資料介紹

數據壓縮技術能減少傳輸所用的時間和存儲空間,在有限的信道容量內傳輸更多的有用信息,有助于降低功率和帶寬要求,改善通信效率。反之,如果不進行數據壓縮,則無論傳輸或存儲都很難實用化[1]。

1 硬件及實現原理

結合本設計的實際情況,由于壓縮算法比較復雜,計算量大,在壓縮數據時必須采用浮點型運算。另一方面,由于處理精度要求高,所以需要選擇浮點型DSP。基于上述考慮,選用TI公司的一款性價比非常高的浮點芯片TMS320C6713。其主頻225MHz,每周期執行8條32bit指令,最高定點運算能力為 1800MIPS,浮點運算能力為1350MFLOPS,32位指令集,而且內部自帶256KB的RAM,4KB程序緩沖器和4KB的數據緩沖器,可以通過外部存儲器接口EMIF(External Memory Inter Faces)擴展SDRAM和Flash[2]。在本設計中,對原始數據按照每2 048B為一組進行壓縮。壓縮的最小單位是2 048B,且壓縮率不固定,對于某組特定數據壓縮后可能比原來的數據還要大。壓縮前后的數據都需要放到DSP的RAM中進行處理,其256KB的RAM不能滿足本設計存儲要求,需要通過EMIF擴展存儲空間。SDRAM選用Micron公司的MT48LC2M32B2。其數據總線為32位,存儲空間為 64Mbit。工作電壓為3.3V,內部流水線結構保證了芯片的高速運行。SDRAM可以與EMIF無縫接口。EMIF的CE0連入片選引腳CS,將 SDRAM映射到CE0地址空間(0x80000000-0x80800000)。Flash是系統在斷電后用來保存程序和初始化數據的存儲器,系統上電時,由引導程序將DSP的應用程序從該存儲器引導到系統的高速存儲器RAM中。本設計用AMD公司生產的1M×8bit/512K×16bit AM29LV800-70 Flash存儲器,其數據寬度為8位、16位可選,采用3.3V供電,訪問時間僅70ns。EMIF的CE1連入片選引腳CE,將Flash映射到CE1 地址空間地址范圍為0x90000000~0x90100000,尋址空間為1MB[3]。

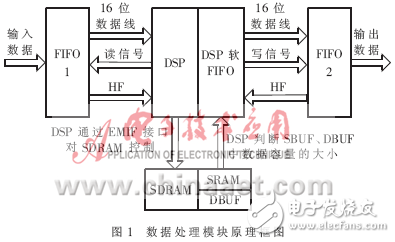

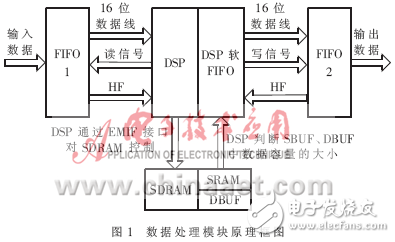

通常在高速數據采集系統中,數據處理速度及數據傳輸速度與前端A/D轉換器的采集速度不一致。為了協調它們之間工作,可以加入數據存儲器或者數據緩存器(FIFO)進行數據緩沖,使得前端數據采集和后級數據處理能夠協調工作。在本設計中,前端的采樣速度為27Kb/s;且數據流是連續的。DSP的主頻為 225MHz,經過鎖向環分頻后其讀取數據的速度為38Mb/s左右。DSP若一直等待讀數據,會大大降低其數據的處理能力。DSP讀入數據后,馬上對數據進行壓縮,壓縮后把相應的數據寫到輸出FIFO。同理,發送模塊的處理速度為18Kb/s。DSP寫輸出FIFO的速度也在38Mb/s左右。顯然,前端與DSP及DSP與發送模塊的處理速度不是一個數量級。所以在前端與DSP之間,DSP與發送模塊間分別加了兩個FIFO。本設計中FIFO1、 FIFO2均選用IDT72V19160,其存儲空間為128KB,16位并行數據總線,可達到100MHz的操作時鐘。原理框圖如圖1所示。

前端通過16位數據總線將數據寫入到輸入FIFO1中。在程序中通過控制其半滿(HF)信號,即當數據超過32KB時(32768+1), HF信號低電平有效,就會觸發一次中斷通知可編程邏輯和DSP,DSP進入中斷后把2KB的數據從輸入FIFO1中讀入到SBUF所指向的SDRAM空間中,在進行高速壓縮以后,被壓縮的數據放到DBUF中。SBUF的數據要與DBUF的數據進行比較,若DBUF中存儲數據的容量小于SBUF中的存儲數據的容量,就把DBUF中相應的數據寫到DSP的軟FIFO中,否則,就把SBUF中相應的數據寫到DSP的軟FIFO中。最終,DSP把壓縮后的數據通過其軟FIFO寫入到輸出FIFO2中,等待發送模塊把數據讀走。

在上述過程中,如果DSP沒有等待到中斷信號,則返回繼續等待,直到檢測到中斷信號,才讀取FIFO1中的數據。在DSP對SBUF中的數據幀壓縮的同時,前端以固定的采樣率對模擬信號進行采樣,并寫入到輸入FIFO1中。同時DSP把壓縮后的數據按每次小于2KB左右的速度寫入到輸出FIFO2。當輸出FIFO2半滿,發送模塊控制器會把其HF信號通過GPIO口指向DSP。本設計中用GP10實現相應的操作。DSP的GPIO口可以設為輸入引腳,在中斷向量表中定義后,其本身可以當作中斷使用。這樣DSP可以把采集到的實時數據源源不斷地寫入到FIFO2。整個信號處理模塊的不同子模塊都處于并行工作狀態,較好地實現了數據的實時壓縮,提高了壓縮效率。

設備上電DSP復位后,由其內部固化的自引導程序(BOOT)將存于Flash存儲器的程序和數據搬移至內部 RAM中,然后DSP即可以開始讀取壓縮算法的應用程序,繼續運行。DSP的工作流程圖如圖2所示。上電以后,首先初始化DSP的CSL函數庫,然后初始化PLL、GPIO及關中斷寄存器,等待中斷信號的來臨。

1 硬件及實現原理

結合本設計的實際情況,由于壓縮算法比較復雜,計算量大,在壓縮數據時必須采用浮點型運算。另一方面,由于處理精度要求高,所以需要選擇浮點型DSP。基于上述考慮,選用TI公司的一款性價比非常高的浮點芯片TMS320C6713。其主頻225MHz,每周期執行8條32bit指令,最高定點運算能力為 1800MIPS,浮點運算能力為1350MFLOPS,32位指令集,而且內部自帶256KB的RAM,4KB程序緩沖器和4KB的數據緩沖器,可以通過外部存儲器接口EMIF(External Memory Inter Faces)擴展SDRAM和Flash[2]。在本設計中,對原始數據按照每2 048B為一組進行壓縮。壓縮的最小單位是2 048B,且壓縮率不固定,對于某組特定數據壓縮后可能比原來的數據還要大。壓縮前后的數據都需要放到DSP的RAM中進行處理,其256KB的RAM不能滿足本設計存儲要求,需要通過EMIF擴展存儲空間。SDRAM選用Micron公司的MT48LC2M32B2。其數據總線為32位,存儲空間為 64Mbit。工作電壓為3.3V,內部流水線結構保證了芯片的高速運行。SDRAM可以與EMIF無縫接口。EMIF的CE0連入片選引腳CS,將 SDRAM映射到CE0地址空間(0x80000000-0x80800000)。Flash是系統在斷電后用來保存程序和初始化數據的存儲器,系統上電時,由引導程序將DSP的應用程序從該存儲器引導到系統的高速存儲器RAM中。本設計用AMD公司生產的1M×8bit/512K×16bit AM29LV800-70 Flash存儲器,其數據寬度為8位、16位可選,采用3.3V供電,訪問時間僅70ns。EMIF的CE1連入片選引腳CE,將Flash映射到CE1 地址空間地址范圍為0x90000000~0x90100000,尋址空間為1MB[3]。

通常在高速數據采集系統中,數據處理速度及數據傳輸速度與前端A/D轉換器的采集速度不一致。為了協調它們之間工作,可以加入數據存儲器或者數據緩存器(FIFO)進行數據緩沖,使得前端數據采集和后級數據處理能夠協調工作。在本設計中,前端的采樣速度為27Kb/s;且數據流是連續的。DSP的主頻為 225MHz,經過鎖向環分頻后其讀取數據的速度為38Mb/s左右。DSP若一直等待讀數據,會大大降低其數據的處理能力。DSP讀入數據后,馬上對數據進行壓縮,壓縮后把相應的數據寫到輸出FIFO。同理,發送模塊的處理速度為18Kb/s。DSP寫輸出FIFO的速度也在38Mb/s左右。顯然,前端與DSP及DSP與發送模塊的處理速度不是一個數量級。所以在前端與DSP之間,DSP與發送模塊間分別加了兩個FIFO。本設計中FIFO1、 FIFO2均選用IDT72V19160,其存儲空間為128KB,16位并行數據總線,可達到100MHz的操作時鐘。原理框圖如圖1所示。

前端通過16位數據總線將數據寫入到輸入FIFO1中。在程序中通過控制其半滿(HF)信號,即當數據超過32KB時(32768+1), HF信號低電平有效,就會觸發一次中斷通知可編程邏輯和DSP,DSP進入中斷后把2KB的數據從輸入FIFO1中讀入到SBUF所指向的SDRAM空間中,在進行高速壓縮以后,被壓縮的數據放到DBUF中。SBUF的數據要與DBUF的數據進行比較,若DBUF中存儲數據的容量小于SBUF中的存儲數據的容量,就把DBUF中相應的數據寫到DSP的軟FIFO中,否則,就把SBUF中相應的數據寫到DSP的軟FIFO中。最終,DSP把壓縮后的數據通過其軟FIFO寫入到輸出FIFO2中,等待發送模塊把數據讀走。

在上述過程中,如果DSP沒有等待到中斷信號,則返回繼續等待,直到檢測到中斷信號,才讀取FIFO1中的數據。在DSP對SBUF中的數據幀壓縮的同時,前端以固定的采樣率對模擬信號進行采樣,并寫入到輸入FIFO1中。同時DSP把壓縮后的數據按每次小于2KB左右的速度寫入到輸出FIFO2。當輸出FIFO2半滿,發送模塊控制器會把其HF信號通過GPIO口指向DSP。本設計中用GP10實現相應的操作。DSP的GPIO口可以設為輸入引腳,在中斷向量表中定義后,其本身可以當作中斷使用。這樣DSP可以把采集到的實時數據源源不斷地寫入到FIFO2。整個信號處理模塊的不同子模塊都處于并行工作狀態,較好地實現了數據的實時壓縮,提高了壓縮效率。

設備上電DSP復位后,由其內部固化的自引導程序(BOOT)將存于Flash存儲器的程序和數據搬移至內部 RAM中,然后DSP即可以開始讀取壓縮算法的應用程序,繼續運行。DSP的工作流程圖如圖2所示。上電以后,首先初始化DSP的CSL函數庫,然后初始化PLL、GPIO及關中斷寄存器,等待中斷信號的來臨。

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- 數據無損壓縮 0次下載

- 實時數據分析器用戶手冊

- 嵌入式系統數據無損壓縮

- 基于強連接網絡圖的無損壓縮算法綜述 6次下載

- 如何使用FPGA實現機載圖像無損和近無損壓縮方案 3次下載

- 基于改進SPIHT的圖像無損壓縮算法研究_武永紅 1次下載

- 機載圖像無損近無損壓縮方案及其FPGA實現 5次下載

- 基于實時數據庫的數據壓縮算法 20次下載

- 基于FPGA的數據實時無損壓縮系統 63次下載

- 同聲數據補償方法應用于無損音頻格式

- 常用數據無損壓縮算法分析 0次下載

- 基于搜索最優雙預測波段的超光譜遙感圖像無損壓縮

- 基于聚類的高光譜圖像無損壓縮

- 基于DSP的實時無損壓縮算法設計與實現

- 基于實時數據交換技術的數據通信

- 基于門控線性網絡(GLN)的高壓縮比無損醫學圖像壓縮算法 473次閱讀

- 物聯網中的PLC如何實現實時數據采集 816次閱讀

- 采用海思Hi3512處理器和GPS數據無損壓縮技術實現車載移動終端設計 2624次閱讀

- 實時數據體系建設的總體方案的三部分 6598次閱讀

- 怎么鑒別MP3的無損音樂格式,你會了? 1.3w次閱讀

- 根據電網特點對實時數據庫的測試要點的幾個方面 1745次閱讀

- 數據壓縮算法計算步驟及過程 1.1w次閱讀

- 數據壓縮的重要性 1.4w次閱讀

- 無損壓縮算法有哪些 1.8w次閱讀

- 有損壓縮和無損壓縮的區別 5w次閱讀

- 音頻壓縮技術標準 1.7w次閱讀

- 音頻壓縮技術原理 2.4w次閱讀

- 基于FPGA的LZO實時無損壓縮的硬件設計 3103次閱讀

- 一種高速實時數據采集系統的設計方案 4671次閱讀

- DSP+CPLD空間瞬態光輻射信號實時探測系統 1418次閱讀

下載排行

本周

- 1電子電路原理第七版PDF電子教材免費下載

- 0.00 MB | 1489次下載 | 免費

- 2單片機典型實例介紹

- 18.19 MB | 91次下載 | 1 積分

- 3S7-200PLC編程實例詳細資料

- 1.17 MB | 27次下載 | 1 積分

- 4筆記本電腦主板的元件識別和講解說明

- 4.28 MB | 18次下載 | 4 積分

- 5開關電源原理及各功能電路詳解

- 0.38 MB | 9次下載 | 免費

- 6基于AT89C2051/4051單片機編程器的實驗

- 0.11 MB | 4次下載 | 免費

- 7基于單片機和 SG3525的程控開關電源設計

- 0.23 MB | 3次下載 | 免費

- 8基于單片機的紅外風扇遙控

- 0.23 MB | 3次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費

- 2PADS 9.0 2009最新版 -下載

- 0.00 MB | 66304次下載 | 免費

- 3protel99下載protel99軟件下載(中文版)

- 0.00 MB | 51209次下載 | 免費

- 4LabView 8.0 專業版下載 (3CD完整版)

- 0.00 MB | 51043次下載 | 免費

- 5555集成電路應用800例(新編版)

- 0.00 MB | 33562次下載 | 免費

- 6接口電路圖大全

- 未知 | 30319次下載 | 免費

- 7Multisim 10下載Multisim 10 中文版

- 0.00 MB | 28588次下載 | 免費

- 8開關電源設計實例指南

- 未知 | 21539次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935053次下載 | 免費

- 2protel99se軟件下載(可英文版轉中文版)

- 78.1 MB | 537791次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233045次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191183次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183277次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138039次下載 | 免費

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論