資料介紹

引言

HDLC(高級數(shù)據(jù)鏈路控制)廣泛應用于數(shù)據(jù)通信領(lǐng)域,是確保數(shù)據(jù)信息可靠互通的重要技術(shù)。實施HDLC的一般方法通常是采用ASIC器件或軟件編程等。

HDLC的ASIC芯片使用簡易,功能針對性強,性能可靠,適合應用于特定用途的大批量產(chǎn)品中。但由于HDLC標準的文本較多,ASIC芯片出于專用性的目的難以通用于不同版本,缺乏應用靈活性。有的芯片公司還有自己的標準,對HDLC的CRC(循環(huán)冗余碼校驗)序列生成多項式等有不同的規(guī)定。專用于HDLC的ASIC芯片其片內(nèi)數(shù)據(jù)存儲器容量有限,通常只有不多字節(jié)的FIFO(先進先出存儲器)可用。對于某些應用來說,當需要擴大數(shù)據(jù)緩存的容量時,只能對ASIC再外接存儲器或其他電路,ASIC的簡單易用性就被抵銷掉了。HDLC的軟件編程方法功能靈活,通過修改程序就可以適用于不同的HDLC應用。但程序運行占用處理器資源多,執(zhí)行速度慢,對信號的時延和同步性不易預測。純軟件HDLC一般只能用于個別路數(shù)的低速信號處理。

FPGA采用硬件技術(shù)處理信號,又可以通過軟件反復編程使用,能夠兼顧速度和靈活性,并能并行處理多路信號,實時性能能夠預測和仿真。

DSP采用軟件技術(shù)處理信號,也可以反復編程使用。DSP、FPGA芯片雖成本略微高于ASIC芯片,但具有貨源暢通、可多次編程使用等優(yōu)點。在中小批量通信產(chǎn)品的設(shè)計生產(chǎn)中,用FPGA和DSP實現(xiàn)HDLC功能是一種值得采用的方法。

HDLC的幀結(jié)構(gòu)和CRC校驗

為了使FPGA的設(shè)計能夠?qū)崿F(xiàn)HDLC的基本功能并能按照各項標準的規(guī)定靈活采用不同的CRC校驗算法,首先看一下HDLC基本的幀結(jié)構(gòu)形式。

HDLC是面向比特的鏈路控制規(guī)程,其鏈路監(jiān)控功能通過一定的比特組合所表示的命令和響應來實現(xiàn),這些監(jiān)控比特和信息比特一起以幀的形式傳送。以下是ISO/IEC3309標準規(guī)定的HDLC的基本幀結(jié)構(gòu)。

其他的HDLC標準也有類似的幀結(jié)構(gòu)。每幀的起始和結(jié)束以“7E”(01111110)做標志,兩個“7E”之間為數(shù)據(jù)段(含地址數(shù)據(jù)、控制數(shù)據(jù)、信息數(shù)據(jù))和幀校驗序列。幀校驗采用CRC算法,對除了插入的“零”以外的所有數(shù)據(jù)進行校驗。為了避免將數(shù)據(jù)中的“7E”誤為標志,在發(fā)送端和接收端要相應地對數(shù)據(jù)流和幀校驗序列進行“插零”及“刪零”操作。

用FPGA+DSP實現(xiàn)HDLC功能

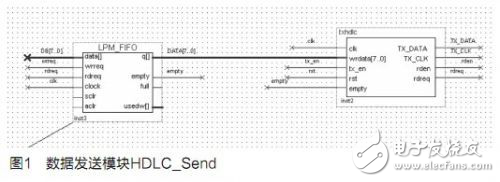

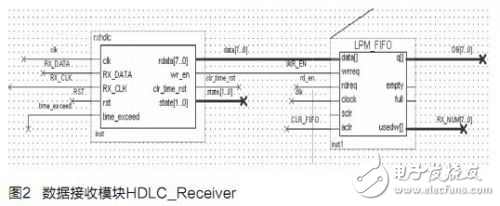

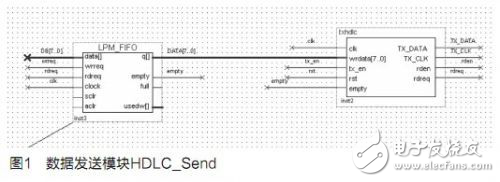

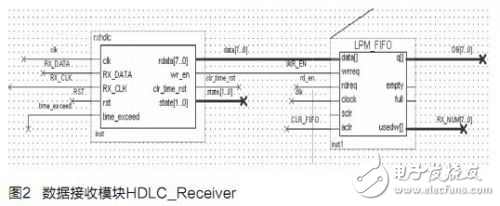

對FPGA器件進行功能設(shè)計一般采用的是“ToptoDown”(“從頂?shù)降住保┑姆椒ǎ嗉锤鶕?jù)要求的功能先設(shè)計出頂層的原理框圖,該圖通常由若干個功能模塊組成。再把各個模塊細化為子模塊,對較復雜的設(shè)計還可把各子模塊分成一層層的下級子模塊,各層的功能可以用硬件描述語言或電路圖來實現(xiàn)。

HDLC(高級數(shù)據(jù)鏈路控制)廣泛應用于數(shù)據(jù)通信領(lǐng)域,是確保數(shù)據(jù)信息可靠互通的重要技術(shù)。實施HDLC的一般方法通常是采用ASIC器件或軟件編程等。

HDLC的ASIC芯片使用簡易,功能針對性強,性能可靠,適合應用于特定用途的大批量產(chǎn)品中。但由于HDLC標準的文本較多,ASIC芯片出于專用性的目的難以通用于不同版本,缺乏應用靈活性。有的芯片公司還有自己的標準,對HDLC的CRC(循環(huán)冗余碼校驗)序列生成多項式等有不同的規(guī)定。專用于HDLC的ASIC芯片其片內(nèi)數(shù)據(jù)存儲器容量有限,通常只有不多字節(jié)的FIFO(先進先出存儲器)可用。對于某些應用來說,當需要擴大數(shù)據(jù)緩存的容量時,只能對ASIC再外接存儲器或其他電路,ASIC的簡單易用性就被抵銷掉了。HDLC的軟件編程方法功能靈活,通過修改程序就可以適用于不同的HDLC應用。但程序運行占用處理器資源多,執(zhí)行速度慢,對信號的時延和同步性不易預測。純軟件HDLC一般只能用于個別路數(shù)的低速信號處理。

FPGA采用硬件技術(shù)處理信號,又可以通過軟件反復編程使用,能夠兼顧速度和靈活性,并能并行處理多路信號,實時性能能夠預測和仿真。

DSP采用軟件技術(shù)處理信號,也可以反復編程使用。DSP、FPGA芯片雖成本略微高于ASIC芯片,但具有貨源暢通、可多次編程使用等優(yōu)點。在中小批量通信產(chǎn)品的設(shè)計生產(chǎn)中,用FPGA和DSP實現(xiàn)HDLC功能是一種值得采用的方法。

HDLC的幀結(jié)構(gòu)和CRC校驗

為了使FPGA的設(shè)計能夠?qū)崿F(xiàn)HDLC的基本功能并能按照各項標準的規(guī)定靈活采用不同的CRC校驗算法,首先看一下HDLC基本的幀結(jié)構(gòu)形式。

HDLC是面向比特的鏈路控制規(guī)程,其鏈路監(jiān)控功能通過一定的比特組合所表示的命令和響應來實現(xiàn),這些監(jiān)控比特和信息比特一起以幀的形式傳送。以下是ISO/IEC3309標準規(guī)定的HDLC的基本幀結(jié)構(gòu)。

其他的HDLC標準也有類似的幀結(jié)構(gòu)。每幀的起始和結(jié)束以“7E”(01111110)做標志,兩個“7E”之間為數(shù)據(jù)段(含地址數(shù)據(jù)、控制數(shù)據(jù)、信息數(shù)據(jù))和幀校驗序列。幀校驗采用CRC算法,對除了插入的“零”以外的所有數(shù)據(jù)進行校驗。為了避免將數(shù)據(jù)中的“7E”誤為標志,在發(fā)送端和接收端要相應地對數(shù)據(jù)流和幀校驗序列進行“插零”及“刪零”操作。

用FPGA+DSP實現(xiàn)HDLC功能

對FPGA器件進行功能設(shè)計一般采用的是“ToptoDown”(“從頂?shù)降住保┑姆椒ǎ嗉锤鶕?jù)要求的功能先設(shè)計出頂層的原理框圖,該圖通常由若干個功能模塊組成。再把各個模塊細化為子模塊,對較復雜的設(shè)計還可把各子模塊分成一層層的下級子模塊,各層的功能可以用硬件描述語言或電路圖來實現(xiàn)。

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- 基于FPGA和DSP的機載圖形顯示系統(tǒng) 36次下載

- 如何使用FPGA和DSP實現(xiàn)數(shù)字視頻消像旋系統(tǒng)的設(shè)計 10次下載

- 如何使用FPGA實現(xiàn)HDLC協(xié)議控制器 15次下載

- 基于DSP與FPGA實現(xiàn)的HDLC系統(tǒng) 1次下載

- 基于DSP的FPGA配置方法研究與實現(xiàn) 36次下載

- DSP和FPGA的HDLC協(xié)議通訊電路設(shè)計 7次下載

- 基于FPGA和DSP的圖像多功能卡的設(shè)計與實現(xiàn) 28次下載

- HDLC協(xié)議RS485總線控制器的FPGA實現(xiàn) 100次下載

- 基于FPGA的HDLC協(xié)議控制器 93次下載

- 融合DSP設(shè)計與FPGA硬件實現(xiàn) 225次下載

- 基于DSP和FPGA的運動控制卡的設(shè)計與實現(xiàn) 105次下載

- 基于DSP和FPGA的HDLC協(xié)議通訊電路設(shè)計 98次下載

- WTB網(wǎng)絡(luò)HDLC在FPGA中的實現(xiàn)

- 基于FPGA的多通道HDLC通信系統(tǒng)設(shè)計與實現(xiàn)

- FPGA實現(xiàn)DSP應用

- MCU、DSP和FPGA的區(qū)別 4091次閱讀

- 基于DSP+FPGA+ARM的架構(gòu)實現(xiàn)高速多路數(shù)據(jù)傳輸系統(tǒng)的設(shè)計 5037次閱讀

- 基于FPGA和DSP技術(shù)實現(xiàn)3D視頻的系統(tǒng)設(shè)計 1721次閱讀

- 基于DSP+FPGA實現(xiàn)的TL6678F-EasyEVM開發(fā)板的介紹 3834次閱讀

- 基于FPGA的自動化DSP開發(fā)流程 4181次閱讀

- 怎么利用FPGA器件保護DSP網(wǎng)絡(luò)設(shè)計避免入侵? 954次閱讀

- 如何利用FPGA技術(shù)來解決DSP的設(shè)計難題? 1951次閱讀

- FPGA會取代DSP嗎?FPGA與DSP區(qū)別介紹 3.6w次閱讀

- 基于FPGA+DSP的視頻控制的智能交通燈設(shè)計 2043次閱讀

- 一種基于DSP+FPGA視頻圖像采集處理系統(tǒng)的設(shè)計與實現(xiàn) 4763次閱讀

- 基于DSP+FPGA的實時圖像去霧增強系統(tǒng)設(shè)計 3636次閱讀

- 基于FPGA和DSP的噴油器霧化粒徑測量系統(tǒng)的設(shè)計 1918次閱讀

- 一文了解FPGA與DSP的區(qū)別、特點及用途 2.9w次閱讀

- 基于EMIF接口的DSP控制系統(tǒng)設(shè)計 5799次閱讀

- FPGA+DSP的高速通信接口設(shè)計與實現(xiàn) 7623次閱讀

下載排行

本周

- 1電子電路原理第七版PDF電子教材免費下載

- 0.00 MB | 1489次下載 | 免費

- 2單片機典型實例介紹

- 18.19 MB | 91次下載 | 1 積分

- 3S7-200PLC編程實例詳細資料

- 1.17 MB | 27次下載 | 1 積分

- 4筆記本電腦主板的元件識別和講解說明

- 4.28 MB | 18次下載 | 4 積分

- 5開關(guān)電源原理及各功能電路詳解

- 0.38 MB | 9次下載 | 免費

- 6基于AT89C2051/4051單片機編程器的實驗

- 0.11 MB | 4次下載 | 免費

- 7基于單片機和 SG3525的程控開關(guān)電源設(shè)計

- 0.23 MB | 3次下載 | 免費

- 8基于單片機的紅外風扇遙控

- 0.23 MB | 3次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費

- 2PADS 9.0 2009最新版 -下載

- 0.00 MB | 66304次下載 | 免費

- 3protel99下載protel99軟件下載(中文版)

- 0.00 MB | 51209次下載 | 免費

- 4LabView 8.0 專業(yè)版下載 (3CD完整版)

- 0.00 MB | 51043次下載 | 免費

- 5555集成電路應用800例(新編版)

- 0.00 MB | 33562次下載 | 免費

- 6接口電路圖大全

- 未知 | 30319次下載 | 免費

- 7Multisim 10下載Multisim 10 中文版

- 0.00 MB | 28588次下載 | 免費

- 8開關(guān)電源設(shè)計實例指南

- 未知 | 21539次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935053次下載 | 免費

- 2protel99se軟件下載(可英文版轉(zhuǎn)中文版)

- 78.1 MB | 537791次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233045次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191183次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183277次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138039次下載 | 免費

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問

提問  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評論