資料介紹

摘要:高速中頻采樣信號處理平臺在實際應用中有很大的前景,提出采用FPGA+DSP的處理結構,結合高性能A/D和D/A處理芯片,設計了一個通用處理平臺,并對其主要性能進行了測試。實驗與實際應用表明,該系統具有很強的數據處理能力和很好的穩定性。

關鍵詞:高速中頻;信號處理;FPGA;DSP

0 引言

現代社會正向數字化、信息化方向高速發展,在這一過程中,往往需要高速信號的實時性數字化處理。例如,隨著科技的進步,現代雷達等應用信號的數字化處理上有了長足的發展,但也帶來了新的問題,這些應用的數字信號處理具有海量運行需求的應用背景,如巡航導彈末制導雷達地形匹配、合成孔徑雷達的成像處理、相控陣雷達的時空二維濾波處理等領域。目前,單片DSP難以勝任許多信號處理系統的要求。而常見的解決方案也是高速A/D采樣與信號處理功能是在多塊不同的板卡上實現,這給實際應用帶來很多不便。

鑒于上述現有技術所存在的問題,本設計平臺的目的是:

(1)實現高速中頻信號(如雷達信號)的數字化處理并進行實時傳輸數據或進行數據的實時計算,并能通過輸出電路進行結果顯示;

(2)自定義控制總線可以實現對高速中頻信號處理板進行靈活控制,具有較強的可配置性和豐富的靈活性;

(3)高速A/D采樣與D/A回放及數據處理單元集成在一塊板上,在集成度高的同時也降低了高速信號在傳輸過程中出現差錯的概率。

1 平臺設計方案

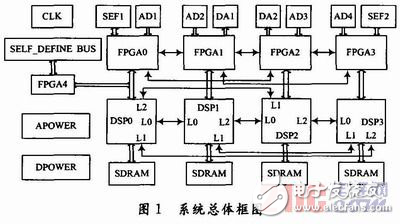

高速中頻采樣信號處理平臺由主控制電路、高速A/D與D/A電路、信號處理單元電路、光纖通道電路、時鐘管理電路、存儲單元和外部接口電路組成,其總體框圖如圖1所示。

在實際應用過程中,四路A/D通道可以接收不同的信號源的信號,D/A通路可以對外進行數據顯示等多種功能,時鐘管理電路管理內外時鐘的使用及對板上系統供給工作時鐘,兩路光纖通道可以與其他高速設備相連接,自定義總線可以與CPU或主控制器相連接對平臺進行有效靈活的控制。

1.1 高速A/D與D/A設計

四路高速A/D采樣通道采用兩片NS公司的ADC081000實現,每片有兩個A/D通道,相比多片A/D器件的通道間相位恒定設計是一個難點而言,單片A/D器件可以更容易實現兩路通道間的相位恒定。ADC081000是一款高性能的A/D采集芯片,單通道8 b采樣頻率為1 GHz。本平臺中A/D通道間采樣數據的相位恒定是利用采樣時鐘相位間的恒定來實現的。在設計時,使時鐘芯片到兩片A/D器件間的時鐘線等長,兩片A /D器件到FPGA間的時鐘線與數據線也分別等長,并且還利用一片FPGA設計了對兩片A/D器件的軟啟動控制,這就更保證了四路通道間采樣時鐘的相位恒定。

兩路高速D/A通道采用兩片AD公司的AD9736實現,AD9736單通道14 b,采樣頻率可達1 200 MSPS。兩路高速D/A通路也利用一片FPGA作控制,實現通道間相位差的恒定。

1.2 信號處理單元設計

信號處理單元包括FPGA和DSP兩大部分。

FPGA部分主要由四片Virtex-4 SX55組成,四片FPGA間實現有串行連接和相隔間的連接。FPGA電路主要是實現對高速A/D采集數據的預處理和高速D/A回放數據處理,并且控制高速A/D電路采樣時鐘的相位恒定與高速D/A電路采樣時鐘的相位恒定,同時也根據需要與相應的DSP進行數據交換或傳遞。FPGA電路上連接的光接口電路也可以實現與其他系統進行高速、實時的數據交換。

A/D采樣之后的數字信號速率非常高,要從這些高速信號中得到有用的基帶信號,需要有效地對其進行數字下變頻、抽取、濾波等處理,這些功能都可以通過FPGA來實現。FPGA具有較高的處理速度和較高的穩定性,同時又具有設計靈活、易于修改和維護的優點,可以適應不同系統的要求,提高了系統的適用性及可擴展性。

DSP電路是本平臺信號處理的核心,完成大部分的數據處理工作,由四片ADSP TS201組成,四片DSP間實現了兩兩間的Link口互連,構成了分布式并行系統,可以把復雜的算法分割成小的任務給各處理器完成,從而減少任務的執行時間。

根據設計需要,平臺數據的傳輸量很大,多DSP之間的數據傳輸速度尤為重要,采用Link口來傳輸數據,可以在不增加輔助電路的前提下,DSP間的直接互聯。而且,基于Link口的數據傳輸采用專門的數據通道,不占有系統總線資源,消除了傳輸過程中的總線仲裁,減少了網絡延遲帶來的不確定因素。四片DSP間Link口的傳遞數據能力高達600 MB/s。

DSP主要是通過軟件設計來實現數字基帶信號處理以及比特流控制、編碼解碼等高速的數據交換和處理功能。對DSP開發的軟件工具是ADI公司的VisualDSF++4.0,它是TigerSHARC系列DSP的集成開發環境,支持匯編語言、C語言、C++等開發語言,能讓程序員使用這些工具編寫出相對于特定DSP的高性能應用程序,發揮強大的處理能力。在本平臺中,每片DSP的地位都是對等的,能夠根據不同的要求,硬件結構不用改變,只須在DSP的軟件算法中稍加改動,系統就能實現新的功能。

關鍵詞:高速中頻;信號處理;FPGA;DSP

0 引言

現代社會正向數字化、信息化方向高速發展,在這一過程中,往往需要高速信號的實時性數字化處理。例如,隨著科技的進步,現代雷達等應用信號的數字化處理上有了長足的發展,但也帶來了新的問題,這些應用的數字信號處理具有海量運行需求的應用背景,如巡航導彈末制導雷達地形匹配、合成孔徑雷達的成像處理、相控陣雷達的時空二維濾波處理等領域。目前,單片DSP難以勝任許多信號處理系統的要求。而常見的解決方案也是高速A/D采樣與信號處理功能是在多塊不同的板卡上實現,這給實際應用帶來很多不便。

鑒于上述現有技術所存在的問題,本設計平臺的目的是:

(1)實現高速中頻信號(如雷達信號)的數字化處理并進行實時傳輸數據或進行數據的實時計算,并能通過輸出電路進行結果顯示;

(2)自定義控制總線可以實現對高速中頻信號處理板進行靈活控制,具有較強的可配置性和豐富的靈活性;

(3)高速A/D采樣與D/A回放及數據處理單元集成在一塊板上,在集成度高的同時也降低了高速信號在傳輸過程中出現差錯的概率。

1 平臺設計方案

高速中頻采樣信號處理平臺由主控制電路、高速A/D與D/A電路、信號處理單元電路、光纖通道電路、時鐘管理電路、存儲單元和外部接口電路組成,其總體框圖如圖1所示。

在實際應用過程中,四路A/D通道可以接收不同的信號源的信號,D/A通路可以對外進行數據顯示等多種功能,時鐘管理電路管理內外時鐘的使用及對板上系統供給工作時鐘,兩路光纖通道可以與其他高速設備相連接,自定義總線可以與CPU或主控制器相連接對平臺進行有效靈活的控制。

1.1 高速A/D與D/A設計

四路高速A/D采樣通道采用兩片NS公司的ADC081000實現,每片有兩個A/D通道,相比多片A/D器件的通道間相位恒定設計是一個難點而言,單片A/D器件可以更容易實現兩路通道間的相位恒定。ADC081000是一款高性能的A/D采集芯片,單通道8 b采樣頻率為1 GHz。本平臺中A/D通道間采樣數據的相位恒定是利用采樣時鐘相位間的恒定來實現的。在設計時,使時鐘芯片到兩片A/D器件間的時鐘線等長,兩片A /D器件到FPGA間的時鐘線與數據線也分別等長,并且還利用一片FPGA設計了對兩片A/D器件的軟啟動控制,這就更保證了四路通道間采樣時鐘的相位恒定。

兩路高速D/A通道采用兩片AD公司的AD9736實現,AD9736單通道14 b,采樣頻率可達1 200 MSPS。兩路高速D/A通路也利用一片FPGA作控制,實現通道間相位差的恒定。

1.2 信號處理單元設計

信號處理單元包括FPGA和DSP兩大部分。

FPGA部分主要由四片Virtex-4 SX55組成,四片FPGA間實現有串行連接和相隔間的連接。FPGA電路主要是實現對高速A/D采集數據的預處理和高速D/A回放數據處理,并且控制高速A/D電路采樣時鐘的相位恒定與高速D/A電路采樣時鐘的相位恒定,同時也根據需要與相應的DSP進行數據交換或傳遞。FPGA電路上連接的光接口電路也可以實現與其他系統進行高速、實時的數據交換。

A/D采樣之后的數字信號速率非常高,要從這些高速信號中得到有用的基帶信號,需要有效地對其進行數字下變頻、抽取、濾波等處理,這些功能都可以通過FPGA來實現。FPGA具有較高的處理速度和較高的穩定性,同時又具有設計靈活、易于修改和維護的優點,可以適應不同系統的要求,提高了系統的適用性及可擴展性。

DSP電路是本平臺信號處理的核心,完成大部分的數據處理工作,由四片ADSP TS201組成,四片DSP間實現了兩兩間的Link口互連,構成了分布式并行系統,可以把復雜的算法分割成小的任務給各處理器完成,從而減少任務的執行時間。

根據設計需要,平臺數據的傳輸量很大,多DSP之間的數據傳輸速度尤為重要,采用Link口來傳輸數據,可以在不增加輔助電路的前提下,DSP間的直接互聯。而且,基于Link口的數據傳輸采用專門的數據通道,不占有系統總線資源,消除了傳輸過程中的總線仲裁,減少了網絡延遲帶來的不確定因素。四片DSP間Link口的傳遞數據能力高達600 MB/s。

DSP主要是通過軟件設計來實現數字基帶信號處理以及比特流控制、編碼解碼等高速的數據交換和處理功能。對DSP開發的軟件工具是ADI公司的VisualDSF++4.0,它是TigerSHARC系列DSP的集成開發環境,支持匯編語言、C語言、C++等開發語言,能讓程序員使用這些工具編寫出相對于特定DSP的高性能應用程序,發揮強大的處理能力。在本平臺中,每片DSP的地位都是對等的,能夠根據不同的要求,硬件結構不用改變,只須在DSP的軟件算法中稍加改動,系統就能實現新的功能。

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- 中頻接收機硬件平臺的設計方案

- 基于多相濾波的寬帶中頻正交采樣數字零中頻接收方案 3次下載

- 小信號放大電路設計方案匯總 139次下載

- 軟件無線電信號中頻與采樣頻率的選擇方法 8次下載

- 數字信號處理虛擬試驗仿真平臺方案 5次下載

- 軟件無線電中信號中頻與采樣頻率選擇 13次下載

- 基于多相濾波的正交采樣零中頻數字化接收及QPSK高速解調的FPGA實現 11次下載

- 一種WiMax雙下變頻IF采樣接收機設計方案

- 使用DDC控制器設計中頻無線電接收系統的方案說明 10次下載

- 基于matlab GUI的彩色圖像處理技術設計方案資料下載 29次下載

- AD9516高速四通道時間交叉采樣時鐘設計方案分析 7次下載

- LFMCW雷達中頻接收機的設計 65次下載

- 中頻信號與伴音信號處理電路 0次下載

- 中頻信號與伴音信號處理電路

- 中頻采樣多模式數字接收機的設計與實現

- 信號采樣的算法原理是什么 276次閱讀

- 基于FPGA的并行處理實現數字中頻設計 1323次閱讀

- 中頻采樣和IQ采樣的比較分析 3155次閱讀

- 基于軟件無線電和接收信號處理器芯片AD6624實現基帶濾波器的設計 3200次閱讀

- 基于FPGA和高速ADC實現多通道通用信號處理平臺的設計方案 2612次閱讀

- 基于FPGA的并行處理實現數字中頻的設計 3045次閱讀

- 基于FPGA和NAND Flash的便攜式高速信號采集系統的設計方案介紹 2538次閱讀

- 高速信號PCB走線屏蔽設計方案 3184次閱讀

- 基于嵌入式處理器PowerPC7447的設計方案 1128次閱讀

- 過采樣技術在通信信號處理中的應用 5320次閱讀

- 結合FPGA與DSP實現對高速中頻采樣信號處理平臺的設計詳解 2182次閱讀

- 基于PCI總線的微弱信號采集模塊的設計方案 1753次閱讀

- 基于軟件無線電中頻接收系統的設計方案 2833次閱讀

- 基于FPGA的多普勒測振計信號采集與處理系統設計方案 2340次閱讀

- DSP C54X窄帶中頻抽樣的實現 1666次閱讀

下載排行

本周

- 1電子電路原理第七版PDF電子教材免費下載

- 0.00 MB | 1489次下載 | 免費

- 2單片機典型實例介紹

- 18.19 MB | 91次下載 | 1 積分

- 3S7-200PLC編程實例詳細資料

- 1.17 MB | 27次下載 | 1 積分

- 4筆記本電腦主板的元件識別和講解說明

- 4.28 MB | 18次下載 | 4 積分

- 5開關電源原理及各功能電路詳解

- 0.38 MB | 9次下載 | 免費

- 6基于AT89C2051/4051單片機編程器的實驗

- 0.11 MB | 4次下載 | 免費

- 7基于單片機和 SG3525的程控開關電源設計

- 0.23 MB | 3次下載 | 免費

- 8基于單片機的紅外風扇遙控

- 0.23 MB | 3次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費

- 2PADS 9.0 2009最新版 -下載

- 0.00 MB | 66304次下載 | 免費

- 3protel99下載protel99軟件下載(中文版)

- 0.00 MB | 51209次下載 | 免費

- 4LabView 8.0 專業版下載 (3CD完整版)

- 0.00 MB | 51043次下載 | 免費

- 5555集成電路應用800例(新編版)

- 0.00 MB | 33562次下載 | 免費

- 6接口電路圖大全

- 未知 | 30319次下載 | 免費

- 7Multisim 10下載Multisim 10 中文版

- 0.00 MB | 28588次下載 | 免費

- 8開關電源設計實例指南

- 未知 | 21539次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935053次下載 | 免費

- 2protel99se軟件下載(可英文版轉中文版)

- 78.1 MB | 537791次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233045次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191183次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183277次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138039次下載 | 免費

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論