資料介紹

根據最新JESD204B標準構建的轉換器非常適合新型高速FPGA。在采用這些器件進行設計時,應考慮I/O注意事項。

隨著數據轉換器架構和FPGA不斷采用更高級更小型化幾何體,系統設計人員面臨著新的數據接口挑戰。更小工藝幾何體支持更高帶寬轉換器在不斷提高的分辨率及速度下運行,其可實現更高的數據吞吐量。而且,它們還可提供更高的串行/解串(串行解串器)速率,以適應在以前較大幾何體上無法實現的帶寬占用。更小的工藝幾何體也可實現將更多的數據轉換器集成在單個器件中。這些數據轉換器的接口解決方案不僅需要支持高數據速率,而且還必須與復雜FPGA器件兼容,并保證I/O數。

JESD204B接口是一個串行解串器鏈路規范,允許12.5Gbps的最大數據速率傳輸。使用高級工藝(例如65nm或更小)的轉換器支持該最大數據速率,還可提高電源效率。系統設計人員可充分利用該技術相對于低壓差分信號(LVDS)DDR的優點。

幾個開放市場FPGA可為串行收發器提供12.5Gbps乃至更高的數據速率,其中包括賽靈思Virtex-7與Kintex-7系列。盡管FPGA具備這種功能有一定時間了,但轉換器現在才能達到這種性能。該技術可允許多個轉換器的同步,比如常用的轉換器內部多個通道同步,能夠在單個FPGA器件中實現。

為不同應用提供不同選擇

對于數據轉換器的高速串行傳輸,不同的應用有不同的選擇。十多年來,數據轉換器制造商一直選擇LVDS作為主要差分信號技術。盡管有些LVDS應用可使用更高的數據速率,但目前該市場上的轉換器廠商可提供的最大LVDS數據速率仍然為0.8至1 Gbps.LVDS技術一直難以滿足轉換器的帶寬要求。LVDS受TIA/EIA 644A規范控制,這是一項LVDS核心制造商的行業標準。該規范可作為設計人員的最佳實踐指南,提高不同廠商的LVDS發送器及接收器兼容性。同樣,沒有完全遵守LVDS規范的設計人員構建的產品將不符合規范,并會因兼容性問題在市場上遇到更大的挑戰。

像LVDS一樣,JESD204B歸屬Jedec標準組織,其可針對不同制造商之間的互操作性提供電氣及物理需求指導。JESD204B的最大數據速率定義為12.5 Gbps,可實現比實際LVDS吞吐量高出10倍以上的優勢。該性能不僅可為數據轉換器系統降低I/O需求及封裝尺寸,而且還可通過降低靜態功耗顯著節省系統成本。

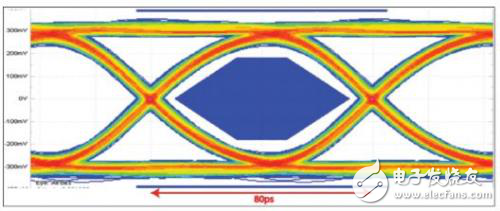

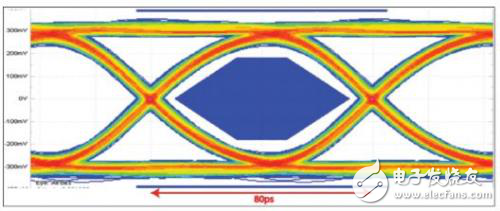

JESD204B規范支持AC耦合,可實現與使用不同供電級的不同技術節點的兼容。例如,28nm及更小的FPGA處理節點是典型的前沿制造工藝技術。轉換器晶體管節點由于需要自定義模擬設計,一般會落后于業界最佳FPGA幾代。相反,LVDS通常采用DC耦合策略,其會提高轉換器與更低功耗電源FPGA的連接難度。共模電壓的不匹配度越大,靜態電流消耗就越高,不會受數據速率影響。為此,JESD204B現已成為高分辨率及高速數據轉換器制造商極具誘惑力的差分信號技術。除了電氣規范以外,JESD204B還具有針對三種物理層的相關眼圖性能要求。性能指標包括定義的眼圖和總體抖動預算。光互聯網絡論壇(OIF)具有成熟的物理層(PHY)規范和眼圖標準,JESD204B接口可利用其實現相同的串行數據速率。JESD204B鏈路可使用OIF低電壓11 Gbit短距離規范(LV-OIF-11G-SR)允許的總體抖動最大值,即單位間隔(UI)的30%.圖1是12.5 Gbps下原始JESD204B眼圖及模板的示圖。模板可在水平軸及垂直軸上提供確定的裕量總數。值得注意的是,12.5Gbps眼圖符合LV-OIF-11G-SR規范,該規范建立在11.1 Gbps的速度基礎之上,比其他的12.5 Gbps數據速率下的規范要求更嚴格。

圖1 12.5Gbps JESD204B眼圖與LV-OIF-11G-SR發送眼圖模板

隨著數據轉換器架構和FPGA不斷采用更高級更小型化幾何體,系統設計人員面臨著新的數據接口挑戰。更小工藝幾何體支持更高帶寬轉換器在不斷提高的分辨率及速度下運行,其可實現更高的數據吞吐量。而且,它們還可提供更高的串行/解串(串行解串器)速率,以適應在以前較大幾何體上無法實現的帶寬占用。更小的工藝幾何體也可實現將更多的數據轉換器集成在單個器件中。這些數據轉換器的接口解決方案不僅需要支持高數據速率,而且還必須與復雜FPGA器件兼容,并保證I/O數。

JESD204B接口是一個串行解串器鏈路規范,允許12.5Gbps的最大數據速率傳輸。使用高級工藝(例如65nm或更小)的轉換器支持該最大數據速率,還可提高電源效率。系統設計人員可充分利用該技術相對于低壓差分信號(LVDS)DDR的優點。

幾個開放市場FPGA可為串行收發器提供12.5Gbps乃至更高的數據速率,其中包括賽靈思Virtex-7與Kintex-7系列。盡管FPGA具備這種功能有一定時間了,但轉換器現在才能達到這種性能。該技術可允許多個轉換器的同步,比如常用的轉換器內部多個通道同步,能夠在單個FPGA器件中實現。

為不同應用提供不同選擇

對于數據轉換器的高速串行傳輸,不同的應用有不同的選擇。十多年來,數據轉換器制造商一直選擇LVDS作為主要差分信號技術。盡管有些LVDS應用可使用更高的數據速率,但目前該市場上的轉換器廠商可提供的最大LVDS數據速率仍然為0.8至1 Gbps.LVDS技術一直難以滿足轉換器的帶寬要求。LVDS受TIA/EIA 644A規范控制,這是一項LVDS核心制造商的行業標準。該規范可作為設計人員的最佳實踐指南,提高不同廠商的LVDS發送器及接收器兼容性。同樣,沒有完全遵守LVDS規范的設計人員構建的產品將不符合規范,并會因兼容性問題在市場上遇到更大的挑戰。

像LVDS一樣,JESD204B歸屬Jedec標準組織,其可針對不同制造商之間的互操作性提供電氣及物理需求指導。JESD204B的最大數據速率定義為12.5 Gbps,可實現比實際LVDS吞吐量高出10倍以上的優勢。該性能不僅可為數據轉換器系統降低I/O需求及封裝尺寸,而且還可通過降低靜態功耗顯著節省系統成本。

JESD204B規范支持AC耦合,可實現與使用不同供電級的不同技術節點的兼容。例如,28nm及更小的FPGA處理節點是典型的前沿制造工藝技術。轉換器晶體管節點由于需要自定義模擬設計,一般會落后于業界最佳FPGA幾代。相反,LVDS通常采用DC耦合策略,其會提高轉換器與更低功耗電源FPGA的連接難度。共模電壓的不匹配度越大,靜態電流消耗就越高,不會受數據速率影響。為此,JESD204B現已成為高分辨率及高速數據轉換器制造商極具誘惑力的差分信號技術。除了電氣規范以外,JESD204B還具有針對三種物理層的相關眼圖性能要求。性能指標包括定義的眼圖和總體抖動預算。光互聯網絡論壇(OIF)具有成熟的物理層(PHY)規范和眼圖標準,JESD204B接口可利用其實現相同的串行數據速率。JESD204B鏈路可使用OIF低電壓11 Gbit短距離規范(LV-OIF-11G-SR)允許的總體抖動最大值,即單位間隔(UI)的30%.圖1是12.5 Gbps下原始JESD204B眼圖及模板的示圖。模板可在水平軸及垂直軸上提供確定的裕量總數。值得注意的是,12.5Gbps眼圖符合LV-OIF-11G-SR規范,該規范建立在11.1 Gbps的速度基礎之上,比其他的12.5 Gbps數據速率下的規范要求更嚴格。

圖1 12.5Gbps JESD204B眼圖與LV-OIF-11G-SR發送眼圖模板

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- JESD204B:適合您嗎?

- 理解JESD204B協議

- 如何構建您的JESD204B 鏈路

- AD9250:14位、170 MSPS/250 MSPS、JESD204B、雙模數轉換器數據表

- AD9694:14位、500 MSPS、JESD204B、四路模數轉換器數據表

- AD9213:12位,6 GSPS/10.25 GSPS,JESD204B,RF模擬到數字轉換器數據Sheet

- AD9697:14位,1300 MSPS,JESD204B,模擬到數字轉換器數據Sheet

- AD9689:14位,2.0 GSPS/2.6 GSPS,JESD204B,雙模擬到數字轉換器數據Sheet

- 驗證ADI轉換器與Xilinx FPGA和JESD204B/C IP的互操作性

- AD9207:12位、6 GSPS、JESD204B/C雙模數轉換器初步數據表

- AD9083:16通道、125 MHz帶寬、JESD204B模數轉換器數據表

- AD9680: 14位、1000 MSPS JESD204B雙通道模數轉換器

- AD9683:14位、170 MSPS/250 MSPS、JESD204B模數轉換器

- 基于JESD204B高速數據傳輸協議 通過DDC魔法乘以ADC的虛擬通道數 39次下載

- JESD204B 串行接口時鐘需要及其實現 44次下載

- 抓住JESD204B接口功能的關鍵問題 876次閱讀

- 采用系統參考模式設計JESD 204B時鐘 1251次閱讀

- 在賽靈思FPGA上快速實現JESD204B 3965次閱讀

- JESD204B學習手冊 2277次閱讀

- JESD204B與串行LVDS接口在寬帶數據轉換器應用中的考慮因素 1266次閱讀

- 在串行LVDS和JESD204B接口之間選擇 1353次閱讀

- 寬帶數據轉換器應用的JESD204B與串行LVDS接口考量 1271次閱讀

- 什么是JESD204B標準為什么需要關注JESD204B接口 1.2w次閱讀

- 為便于實現如此龐大的吞吐量,JESD204B標準應運而生 4484次閱讀

- 針對高速數據轉換器的最新高速JESD204B標準帶來了驗證挑戰 3021次閱讀

- 轉換器JESD204B與LVDS的綜合比較 2281次閱讀

- JESD204B接口及協議狀態過程 3039次閱讀

- JESD204B標準及演進歷程 1.4w次閱讀

- 采用系統參考模式設計JESD204B時鐘 3120次閱讀

- JESD204B SystemC module 設計簡介(一) 3157次閱讀

下載排行

本周

- 1TC358743XBG評估板參考手冊

- 1.36 MB | 330次下載 | 免費

- 2開關電源基礎知識

- 5.73 MB | 6次下載 | 免費

- 3100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

- 4嵌入式linux-聊天程序設計

- 0.60 MB | 3次下載 | 免費

- 5基于FPGA的光纖通信系統的設計與實現

- 0.61 MB | 2次下載 | 免費

- 651單片機窗簾控制器仿真程序

- 1.93 MB | 2次下載 | 免費

- 751單片機大棚環境控制器仿真程序

- 1.10 MB | 2次下載 | 免費

- 8基于51單片機的RGB調色燈程序仿真

- 0.86 MB | 2次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 2555集成電路應用800例(新編版)

- 0.00 MB | 33564次下載 | 免費

- 3接口電路圖大全

- 未知 | 30323次下載 | 免費

- 4開關電源設計實例指南

- 未知 | 21549次下載 | 免費

- 5電氣工程師手冊免費下載(新編第二版pdf電子書)

- 0.00 MB | 15349次下載 | 免費

- 6數字電路基礎pdf(下載)

- 未知 | 13750次下載 | 免費

- 7電子制作實例集錦 下載

- 未知 | 8113次下載 | 免費

- 8《LED驅動電路設計》 溫德爾著

- 0.00 MB | 6653次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935054次下載 | 免費

- 2protel99se軟件下載(可英文版轉中文版)

- 78.1 MB | 537796次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191185次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183279次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138040次下載 | 免費

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論