資料介紹

簡介

SoC設計也面臨著一系列的難題和挑戰,其中出現的最大挑戰之一是硬核IP模塊集成和驗證。隨著技術的擴展,設計并集成IP模塊變得越來越難。在深亞微米技術設計中,IR壓降往往會對功能性造成顯著的影響。

本文介紹了一種新的IR壓降方法,使用這種方法可以帶來非常穩健的內部電網結構。憑借強大的設計技術,該IR壓降方法能帶來出色的硅結果,單端口高速RAM上的8Kx72切口最低電壓可低至0.52V。

存儲器基本架構

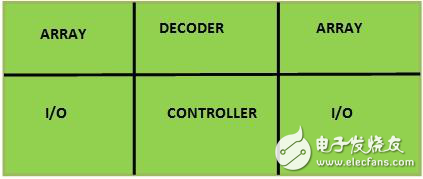

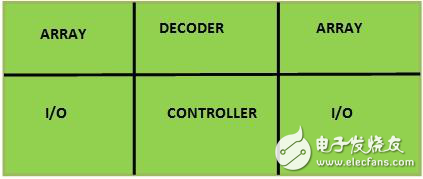

存儲器通常包含四個基本模塊——控制器、解碼器、陣列比特單元和輸入/輸出端。大部分吸收較多電流的大型驅動器都被置于輸入/輸出端、解碼器和控制模塊中。因此,為使各模塊正常運作,我們需要確保每個驅動器有足夠的電壓來保證正常運行。

存儲器基本模塊圖圖1:存儲器基本模塊圖

圖字:陣列;解碼器;陣列;輸入/輸出端;控制器;輸入/輸出端

系統芯片存儲器的連接指南

1.一般方法

一般地,存儲器所有者會以電網的捆扎頻率的形式向設計電源連接的SoC設計人員提供所有電源軌的指導大綱。捆扎頻率定義了給定電源線上的兩個連續金屬帶(一般在頂端金屬)之間的距離。在建造電網時按照捆扎指導大綱操作,可確保幾乎所有驅動器可獲得足夠的工作電壓,實現良好的性能。

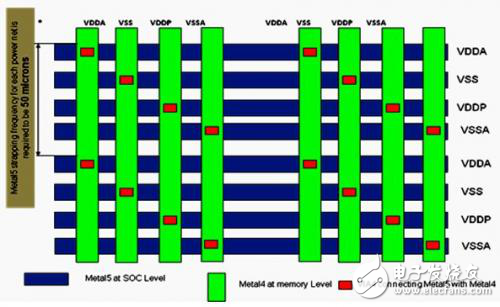

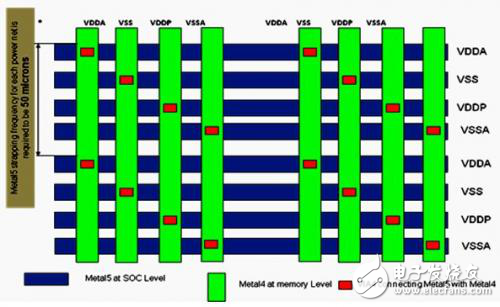

在圖2中,M4的供電軌是垂直的,應與水平的M5相連接。目標存儲器中存在著多個電源域,如VSSA、VDDP、VSS和VDDA等等。

圖2:系統芯片的電源連接結構圖

圖字:要求每個電源網的金屬5捆扎頻率為50微米;系統芯片級金屬5;存儲器級金屬4;VIA4將金屬5與金屬4相連接

將捆扎頻率作為唯一決定因素會導致的問題

假設對于某項特定的技術,規定了一個50um的捆扎頻率。也就是說,每隔50um就應當重復電源線以確保恰當的功能和輸出。在這種情況下,只有一個電源線的驅動(VDD、VSS)是受IR壓降影響最嚴重的,因此這些裝置可能會出現異常行為。

在圖3中,分頻器3和分頻器1只分到一根VDD/VSS電源線,因此可能無法獲得足夠的電壓來確保正常的運作。此處,分頻器2有多個電源線,因而可以正常運行。

在單塊存儲器中,僅僅使用strapping技術也許足以確保正常的運行。然而,對于多組架構的儲存器或較長、較寬的存儲器而言,僅僅使用strapping技術是不足以實現IR壓降要求的。因此,在這種情況下,除了strapping之外,我們還需要使用其他方法來幫助我們實現IR的壓降目標。

SoC設計也面臨著一系列的難題和挑戰,其中出現的最大挑戰之一是硬核IP模塊集成和驗證。隨著技術的擴展,設計并集成IP模塊變得越來越難。在深亞微米技術設計中,IR壓降往往會對功能性造成顯著的影響。

本文介紹了一種新的IR壓降方法,使用這種方法可以帶來非常穩健的內部電網結構。憑借強大的設計技術,該IR壓降方法能帶來出色的硅結果,單端口高速RAM上的8Kx72切口最低電壓可低至0.52V。

存儲器基本架構

存儲器通常包含四個基本模塊——控制器、解碼器、陣列比特單元和輸入/輸出端。大部分吸收較多電流的大型驅動器都被置于輸入/輸出端、解碼器和控制模塊中。因此,為使各模塊正常運作,我們需要確保每個驅動器有足夠的電壓來保證正常運行。

存儲器基本模塊圖圖1:存儲器基本模塊圖

圖字:陣列;解碼器;陣列;輸入/輸出端;控制器;輸入/輸出端

系統芯片存儲器的連接指南

1.一般方法

一般地,存儲器所有者會以電網的捆扎頻率的形式向設計電源連接的SoC設計人員提供所有電源軌的指導大綱。捆扎頻率定義了給定電源線上的兩個連續金屬帶(一般在頂端金屬)之間的距離。在建造電網時按照捆扎指導大綱操作,可確保幾乎所有驅動器可獲得足夠的工作電壓,實現良好的性能。

在圖2中,M4的供電軌是垂直的,應與水平的M5相連接。目標存儲器中存在著多個電源域,如VSSA、VDDP、VSS和VDDA等等。

圖2:系統芯片的電源連接結構圖

圖字:要求每個電源網的金屬5捆扎頻率為50微米;系統芯片級金屬5;存儲器級金屬4;VIA4將金屬5與金屬4相連接

將捆扎頻率作為唯一決定因素會導致的問題

假設對于某項特定的技術,規定了一個50um的捆扎頻率。也就是說,每隔50um就應當重復電源線以確保恰當的功能和輸出。在這種情況下,只有一個電源線的驅動(VDD、VSS)是受IR壓降影響最嚴重的,因此這些裝置可能會出現異常行為。

在圖3中,分頻器3和分頻器1只分到一根VDD/VSS電源線,因此可能無法獲得足夠的電壓來確保正常的運作。此處,分頻器2有多個電源線,因而可以正常運行。

在單塊存儲器中,僅僅使用strapping技術也許足以確保正常的運行。然而,對于多組架構的儲存器或較長、較寬的存儲器而言,僅僅使用strapping技術是不足以實現IR壓降要求的。因此,在這種情況下,除了strapping之外,我們還需要使用其他方法來幫助我們實現IR的壓降目標。

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- PLC系統存儲器與用戶存儲器的功能

- 存儲器介紹

- 基于FPGA塊存儲器的多位反轉容錯 19次下載

- 如何配置存儲器保護單元(MPU) 13次下載

- 半導體存儲器及其測試 35次下載

- Flash存儲器在MCS-51系統中的應用 7次下載

- EEPROM和FLASH存儲器的測試方法詳細說明 33次下載

- 單片機存儲器的工作原理和結構與半導體存儲器的分類說明

- SDRAM存儲器相關資料下載 49次下載

- dsp與外擴展存儲器的連接方法 5次下載

- 淺談SoC存儲器的智能電源連接方法 9次下載

- ARM處理器存儲器及存儲器映射I/O 2次下載

- 基于SOC的高性能存儲器控制器設計 0次下載

- 基于March算法的存儲器測試控制器設計

- 簡單有效的存儲器后備電源

- 季豐對存儲器芯片的失效分析方法步驟 185次閱讀

- 內存儲器與外存儲器的主要區別 2549次閱讀

- 隨機訪問存儲器(RAM)和只讀存儲器(ROM)的區別 1579次閱讀

- PLC系統的存儲器分類介紹 5843次閱讀

- 汽車SoC嵌入式存儲器的優化診斷策略 701次閱讀

- MCP存儲器以及MCP存儲器的應用介紹 4590次閱讀

- 半導體存儲器有哪些類型 1.5w次閱讀

- 只讀存儲器有哪些類型及相變存儲器的詳細介紹 7790次閱讀

- 寄存器和存儲器的區別 1.4w次閱讀

- 計算機的存儲器主要作用_計算機的存儲器的分類介紹 1.1w次閱讀

- 多媒體應用的數據存儲器的各種分配方法 1783次閱讀

- flash存儲器的讀寫原理及次數 2.1w次閱讀

- FinFET存儲器的設計挑戰以及測試和修復方法 2963次閱讀

- 嵌入式存儲器的設計方法和策略 1790次閱讀

- μPSD中存儲器系統的配置 1050次閱讀

下載排行

本周

- 1TC358743XBG評估板參考手冊

- 1.36 MB | 330次下載 | 免費

- 2開關電源基礎知識

- 5.73 MB | 6次下載 | 免費

- 3100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

- 4嵌入式linux-聊天程序設計

- 0.60 MB | 3次下載 | 免費

- 5基于FPGA的光纖通信系統的設計與實現

- 0.61 MB | 2次下載 | 免費

- 651單片機窗簾控制器仿真程序

- 1.93 MB | 2次下載 | 免費

- 751單片機大棚環境控制器仿真程序

- 1.10 MB | 2次下載 | 免費

- 8基于51單片機的RGB調色燈程序仿真

- 0.86 MB | 2次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 2555集成電路應用800例(新編版)

- 0.00 MB | 33564次下載 | 免費

- 3接口電路圖大全

- 未知 | 30323次下載 | 免費

- 4開關電源設計實例指南

- 未知 | 21549次下載 | 免費

- 5電氣工程師手冊免費下載(新編第二版pdf電子書)

- 0.00 MB | 15349次下載 | 免費

- 6數字電路基礎pdf(下載)

- 未知 | 13750次下載 | 免費

- 7電子制作實例集錦 下載

- 未知 | 8113次下載 | 免費

- 8《LED驅動電路設計》 溫德爾著

- 0.00 MB | 6653次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935054次下載 | 免費

- 2protel99se軟件下載(可英文版轉中文版)

- 78.1 MB | 537796次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191185次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183279次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138040次下載 | 免費

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論