資料介紹

DFT 是一種在設計階段將可測試性置入集成電路 (IC) 的方法,可以降低測試成本并提高制造良率,多年來以不同方式得到廣泛應用。Ad-hoc 和結構化這兩種方法能夠有效地檢測出電路中所有的故障,減少測試開發相關的成本和時間,以及減少測試制造芯片所需的實際時間。

Scan 和 MBIST 是兩種最常用的 DFT 工具,在功能驗證后可插入到設計中。這些工具絕對物有所值,因為在制造完成后,通過測試大量芯片是否存在制造缺陷的成本可能高達制造成本的 40%。此外,它們可以規避將失效器件推廣到市場的風險,因為召回該批次失效器件的成本遠遠大于在測試工廠發現該問題的成本,而且容易對商譽產生不可估量的負面影響。

但是,片上測試架構(例如掃描鏈、MBIST 結構和壓縮/解壓邏輯)的插入可能影響到其自身的功能正確性。因而必須在植入 DFT 之后執行門級設計驗證。然而,如今的設計規模已涉及數億個邏輯門,完全超過了硬件描述語言 (HDL) 所能達到的性能,使其在應對當前任務時幾乎毫無用處。

只有硬件加速仿真能夠驗證各種規模和復雜芯片的功能。硬件加速仿真的執行速度要比軟件仿真高出幾個數量級,例如,硬件加速仿真在數小時內就能完成需要花費約 3 個月時間的設計仿真。

新的 DFT“App”可用于硬件加速仿真*,以執行一項艱巨的任務——根據既定排程測試植入 DFT 的被測設計 (DUT),這一任務有嚴格的時間規定,可能沒有多余的浮動時間。它給硬件加速器開發流程帶來了兩大改變,第一個是編譯流程的改變,第二個是運行時間的變化。

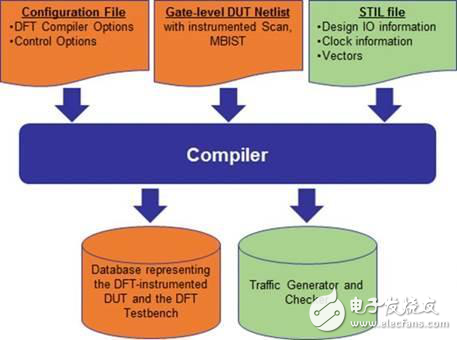

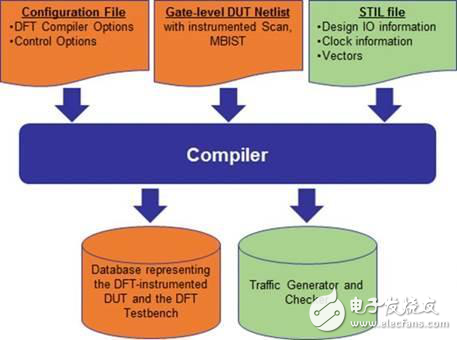

首先,包含 Scan 和 MBIST 測試結構的網表與工業標準 STIL 格式文件一起傳入硬件加速仿真編譯器,包括設計 I/O 配置、時鐘信息和測試向量。

編譯器可創建必要的架構,即流量生成器和檢查器,以便從 STIL 文件讀取測試向量,然后將包含 DFT 邏輯的 DUT 門級網表綜合成一個能夠兼容硬件加速仿真的結構化說明中,最后生成 DFT 驗證平臺。測試邏輯還包含了 DUT 輸出的對比機制(圖 1)。

圖 1.經 DFT App 修改后的編譯流程。

在調取時,設計和驗證平臺映射到硬件加速器中。在運行期間,硬件加速器通過由編譯器創建并在主機 PC 上運行的流量生成器從 STIL 文件讀取測試向量,然后通過驗證平臺應用到合成 DUT 中。檢查器以硬件加速仿真速度比較 DUT 的輸出(圖 2)。

Scan 和 MBIST 是兩種最常用的 DFT 工具,在功能驗證后可插入到設計中。這些工具絕對物有所值,因為在制造完成后,通過測試大量芯片是否存在制造缺陷的成本可能高達制造成本的 40%。此外,它們可以規避將失效器件推廣到市場的風險,因為召回該批次失效器件的成本遠遠大于在測試工廠發現該問題的成本,而且容易對商譽產生不可估量的負面影響。

但是,片上測試架構(例如掃描鏈、MBIST 結構和壓縮/解壓邏輯)的插入可能影響到其自身的功能正確性。因而必須在植入 DFT 之后執行門級設計驗證。然而,如今的設計規模已涉及數億個邏輯門,完全超過了硬件描述語言 (HDL) 所能達到的性能,使其在應對當前任務時幾乎毫無用處。

只有硬件加速仿真能夠驗證各種規模和復雜芯片的功能。硬件加速仿真的執行速度要比軟件仿真高出幾個數量級,例如,硬件加速仿真在數小時內就能完成需要花費約 3 個月時間的設計仿真。

新的 DFT“App”可用于硬件加速仿真*,以執行一項艱巨的任務——根據既定排程測試植入 DFT 的被測設計 (DUT),這一任務有嚴格的時間規定,可能沒有多余的浮動時間。它給硬件加速器開發流程帶來了兩大改變,第一個是編譯流程的改變,第二個是運行時間的變化。

首先,包含 Scan 和 MBIST 測試結構的網表與工業標準 STIL 格式文件一起傳入硬件加速仿真編譯器,包括設計 I/O 配置、時鐘信息和測試向量。

編譯器可創建必要的架構,即流量生成器和檢查器,以便從 STIL 文件讀取測試向量,然后將包含 DFT 邏輯的 DUT 門級網表綜合成一個能夠兼容硬件加速仿真的結構化說明中,最后生成 DFT 驗證平臺。測試邏輯還包含了 DUT 輸出的對比機制(圖 1)。

圖 1.經 DFT App 修改后的編譯流程。

在調取時,設計和驗證平臺映射到硬件加速器中。在運行期間,硬件加速器通過由編譯器創建并在主機 PC 上運行的流量生成器從 STIL 文件讀取測試向量,然后通過驗證平臺應用到合成 DUT 中。檢查器以硬件加速仿真速度比較 DUT 的輸出(圖 2)。

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- 硬件加速自然語言理解解決方案

- Hyperon—大數據應用的硬件加速解決方案

- 硬件加速人體姿態估計開源分享

- 硬件加速器提升下一代SHARC處理器的性能

- 利用硬件加速器提高仿真速度時的驗證平臺考慮 3次下載

- 使用硬件加速仿真的功耗分析 0次下載

- 加速可測試性設計圖形仿真 1次下載

- MD5算法硬件加速模型 0次下載

- 借助硬件加速仿真將 DFT 用于芯片設計 0次下載

- 基于硬件加速系統的PCIe-SRIO橋的邏輯結構 13次下載

- UVM驗證平臺執行硬件加速 14次下載

- 基于最優移位雙線性插值的圖像縮放旋轉硬件加速研究 10次下載

- 基于硬件加速的實時仿真平臺構建技術 1次下載

- 精確分類的視角無關人臉檢測方法與硬件加速體系結構 33次下載

- 數字集成電路設計中的硬件加速驗證技術

- 用DE1-SOC進行硬件加速的2D N-Body重力模擬器設計 386次閱讀

- Lightelligence使用Cadence Xcelium多核加速DFT仿真 1651次閱讀

- 硬件加速器提升下一代SHARC處理器的性能 1067次閱讀

- OpenCV配置CUDA以支持GPU加速 4467次閱讀

- 利用數字信號處理器上的片上FIR和IIR硬件加速器 1232次閱讀

- 如何確定一個硬件加速應用 504次閱讀

- firefly神經網絡硬件加速簡介 1884次閱讀

- 如何使用DFT App進行硬件加速仿真設計 1892次閱讀

- LSTM的硬件加速方式 2935次閱讀

- 斯坦福機器學習硬件加速器的課程學芯片技術機會來了 5970次閱讀

- 憶芯科技利用Veloce 硬件加速仿真平臺進行高速企業級固態硬盤存儲設計 1725次閱讀

- 如何使用 DFT App 進行硬件仿真 2878次閱讀

- Veloce仿真環境下的SoC端到端硬件加速器功能驗證 3491次閱讀

- 用于軟件驗證的硬件加速仿真之一:物理和虛擬探針 1962次閱讀

- 基于FPGA的軟硬件協同仿真加速技術 5074次閱讀

下載排行

本周

- 1TC358743XBG評估板參考手冊

- 1.36 MB | 330次下載 | 免費

- 2開關電源基礎知識

- 5.73 MB | 6次下載 | 免費

- 3100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

- 4嵌入式linux-聊天程序設計

- 0.60 MB | 3次下載 | 免費

- 5基于FPGA的光纖通信系統的設計與實現

- 0.61 MB | 2次下載 | 免費

- 651單片機窗簾控制器仿真程序

- 1.93 MB | 2次下載 | 免費

- 751單片機大棚環境控制器仿真程序

- 1.10 MB | 2次下載 | 免費

- 8基于51單片機的RGB調色燈程序仿真

- 0.86 MB | 2次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 2555集成電路應用800例(新編版)

- 0.00 MB | 33564次下載 | 免費

- 3接口電路圖大全

- 未知 | 30323次下載 | 免費

- 4開關電源設計實例指南

- 未知 | 21549次下載 | 免費

- 5電氣工程師手冊免費下載(新編第二版pdf電子書)

- 0.00 MB | 15349次下載 | 免費

- 6數字電路基礎pdf(下載)

- 未知 | 13750次下載 | 免費

- 7電子制作實例集錦 下載

- 未知 | 8113次下載 | 免費

- 8《LED驅動電路設計》 溫德爾著

- 0.00 MB | 6653次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935054次下載 | 免費

- 2protel99se軟件下載(可英文版轉中文版)

- 78.1 MB | 537796次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191185次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183279次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138040次下載 | 免費

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論