資料介紹

自2005年9月LXI總線推出以來,已經顯示出其組建測試系統的眾多優點。基于LXI總線組建測試系統具有易于使用、靈活性高、模塊化和可擴縮性、實現更快的系統吞吐率、可分布式應用、長壽命、低成本、通過IEEE1588時鐘同步、機架空間小、合成儀器等諸多優點。

1553B總線的全名為“時分制指令/響應式多路傳輸數據總線”,國內多型戰斗機、軍艦等武器平臺都采用其作為傳輸總線。因此研制基于LXI總線的1553B通訊模塊,不僅能滿足多型武器裝備對1553B總線的測試需求,也對LXI總線在國內的研究和應用有推動作用。

1 模塊總體方案

模塊基本設計指標為:滿足LXI規范C類儀器標準;支持DHCP、自動配置IP地址和手動配置IP地址;支持ICMP協議、TCP/IP協議和UDP協議;同步采用網絡命令方式;能完成1553B在BC模式下的所有功能。

根據指標要求采用基于SOPC的32位處理器+實時多任務操作系統(Real Time Operation System,RTOS)總體方案,在一塊FPGA芯片上集成了控制器和邏輯單元,既降低了開發的難度、減少了模塊體積,也易于以后的升級。32位處理器有足夠的資源可以擴充利用,RAM和ROM可以做的足夠大,整個TCP/IP協議族可以做到系統里面去,甚至可以嵌入一個帶TCP/IP協議族的操作系統。

2 基于SOPC的硬件設計與開發

片上可編程系統(System on a Programmable Chip,SOPC)將處理器、存儲器、I/O口、LVDS和CDR等系統設計需要的功能模塊集成到一個PLD器件上構建成一個可編程的片上系統,是一種靈活高效的SOC解決方案。SOPC結合了SOC和可編程邏輯器件各自的優點,具有靈活的設計方式、可剪裁、可擴充、可升級,并具備軟硬件在系統可編程的功能,成為SOC設計的新趨勢。

2.1 模塊硬件架構

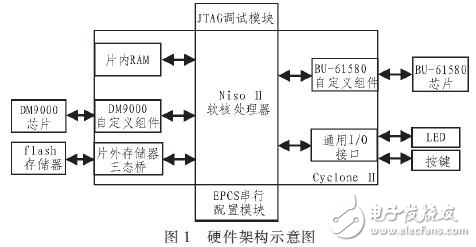

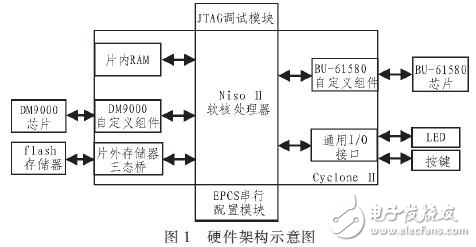

模塊硬件主要由NiosII軟核處理器、以太網組件、1553B總線組件、存儲器、片內RAM、通用I/O接口和調試配置模塊7部分組成,架構示意如圖1所示。

1)NiosII軟核處理器:模塊的CPU,負責系統工作調度。在其內部移植了μC/OSII實時操作系統和LwIP協議;它接受客戶端通過以太網發送過來的請求,經解析后回復Web界面或控制1553B功能接口;2)以太網組件(DM9000A):完成對以太網控制器的操作,將網絡上的數據經以太網控制器送到網際層,由NioslI軟核處理器內的LwIP協議處理;或者將網際層送來的數據經以太網接口發送出去:3)1553B總線組件(BU-61580):受NiosllI軟核處理器控制,完成在BC模式下各類消息和命令的發送及狀態的讀取;4)Flash存儲器:主要用來存儲模塊的一些固定參數和靜態Web界面;5)片內RAM:RAM是在FPGA剩余邏輯中用Quartusll內所帶的MegaWizard管理器生成的,這樣就不需要外加RAM芯片。片內RAM主要是用來存儲程序運行過程中所接收和產生的一些數據;6)通用I/O接口:用來完成對LED或按鍵的控制;7)JTAG調試模塊和EPCS配置模塊:J1TAG模塊用來完成對程序的調試工作。配置是對FPGA的內容進行編程的過程,每次上電后都需要配置,EPCS配置模塊允許NioslI訪問EPCS串行配置器件。

具體開發主要有3部分工作:1)NiosII軟核處理器及其外設的設計。2)自定義宏功能模塊RAM的開發,這部分工作在QuartuslI軟件中完成;3)應用軟件程序的編寫,在NiosIIIDE軟件開發環境中完成。

2.2 模塊硬件設計

SOPC Builder是Altera公司為用戶自定義系統而開發的工具。用戶使用SOPC Builder可以將IP核、存儲器、接口、微處理器和自定義組件等復雜系統組件簡單又快速的集成到Ahera高密度FPGA芯片上。按照模塊硬件系統的要求,借助SOPC Builder生成的模塊硬件結構,包括:32位標準NiosII軟核處理器:cpu;JTAG調試接口:jtag-debug-module;外部SDRAM存儲器接口:sdram;Avalon三態橋:tri_state_brid ge;EPCS串行閃存控制器:EPCS_controller;外部FLASH存儲器接口:cfi_flash;定時/計數器:time0/timel;以太網接口:dm9000a;1553B接口:bu61580;LED接口:led;64KRAM接口:RAM;按鍵接口:key;系統識別模塊:sysid。

1553B總線的全名為“時分制指令/響應式多路傳輸數據總線”,國內多型戰斗機、軍艦等武器平臺都采用其作為傳輸總線。因此研制基于LXI總線的1553B通訊模塊,不僅能滿足多型武器裝備對1553B總線的測試需求,也對LXI總線在國內的研究和應用有推動作用。

1 模塊總體方案

模塊基本設計指標為:滿足LXI規范C類儀器標準;支持DHCP、自動配置IP地址和手動配置IP地址;支持ICMP協議、TCP/IP協議和UDP協議;同步采用網絡命令方式;能完成1553B在BC模式下的所有功能。

根據指標要求采用基于SOPC的32位處理器+實時多任務操作系統(Real Time Operation System,RTOS)總體方案,在一塊FPGA芯片上集成了控制器和邏輯單元,既降低了開發的難度、減少了模塊體積,也易于以后的升級。32位處理器有足夠的資源可以擴充利用,RAM和ROM可以做的足夠大,整個TCP/IP協議族可以做到系統里面去,甚至可以嵌入一個帶TCP/IP協議族的操作系統。

2 基于SOPC的硬件設計與開發

片上可編程系統(System on a Programmable Chip,SOPC)將處理器、存儲器、I/O口、LVDS和CDR等系統設計需要的功能模塊集成到一個PLD器件上構建成一個可編程的片上系統,是一種靈活高效的SOC解決方案。SOPC結合了SOC和可編程邏輯器件各自的優點,具有靈活的設計方式、可剪裁、可擴充、可升級,并具備軟硬件在系統可編程的功能,成為SOC設計的新趨勢。

2.1 模塊硬件架構

模塊硬件主要由NiosII軟核處理器、以太網組件、1553B總線組件、存儲器、片內RAM、通用I/O接口和調試配置模塊7部分組成,架構示意如圖1所示。

1)NiosII軟核處理器:模塊的CPU,負責系統工作調度。在其內部移植了μC/OSII實時操作系統和LwIP協議;它接受客戶端通過以太網發送過來的請求,經解析后回復Web界面或控制1553B功能接口;2)以太網組件(DM9000A):完成對以太網控制器的操作,將網絡上的數據經以太網控制器送到網際層,由NioslI軟核處理器內的LwIP協議處理;或者將網際層送來的數據經以太網接口發送出去:3)1553B總線組件(BU-61580):受NiosllI軟核處理器控制,完成在BC模式下各類消息和命令的發送及狀態的讀取;4)Flash存儲器:主要用來存儲模塊的一些固定參數和靜態Web界面;5)片內RAM:RAM是在FPGA剩余邏輯中用Quartusll內所帶的MegaWizard管理器生成的,這樣就不需要外加RAM芯片。片內RAM主要是用來存儲程序運行過程中所接收和產生的一些數據;6)通用I/O接口:用來完成對LED或按鍵的控制;7)JTAG調試模塊和EPCS配置模塊:J1TAG模塊用來完成對程序的調試工作。配置是對FPGA的內容進行編程的過程,每次上電后都需要配置,EPCS配置模塊允許NioslI訪問EPCS串行配置器件。

具體開發主要有3部分工作:1)NiosII軟核處理器及其外設的設計。2)自定義宏功能模塊RAM的開發,這部分工作在QuartuslI軟件中完成;3)應用軟件程序的編寫,在NiosIIIDE軟件開發環境中完成。

2.2 模塊硬件設計

SOPC Builder是Altera公司為用戶自定義系統而開發的工具。用戶使用SOPC Builder可以將IP核、存儲器、接口、微處理器和自定義組件等復雜系統組件簡單又快速的集成到Ahera高密度FPGA芯片上。按照模塊硬件系統的要求,借助SOPC Builder生成的模塊硬件結構,包括:32位標準NiosII軟核處理器:cpu;JTAG調試接口:jtag-debug-module;外部SDRAM存儲器接口:sdram;Avalon三態橋:tri_state_brid ge;EPCS串行閃存控制器:EPCS_controller;外部FLASH存儲器接口:cfi_flash;定時/計數器:time0/timel;以太網接口:dm9000a;1553B接口:bu61580;LED接口:led;64KRAM接口:RAM;按鍵接口:key;系統識別模塊:sysid。

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- 基于LXI總線的1553B通訊模塊設計與開發

- 基于LabVIEW的1553B多路傳輸數據總線通信 20次下載

- 基于1553B總線的導彈飛控軟件測試仿真平臺 29次下載

- 基于DSP的1553B總線系統設計解析 8次下載

- MIL-STD-1553B入門教程_1553B總線資料課件201 0次下載

- 基于1553B總線遠程終端的FPGA程序設計 37次下載

- 基于ARM-Linux的1553B仿真測試前端系統 11次下載

- 高性能光纖通道上實現1553B協議的研究

- 通用1553B總線的信息監控系統

- 基于FPGA的1553B通信模塊的設計

- 基于SOPC的1553B總線接口邏輯設計

- 基于SOPC的1553B總線遠程終端接口設計

- 基于ARM的1553B總線應用

- 基于USB接口1553B總線設備檢測系統設計

- 1553B總線在武器通信中的應用探討

- 基于TDA1553汽車立體聲放大器電路 950次閱讀

- nRF24L01無線通訊模塊的驅動設計與實現 3027次閱讀

- ESP8266無線通訊模塊的驅動設計與實現 2541次閱讀

- 嵌入式開發中串口通訊方案 2249次閱讀

- 利用FPGA器件和TMS320F206芯片實現飛機總線通訊系統的設計方案 833次閱讀

- 采用BC定時查詢方式的總線控制器異步通訊處理方案 2440次閱讀

- 基于AT89C52單片機和BU-61580芯片實現1553B總線的開發板設計 5863次閱讀

- 采用EP1C20芯片和S698IP核實現平臺計算機的設計 1211次閱讀

- 采用PC/104嵌入式模塊與1553B總線卡實現測控系統的設計 3841次閱讀

- dfrobotBLEmicro 藍牙4.0通訊模塊簡介 1864次閱讀

- 地鐵屏蔽門無線通訊模塊解決方案 1624次閱讀

- 基于1553B總線和ARINC429總線的數據格式介紹 1.5w次閱讀

- 基于FPGA的1553B總線接口設計與驗證 2w次閱讀

- 基于ARM的便攜式1553B總線測試系統的設計與實現 3970次閱讀

- 基于PCI局部總線的1553B總線接口卡設計 3267次閱讀

下載排行

本周

- 1TC358743XBG評估板參考手冊

- 1.36 MB | 330次下載 | 免費

- 2開關電源基礎知識

- 5.73 MB | 6次下載 | 免費

- 3100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

- 4嵌入式linux-聊天程序設計

- 0.60 MB | 3次下載 | 免費

- 5基于FPGA的光纖通信系統的設計與實現

- 0.61 MB | 2次下載 | 免費

- 6基于FPGA的C8051F單片機開發板設計

- 0.70 MB | 2次下載 | 免費

- 751單片機窗簾控制器仿真程序

- 1.93 MB | 2次下載 | 免費

- 8基于51單片機的RGB調色燈程序仿真

- 0.86 MB | 2次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 2555集成電路應用800例(新編版)

- 0.00 MB | 33564次下載 | 免費

- 3接口電路圖大全

- 未知 | 30323次下載 | 免費

- 4開關電源設計實例指南

- 未知 | 21548次下載 | 免費

- 5電氣工程師手冊免費下載(新編第二版pdf電子書)

- 0.00 MB | 15349次下載 | 免費

- 6數字電路基礎pdf(下載)

- 未知 | 13750次下載 | 免費

- 7電子制作實例集錦 下載

- 未知 | 8113次下載 | 免費

- 8《LED驅動電路設計》 溫德爾著

- 0.00 MB | 6653次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935054次下載 | 免費

- 2protel99se軟件下載(可英文版轉中文版)

- 78.1 MB | 537796次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191185次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183278次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138040次下載 | 免費

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論