資料介紹

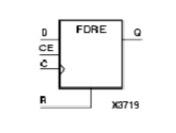

1、源語---FDRE

FDRE代表一個單D型觸發(fā)器,含的有五個信號分別為: 數(shù)據(jù)(data,D)、時鐘使能(Clock enable,CE)、時鐘(Clock)、同步復位(synchronous reset,R)、數(shù)據(jù)輸出(dataout,Q)。當輸入的同步復位信號為高時,否決(override)所有輸入,并在時鐘的上升沿將輸出Q為低信號。在時鐘的上升沿數(shù)據(jù)被加載進入D觸發(fā)器的輸入。

FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg1 ( .C (clk), // 同步時鐘 .D (data_sync0), //異步數(shù)據(jù)輸入 .Q (data_sync1), //同步數(shù)據(jù)輸出 .CE (1'b1), //時鐘使能信號 .R (1'b0) //復位信號輸入,高電平有效 );

由于數(shù)據(jù)可能與時鐘存在著不同步的情況,尤其是在對同步精度要求高的場合,一般還是用多次FDRE源語使得數(shù)據(jù)、控制信號等同步,例如在一個三態(tài)網(wǎng)數(shù)據(jù)同步模塊中使用了四個D觸發(fā)器進行數(shù)據(jù)同步:

`timescale 1ps / 1ps (* dont_touch = "yes" *) module tri_mode_ethernet_mac_0_sync_block #( parameter INITIALISE = 1'b0, parameter DEPTH = 5 ) ( input clk, // clock to be sync'ed to input data_in, // Data to be 'synced' output data_out // synced data ); // Internal Signals wire data_sync0; wire data_sync1; wire data_sync2; wire data_sync3; wire data_sync4; (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg0 ( .C (clk), .D (data_in), .Q (data_sync0), .CE (1'b1), .R (1'b0) ); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg1 ( .C (clk), .D (data_sync0), .Q (data_sync1), .CE (1'b1), .R (1'b0) ); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg2 ( .C (clk), .D (data_sync1), .Q (data_sync2), .CE (1'b1), .R (1'b0) ); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg3 ( .C (clk), .D (data_sync2), .Q (data_sync3), .CE (1'b1), .R (1'b0) ); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg4 ( .C (clk), .D (data_sync3), .Q (data_sync4), .CE (1'b1), .R (1'b0) ); assign data_out = data_sync4; endmodule

本文轉載自:https://www.cnblogs.com/luxinshuo/p/11913988.html,轉載此文目的在于傳播相關技術知識,版權歸原作者所有,如涉及侵權,請聯(lián)系小編刪除(聯(lián)系郵箱:service@eetrend.com )。

- Xilinx-ISE9.x-FPGA-CPLD設計指南合集 77次下載

- 基于FDRE的節(jié)水灌溉智能控制系統(tǒng) 26次下載

- 基于短語的漢語維吾爾語機器翻譯系統(tǒng) 9次下載

- 電壓源與電流源及其等效變換課件下載 11次下載

- Xilinx的時序設計與約束資料詳細說明 34次下載

- 如何使用Xilinx的FPGA對高速PCB信號實現(xiàn)優(yōu)化設計 26次下載

- Xilinx 7 系列FPGA中的Serdes總結 25次下載

- xilinx的FPGA芯片選型手冊免費下載 51次下載

- 如何使用LVQ進行普米語語譜圖的識別說明 7次下載

- 如何進行馬來語語音合成系統(tǒng)的設計與實現(xiàn)概述 4次下載

- 緬甸語分詞方法及其實現(xiàn)方法來開發(fā)緬甸語的語音合成系統(tǒng) 0次下載

- 通信行業(yè)最齊全的英語縮語手冊

- Xilinx Solutions for Automotiv

- 通信英語縮語手冊

- 天語手機usb驅動程序

- Xilinx fpga芯片系列有哪些 2329次閱讀

- Xilinx FPGA IP之Block Memory Generator功能概述 1955次閱讀

- Xilinx源語:Input DDR Overview(IDDR)介紹 2080次閱讀

- 人工智能閱讀的突破唇語 2543次閱讀

- Xilinx FPGA的FMC介紹 5643次閱讀

- Xilinx FPGA的電源設計詳解 1w次閱讀

- Xilinx品牌FPGA使用的三種證書 4193次閱讀

- 基于QEMU系統(tǒng)模擬器Xilinx/QEMU的運行與調(diào)試 8887次閱讀

- xilinx公司的代理商有哪些_十大xilinx公司的代理商推薦 3.9w次閱讀

- Xilinx設備的驅動程序 7967次閱讀

- 基于Xilinx的軟件工程的創(chuàng)建 1570次閱讀

- Xilinx SDK使用教程 4725次閱讀

- 記利用compxlibgui工具編譯Xilinx庫 1369次閱讀

- 如何在設計階段考慮降低XILINX的功耗 1983次閱讀

- Xilinx DPD 解決方案使用經(jīng)驗(七) 3497次閱讀

下載排行

本周

- 1電子電路原理第七版PDF電子教材免費下載

- 0.00 MB | 1491次下載 | 免費

- 2單片機典型實例介紹

- 18.19 MB | 95次下載 | 1 積分

- 3S7-200PLC編程實例詳細資料

- 1.17 MB | 27次下載 | 1 積分

- 4筆記本電腦主板的元件識別和講解說明

- 4.28 MB | 18次下載 | 4 積分

- 5開關電源原理及各功能電路詳解

- 0.38 MB | 11次下載 | 免費

- 6100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

- 7基于單片機和 SG3525的程控開關電源設計

- 0.23 MB | 4次下載 | 免費

- 8基于AT89C2051/4051單片機編程器的實驗

- 0.11 MB | 4次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費

- 2PADS 9.0 2009最新版 -下載

- 0.00 MB | 66304次下載 | 免費

- 3protel99下載protel99軟件下載(中文版)

- 0.00 MB | 51209次下載 | 免費

- 4LabView 8.0 專業(yè)版下載 (3CD完整版)

- 0.00 MB | 51043次下載 | 免費

- 5555集成電路應用800例(新編版)

- 0.00 MB | 33562次下載 | 免費

- 6接口電路圖大全

- 未知 | 30320次下載 | 免費

- 7Multisim 10下載Multisim 10 中文版

- 0.00 MB | 28588次下載 | 免費

- 8開關電源設計實例指南

- 未知 | 21539次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935053次下載 | 免費

- 2protel99se軟件下載(可英文版轉中文版)

- 78.1 MB | 537793次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191183次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183277次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138039次下載 | 免費

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問

提問  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評論