【ZYNQ Ultrascale+ MPSOC FPGA教程】第五章 Vivado下PLL實驗 ALINX

資料介紹

作者: ALINX

* 本原創教程由芯驛電子科技(上海)有限公司(ALINX)創作,版權歸本公司所有,如需轉載,需授權并注明出處。

適用于板卡型號:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

實驗Vivado工程為“pll_test”。

很多初學者看到板上只有一個25Mhz時鐘輸入的時候都產生疑惑,時鐘怎么是25Mhz?如果要工作在100Mhz、150Mhz怎么辦?其實在很多FPGA芯片內部都集成了PLL,其他廠商可能不叫PLL,但是也有類似的功能模塊,通過PLL可以倍頻分頻,產生其他很多時鐘。本實驗通過調用PLL IP core來學習PLL的使用、vivado的IP core使用方法。

1.實驗原理

PLL(phase-locked loop),即鎖相環。是FPGA中的重要資源。由于一個復雜的FPGA系統往往需要多個不同頻率,相位的時鐘信號。所以,一個FPGA芯片中PLL的數量是衡量FPGA芯片能力的重要指標。FPGA的設計中,時鐘系統的FPGA高速的設計極其重要,一個低抖動, 低延遲的系統時鐘會增加FPGA設計的成功率。

本實驗將通過使用PLL, 輸出一個方波到開發板上的擴展口,來給大家演示在Vivado軟件里使用PLL的方法。

Ultrascale+系列的FPGA使用了專用的全局(Global)和區域(Regional)IO和時鐘資源來管理設計中各種的時鐘需求。Clock Management Tiles(CMT)提供了時鐘合成(Clock frequency synthesis),傾斜矯正(deskew),過濾抖動(jitter filtering)功能。

每個CMTs包含一個MMCM(mixed-mode clock manager)和一個PLL。如下圖所示,CMT的輸入可以是BUFR,IBUFG,BUFG,GT,BUFH,本地布線(不推薦使用),輸出需要接到BUFG或者BUFH后再使用

混合模式時鐘管理器(MMCM)

MMCM用于在與給定輸入時鐘有設定的相位和頻率關系的情況下,生成不同的時鐘信號。MMCM提供了廣泛而強大的時鐘管理功能,

MMCM內部的功能框圖如下圖所示:

數字鎖相環(PLL)

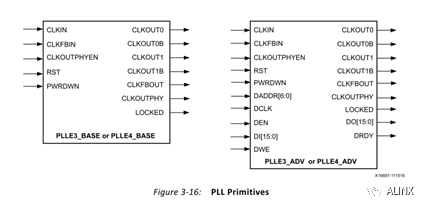

鎖相環(PLL)主要用于頻率綜合。使用一個PLL可以從一個輸入時鐘信號生成多個時鐘信號。與MMCM相比,不能進行時鐘的deskew,不具備高級相位調整,倍頻器和分頻器可調范圍較小等。

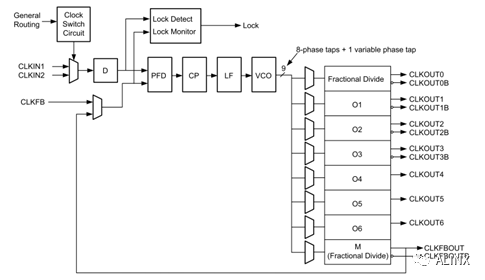

PLL功能框圖如下圖所示:

想了解更多的時鐘資源, 建議大家看看Xilinx提供的文檔"7 Series FPGAs Clocking Resources User Guide"。

2. 創建Vivado工程

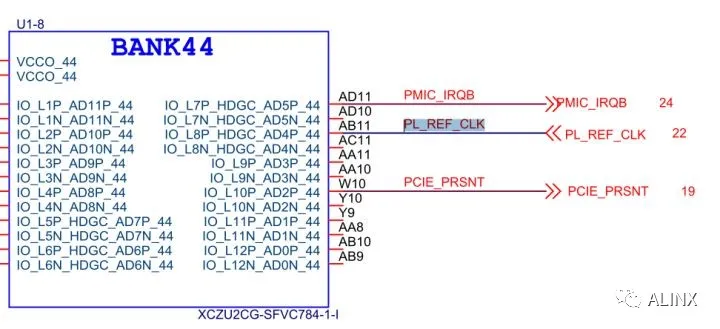

本實驗中為大家演示如果調用Xilinx提供的PLL IP核來產生不同頻率的時鐘, 并把其中的一個時鐘輸出到FPGA外部IO上, 下面為程序設計的詳細步驟。在創建PLL IP之前,有一點需要提下,在原理圖中可以看到PL_REF_CLK,也就是25MHz參考時鐘,在BANK44中,而且屬于HDGC

在ug572文檔中提到HDGC引腳不能直接連接到MMCMs/PLLs,需要經過BUFG,再連接到MMCMs/PLLs,這個地方是需要注意的。

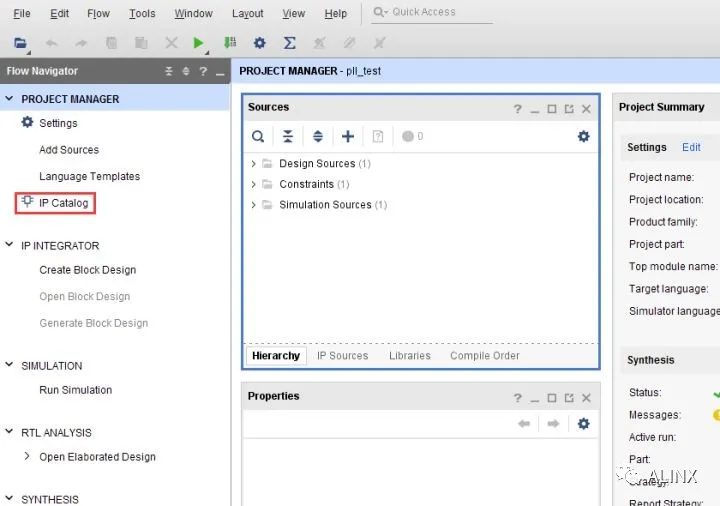

新建一個pll_test的工程,點擊Project Manager界面下的IP Catalog。

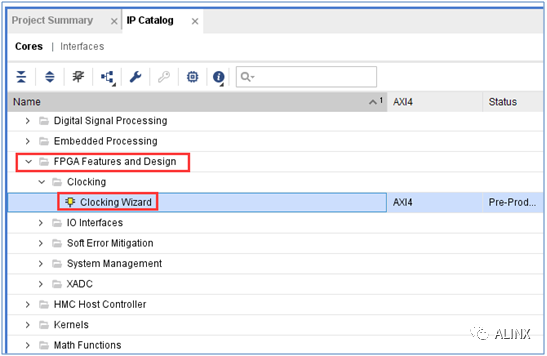

2.1 再在IP Catalog界面里選擇FPGA Features and Design/Clocking下面的Clocking Wizard,雙擊打開配置界面。

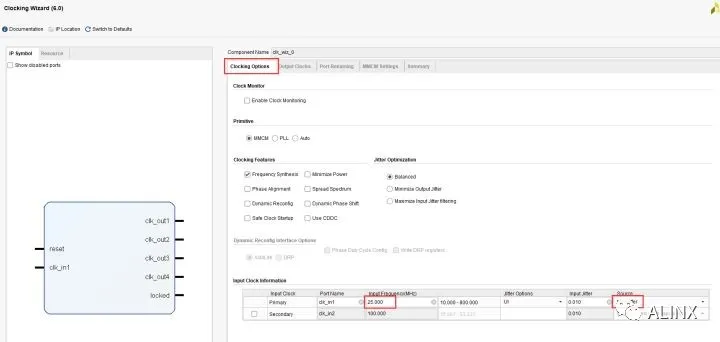

2.2 默認這個Clocking Wizard的名字為clk_wiz_0, 這里我們不做修改。在第一個界面Clocking Options里,輸入的時鐘頻率為25Mhz,并選擇No buffer,也就是在PLL之前要接個BUFG。

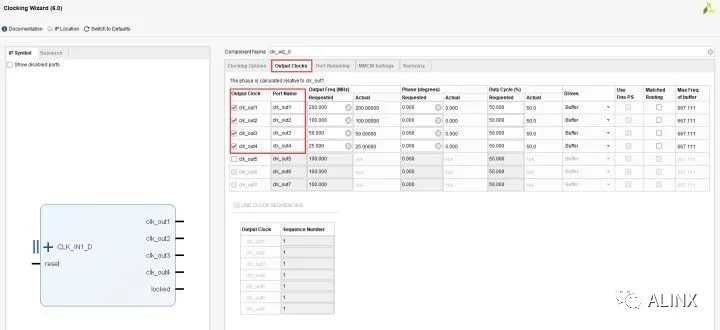

2.3 在Output Clocks界面里選擇clk_out1~clk_out4四個時鐘的輸出,頻率分別為200Mhz, 100Mhz, 50Mhz, 25Mhz。這里還可以設置時鐘輸出的相位,我們不做設置,保留默認相位,點擊 OK完成,

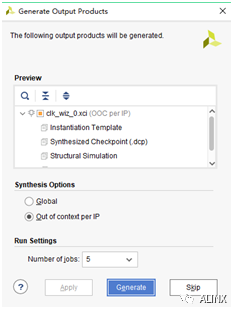

2.4 在彈出的對話框中點擊Generate按鈕生成PLL IP的設計文件。

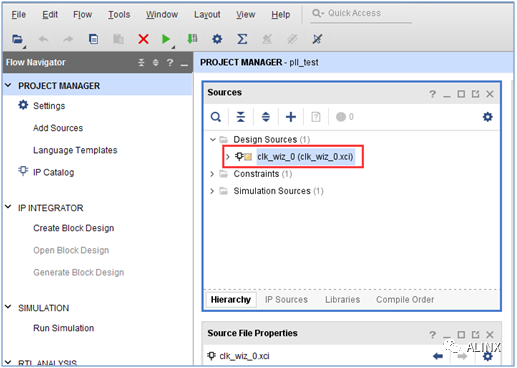

2.5 這時一個 clk_wiz_0.xci的IP會自動添加到我們的pll_test項目中, 用戶可以雙擊它來修改這個IP的配置。

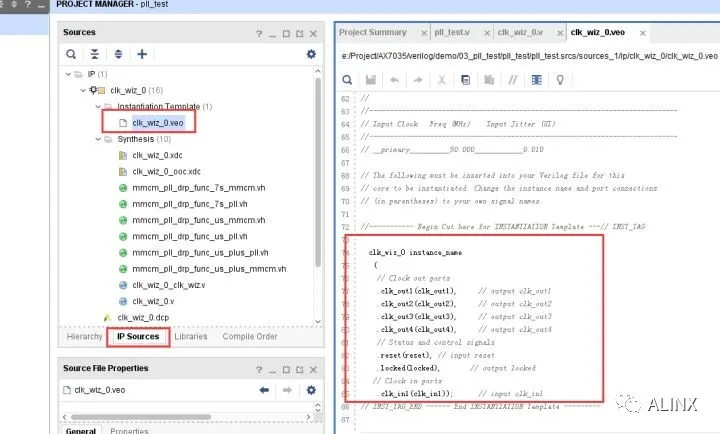

選擇IP Sources這頁,然后雙擊打開clk_wiz_0.veo文件,這個文件里提供了這個IP的實例化模板。我們只需要把框框的中內容拷貝到我們verilog程序中,對IP進行實例化。

2.6 我們再來編寫一個頂層設計文件來實例化這個PLL IP, 編寫pll_test.v代碼如下。注意PLL的復位是高電平有效,也就是高電平時一直在復位狀態,PLL不會工作,這一點很多新手會忽略掉。這里我們將rst_n綁定到一個按鍵上,而按鍵是低電平復位,因此需要反向連接到PLL的復位。在程序中插入一個BUFG原語,連接到PLL。

`timescale1ns/1ps module pll_test( input sys_clk,//system clock 25Mhz on board input rst_n,//reset ,low active output clk_out //pll clock output ); wire locked; wire sys_clkbuf ; BUFG BUFG_inst ( .O(sys_clkbuf),// 1-bit output: Clock output. .I(sys_clk)// 1-bit input: Clock input. ); /////////////////////PLL IP call//////////////////////////// clk_wiz_0 clk_wiz_0_inst (// Clock in ports .clk_in1(sys_clkbuf),// IN 25Mhz // Clock out ports .clk_out1(),// OUT 200Mhz .clk_out2(),// OUT 100Mhz .clk_out3(),// OUT 50Mhz .clk_out4(clk_out),// OUT 25Mhz // Status and control signals .reset(~rst_n),// pll reset, high-active .locked(locked));// OUT endmodule

程序中先用實例化clk_wiz_0, 把25Mhz時鐘信號輸入到clk_wiz_0的clk_in1_p和clk_in1_n,把clk_out4的輸出賦給clk_out。

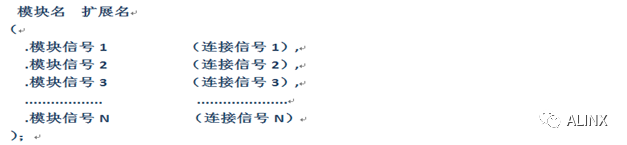

注意:例化的目的是在上一級模塊中調用例化的模塊完成代碼功能,在Verilog里例化信號的格式如下:模塊名必須和要例化的模塊名一致,比如程序中的clk_wiz_0,包括模塊信號名也必須一致,比如clk_in1,clk_out1,clk_out2.....。連接信號為TOP程序跟模塊之間傳遞的信號,模塊與模塊之間的連接信號不能相互沖突,否則會產生編譯錯誤。

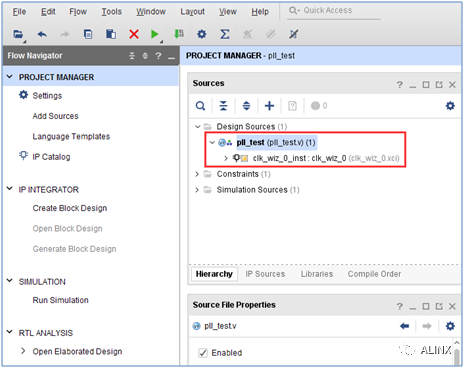

2.7 保存工程后,pll_test自動成為了top文件,clk_wiz_0成為Pll_test文件的子模塊。

2.8 再為工程添加xdc管腳約束文件pll.xdc,添加方法參考”PL的”Hello World”LED實驗”,也可以直接復制以下內容。并編譯生成bitstream。

############## clock and reset define##################set_property PACKAGE_PIN AB11 [get_ports sys_clk]

set_property IOSTANDARD LVCMOS33 [get_ports sys_clk]

create_clock -period 40.000 -name sys_clk -waveform {0.000 20.000} [get_ports sys_clk]

set_property IOSTANDARD LVCMOS33 [get_ports {rst_n}]

set_property PACKAGE_PIN AA13 [get_ports {rst_n}]

############## pll output define J11 PIN3##################

set_property IOSTANDARD LVCMOS33 [get_ports clk_out]

set_property PACKAGE_PIN A11 [get_ports clk_out]

3.板上驗證

編譯工程并生成pll_test.bit文件,再把bit文件下載到FPGA中,接下去我們就可以用示波器來測量輸出時鐘波形了。

用示波器探頭的地線連接到開發板上的地(開發板J15的PIN1腳),信號端連接開發板J15的PIN3腳(測量的時候需要注意,避免示波器表頭碰到其它管腳而導致電源和地短路)。

這時我們可以在示波器里看到25Mhz的時鐘波形,波形的幅度為3.3V, 占空比為1:1,波形顯示如下圖所示:

如果您想輸出其它頻率的波形,可以修改時鐘的輸出為clk_wiz_0的clk_out2或clk_out3或clk_out4。也可以修改clk_wiz_0的clk_out4為您想要的頻率,這里也需要注意一下,因為時鐘的輸出是通過PLL對輸入時鐘信號的倍頻和分頻系數來得到的,所以并不是所有的時鐘頻率都可以用PLL能夠精確產生的,不過PLL也會自動為您計算實際輸出接近的時鐘頻率。

另外需要注意的是,有些用戶的示波器的帶寬和采樣率太低,會導致測量高頻時鐘信號的時候,高頻部分衰減太大,測量波形的幅度會變低。

- 采用Zynq UltraScale+ MPSoC滿足汽車ESD和SEED要求

- Zynq UltraScale+ MPSoC中的隔離方法應用筆記

- Zynq UltraScale+ MPSoC生產勘誤表

- Zynq UltraScale+ MPSoC數據手冊:DC和AC開關特性

- Zynq UltraScale+ MPSoC驗證數據手冊

- Zynq UltraScale+ MPSoC:軟件開發者指南

- Zynq UltraScale+ MPSoC中的隔離方法

- Zynq UltraScale+ MPSoC的隔離設計示例

- 適用于Xilinx Zynq UltraScale+ MPSoC應用的電源參考設計

- 米爾電子zynq ultrascale+ mpsoc底板外設資源清單分享

- 如何調試 Zynq UltraScale+ MPSoC VCU DDR 控制器?

- 【ZYNQ Ultrascale+ MPSOC FPGA教程】第一章 MPSoC芯片介紹

- 【ZYNQ Ultrascale+ MPSOC FPGA教程】第九章Vivado下按鍵實驗

- 如何使用Zynq UltraScale和MPSOC管理電源和性能資料說明 18次下載

- 電力系統繼電保護第五章-自動重合閘(課件)下載.PPT 0次下載

- 針對UltraScale/UltraScale+芯片DFX應考慮的因素有哪些(1) 537次閱讀

- Xilinx ZYNQ UltraScale+系列產品介紹 2405次閱讀

- FPGAs,Zynq和Zynq MPSoC器件的特點 2275次閱讀

- 基于Xilinx Zynq UltraScale+ RFSoC ZCU216評估套件詳細內容介紹 9162次閱讀

- 基于Xilinx Zynq ultraScale+ 系列FPGA的AXU2CGB 開發板評測 9051次閱讀

- 米爾科技Zynq UltraScale+ MPSoC技術參考手冊介紹 2975次閱讀

- 詳解Xilinx公司Zynq? UltraScale+?MPSoC產品 3184次閱讀

- Xilinx Zynq UltraScale MPSoC可擴展電源設計 1950次閱讀

- Xilinx Kintex UltraScale+ FPGA KCU116評估套件主要性能和優勢 6734次閱讀

- Zynq UltraScale+ MPSoC ZCU102評估套件解決方案 8640次閱讀

- Enea OSE可實現對Xilinx UltraScale+ MPSoC的支持 2790次閱讀

- Xilinx基于ARM的Zynq-7000和Zynq UltraScale+ MPSoC及RFSoC器件是否存在安全漏洞 2620次閱讀

- Zynq UltraScale+ MPSoC 上的多個Linux UIO設計 3219次閱讀

- 用ZYNQ MPSoC玩DOOM! 2539次閱讀

- Ti推出面向Zynq UltraScale+ MPSoC的電源參考設計 3588次閱讀

下載排行

本周

- 1電子電路原理第七版PDF電子教材免費下載

- 0.00 MB | 1491次下載 | 免費

- 2單片機典型實例介紹

- 18.19 MB | 95次下載 | 1 積分

- 3S7-200PLC編程實例詳細資料

- 1.17 MB | 27次下載 | 1 積分

- 4筆記本電腦主板的元件識別和講解說明

- 4.28 MB | 18次下載 | 4 積分

- 5開關電源原理及各功能電路詳解

- 0.38 MB | 11次下載 | 免費

- 6100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

- 7基于單片機和 SG3525的程控開關電源設計

- 0.23 MB | 4次下載 | 免費

- 8基于AT89C2051/4051單片機編程器的實驗

- 0.11 MB | 4次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費

- 2PADS 9.0 2009最新版 -下載

- 0.00 MB | 66304次下載 | 免費

- 3protel99下載protel99軟件下載(中文版)

- 0.00 MB | 51209次下載 | 免費

- 4LabView 8.0 專業版下載 (3CD完整版)

- 0.00 MB | 51043次下載 | 免費

- 5555集成電路應用800例(新編版)

- 0.00 MB | 33562次下載 | 免費

- 6接口電路圖大全

- 未知 | 30320次下載 | 免費

- 7Multisim 10下載Multisim 10 中文版

- 0.00 MB | 28588次下載 | 免費

- 8開關電源設計實例指南

- 未知 | 21539次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935053次下載 | 免費

- 2protel99se軟件下載(可英文版轉中文版)

- 78.1 MB | 537793次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191183次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183277次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138039次下載 | 免費

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論