資料介紹

作者: ALINX

* 本原創教程由芯驛電子科技(上海)有限公司(ALINX)創作,版權歸本公司所有,如需轉載,需授權并注明出處。

簡介

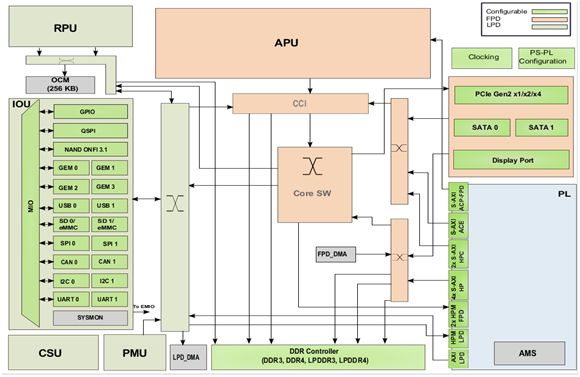

Zynq UltraScale+ MPSoC系列是Xilinx第二代Zynq平臺。其亮點在于FPGA里包含了完整的ARM處理子系統(PS),包含了四核Cortex-A53處理器或雙核Cortex-A53加雙核Cortex-R5處理器,整個處理器的搭建都以處理器為中心,而且處理器子系統中集成了內存控制器和大量的外設,使處理器核在Zynq中完全獨立于可編程邏輯單元,也就是說如果暫時沒有用到可編程邏輯單元部分(PL), ARM處理器的子系統也可以獨立工作,這與以前的FPGA有本質區別,其是以處理器為中心的。

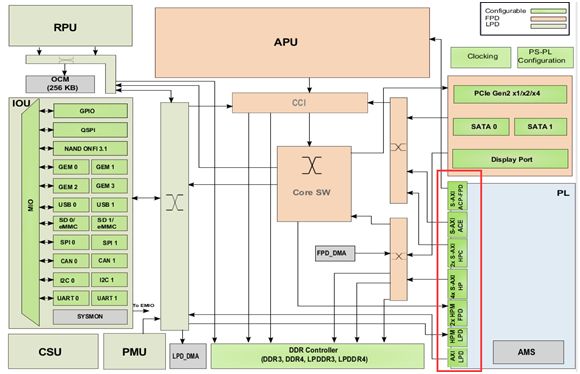

Zynq就是兩大功能塊,PS 部分和 PL部分,說白了,就是ARM的SOC部分,和FPGA部分。其中,PS集成了APU ARM Cortex?-A53處理器,RPU Cortex-R5處理器,AMBA?互連,內部存儲器(OCM),外部存儲器接口(DDR Controller)和外設(IOU)。這些外設(IOU)主要包括USB總線接口,以太網接口,SD/eMMC接口,I2C總線接口,CAN總線接口,UART接口,GPIO等。高速接口如PCIe,SATA,Display Port。

ZYNQ MPSoC芯片的總體框圖

PS: 處理系統(Processing System) , 就是與FPGA無關的ARM的SoC的部分。

PL: 可編程邏輯 (Progarmmable Logic), 就是FPGA部分。

1.1 PS和PL互聯技術

ZYNQ作為將高性能ARM Cortex-A53系列處理器與高性能FPGA在單芯片內緊密結合的產品,為了實現ARM處理器和FPGA之間的高速通信和數據交互,發揮ARM處理器和FPGA的性能優勢,需要設計高效的片內高性能處理器與FPGA之間的互聯通路。因此,如何設計高效的PL和PS數據交互通路是ZYNQ芯片設計的重中之重,也是產品設計的成敗關鍵之一。本節,我們就將主要介紹PS和PL的連接,讓用戶了解PS和PL之間連接的技術。

其實,在具體設計中我們往往不需要在連接這個地方做太多工作,我們加入IP核以后,系統會自動使用AXI接口將我們的IP核與處理器連接起來,我們只需要再做一點補充就可以了。

AXI全稱Advanced eXtensible Interface,是Xilinx從6系列的FPGA開始引入的一個接口協議,主要描述了主設備和從設備之間的數據傳輸方式。在ZYNQ中繼續使用,版本是AXI4,所以我們經常會看到AXI4.0,ZYNQ內部設備都有AXI接口。其實AXI就是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)的一個部分,是一種高性能、高帶寬、低延遲的片內總線,也用來替代以前的AHB和APB總線。第一個版本的AXI(AXI3)包含在2003年發布的AMBA3.0中,AXI的第二個版本AXI(AXI4)包含在2010年發布的AMBA 4.0之中。

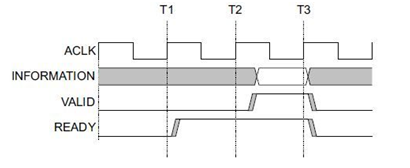

AXI協議主要描述了主設備和從設備之間的數據傳輸方式,主設備和從設備之間通過握手信號建立連接。當從設備準備好接收數據時,會發出READY信號。當主設備的數據準備好時,會發出和維持VALID信號,表示數據有效。數據只有在VALID和READY信號都有效的時候才開始傳輸。當這兩個信號持續保持有效,主設備會繼續傳輸下一個數據。主設備可以撤銷VALID信號,或者從設備撤銷READY信號終止傳輸。AXI的協議如圖,T2時,從設備的READY信號有效,T3時主設備的VILID信號有效,數據傳輸開始。

AXI握手時序圖

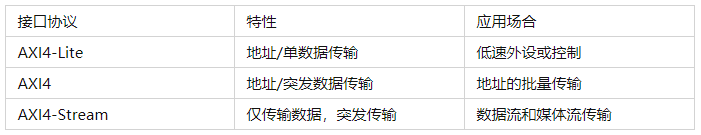

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,通過表5-1,我們可以看到這三種AXI接口的特性。

AXI4-Lite:

具有輕量級,結構簡單的特點,適合小批量數據、簡單控制場合。不支持批量傳輸,讀寫時一次只能讀寫一個字(32bit)。主要用于訪問一些低速外設和外設的控制。

AXI4:

接口和AXI-Lite差不多,只是增加了一項功能就是批量傳輸,可以連續對一片地址進行一次性讀寫。也就是說具有數據讀寫的burst功能。

上面兩種均采用內存映射控制方式,即ARM將用戶自定義IP編入某一地址進行訪問,讀寫時就像在讀寫自己的片內RAM,編程也很方便,開發難度較低。代價就是資源占用過多,需要額外的讀地址線、寫地址線、讀數據線、寫數據線、寫應答線這些信號線。

AXI4-Stream:

這是一種連續流接口,不需要地址線(很像FIFO,一直讀或一直寫就行)。對于這類IP,ARM不能通過上面的內存映射方式控制(FIFO根本沒有地址的概念),必須有一個轉換裝置,例如AXI-DMA模塊來實現內存映射到流式接口的轉換。AXI-Stream適用的場合有很多:視頻流處理;通信協議轉換;數字信號處理;無線通信等。其本質都是針對數值流構建的數據通路,從信源(例如ARM內存、DMA、無線接收前端等)到信宿(例如HDMI顯示器、高速AD音頻輸出,等)構建起連續的數據流。這種接口適合做實時信號處理。

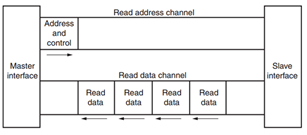

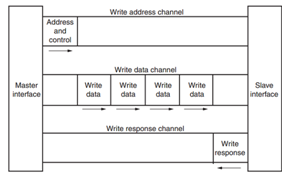

AXI4和AXI4-Lite接口包含5個不同的通道:

其中每個通道都是一個獨立的AXI握手協議。下面兩個圖分別顯示了讀和寫的模型:

AXI讀數據通道

AXI寫數據通道

在ZYNQ芯片內部用硬件實現了AXI總線協議,包括12個物理接口,分別為S_AXI_HP{0:3}_FPD,S_AXI_LPD,S_AXI_ACE_FPD,S_AXI_ACP_FPD,S_AXI_HPC{0,1}_FPD,M_AXI_HPM{0,1}_FPD,M_AXI_HPM0_LPD接口。

S_AXI_HP{0:3}_FPD接口,是高性能/帶寬的AXI4標準的接口,總共有四個,PL模塊作為主設備連接。主要用于PL訪問PS上的存儲器(DDR和FPD Main Switch)

S_AXI_LPD接口,高性能端口,連接PL到LPD。低延遲訪問OCM和TCM,訪問PS端DDR。

S_AXI_HPC{0,1}_FPD接口,連接PL到FPD,可連接到CCI,訪問L1和L2 Cache,由于通過CCI,訪問DDR控制器會有較大延遲。

M_AXI_HPM{0,1}_FPD接口,高性能總線,PS為master,連接FPD到PL,可用于CPU, DMA, PCIe等從PS推送大量數據到PL。

M_AXI_HPM0_LPD接口,低延遲接口總線,PS為master,連接LPD到PL,可直接訪問PL端的BRAM,DDR等,也經常用于配置PL端的寄存器。

只有M_AXI_HPM{0,1}_FPD和M_AXI_HPM0_LPD是Master Port,即主機接口,其余都是Slave Port(從機接口)。主機接口具有發起讀寫的權限,ARM可以利用兩個主機接口主動訪問PL邏輯,其實就是把PL映射到某個地址,讀寫PL寄存器如同在讀寫自己的存儲器。其余從機接口就屬于被動接口,接受來自PL的讀寫,逆來順受。在PS與PL互聯應用,用的最多的接口為S_AXI_HP{0:3}_FPD、M_AXI_HPM{0,1}_FPD和M_AXI_HPM0_LPD。

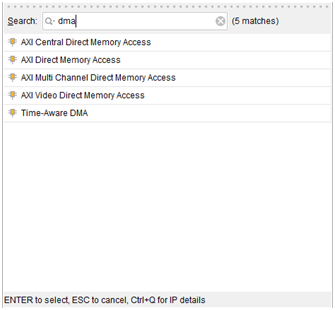

位于PS端的ARM直接有硬件支持AXI接口,而PL則需要使用邏輯實現相應的AXI協議。Xilinx在Vivado開發環境里提供現成IP如AXI-DMA,AXI-GPIO,AXI-Dataover, AXI-Stream都實現了相應的接口,使用時直接從Vivado的IP列表中添加即可實現相應的功能。下圖為Vivado下的各種DMA IP:

下面為幾個常用的AXI接口IP的功能介紹:

AXI-DMA:實現從PS內存到PL高速傳輸高速通道AXI-HPAXI-Stream的轉換

AXI-FIFO-MM2S:實現從PS內存到PL通用傳輸通道AXI-HPMAXI-Stream的轉換

AXI-Datamover:實現從PS內存到PL高速傳輸高速通道AXI-HPAXI-Stream的轉換,只不過這次是完全由PL控制的,PS是完全被動的。

AXI-VDMA:實現從PS內存到PL高速傳輸高速通道AXI-HPAXI-Stream的轉換,只不過是專門針對視頻、圖像等二維數據的。

AXI-CDMA:這個是由PL完成的將數據從內存的一個位置搬移到另一個位置,無需CPU來插手。

關于如何使用這些IP,我們會在后面的章節中舉例講到。有時,用戶需要開發自己定義的IP同PS進行通信,這時可以利用向導生成對應的IP。用戶自定義IP核可以擁有AXI4-Lite,AXI4,AXI-Stream,PLB和FSL這些接口。后兩種由于ARM這一端不支持,所以不用。

有了上面的這些官方IP和向導生成的自定義IP,用戶其實不需要對AXI時序了解太多(除非確實遇到問題),因為Xilinx已經將和AXI時序有關的細節都封裝起來,用戶只需要關注自己的邏輯實現即可。

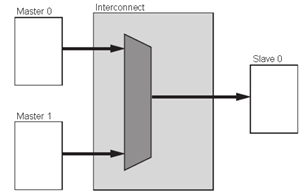

AXI協議嚴格的講是一個點對點的主從接口協議,當多個外設需要互相交互數據時,我們需要加入一個AXI Interconnect模塊,也就是AXI互聯矩陣,作用是提供將一個或多個AXI主設備連接到一個或多個AXI從設備的一種交換機制(有點類似于交換機里面的交換矩陣)。

這個AXI Interconnect IP核最多可以支持16個主設備、16個從設備,如果需要更多的接口,可以多加入幾個IP核。

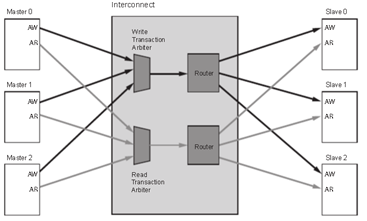

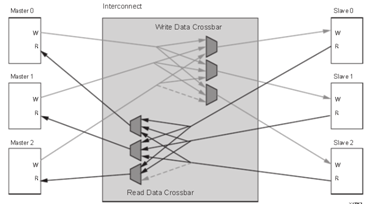

AXI Interconnect基本連接模式有以下幾種:

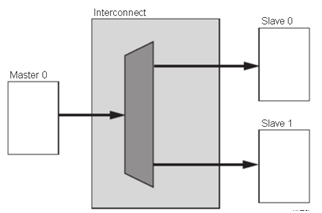

多對一的情況

一對多的情況

多對多讀寫地址通道

多對多讀寫數據通道

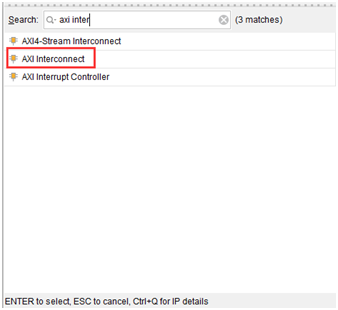

ZYNQ內部的AXI接口設備就是通過互聯矩陣的的方式互聯起來的,既保證了傳輸數據的高效性,又保證了連接的靈活性。Xilinx在Vivado里我們提供了實現這種互聯矩陣的IP核axi_interconnect,我們只要調用就可以。

AXI Interconnect IP

1.2 ZYNQ芯片開發流程的簡介

由于ZYNQ將CPU與FPGA集成在了一起,開發人員既需要設計ARM的操作系統應用程序和設備的驅動程序,又需要設計FPGA部分的硬件邏輯設計。開發中既要了解Linux操作系統,系統的構架,也需要搭建一個FPGA和ARM系統之間的硬件設計平臺。所以ZYNQ的開發是需要軟件人員和硬件硬件人員協同設計并開發的。這既是ZYNQ開發中所謂的"軟硬件協同設計”。

ZYNQ系統的硬件系統和軟件系統的設計和開發需要用到開發環境和調試工具:Xilinx Vivado。

Vivado設計套件實現FPGA部分的設計和開發,管腳和時序的約束,編譯和仿真,實現RTL到比特流的設計流程。Vivado并不是ISE設計套件的簡單升級,而是一個全新的設計套件。它替代了ISE設計套件的所有重要工具,比如Project Navigator、Xilinx Synthesis Technology、Implementation、CORE Generator、Constraint、Simulator、Chipscope Analyzer、FPGA Editor等設計工具。

Xilinx SDK(Software Development Kit), SDK是Xilinx軟件開發套件(SDK),在Vivado硬件系統的基礎上,系統會自動配置一些重要參數,其中包括工具和庫路徑、編譯器選項、JTAG和閃存設置,調試器連接已經裸機板支持包(BSP)。SDK也為所有支持的Xilinx IP硬核提供了驅動程序。SDK支持IP硬核(FPGA上)和處理器軟件協同調試,我們可以使用高級C或C++語言來開發和調試ARM和FPGA系統,測試硬件系統是否工作正常。SDK軟件也是Vivado軟件自帶的,無需單獨安裝。

ZYNQ的開發也是先硬件后軟件的方法。具體流程如下:

1) 在Vivado上新建工程,增加一個嵌入式的源文件。

2) 在Vivado里添加和配置PS和PL部分基本的外設,或需要添加自定義的外設。

3) 在Vivado里生成頂層HDL文件,并添加約束文件。再編譯生成比特流文件(*.bit)。

4) 導出硬件信息到SDK軟件開發環境,在SDK環境里可以編寫一些調試軟件驗證硬件和軟件,結合比特流文件單獨調試ZYNQ系統。

5) 在SDK里生成FSBL文件。

6) 在VMware虛擬機里生成u-boot.elf、 bootloader 鏡像。

7) 在SDK里通過FSBL文件, 比特流文件system.bit和u-boot.elf文件生成一個BOOT.bin文件。

8) 在VMware里生成Ubuntu的內核鏡像文件Zimage和Ubuntu的根文件系統。另外還需要要對FPGA自定義的IP編寫驅動。

9) 把BOOT、內核、設備樹、根文件系統文件放入到SD卡中,啟動開發板電源,Linux操作系統會從SD卡里啟動。

以上是典型的ZYNQ開發流程,但是ZYNQ也可以單獨做為ARM來使用,這樣就不需要關系PL端資源,和傳統的ARM開發沒有太大區別。ZYNQ也可以只使用PL部分,但是PL的配置還是要PS來完成的,就是無法通過傳統的固化Flash方式把只要PL的固件固化起來。

1.3 學習ZYNQ要具備哪些技能

學習ZYNQ比學習FPGA、MCU、ARM等傳統工具開發要求更高,想學好ZYNQ也不是一蹴而就的事情。

1.3.1 軟件開發人員

1.3.2 邏輯開發人員

- 采用Zynq UltraScale+ MPSoC滿足汽車ESD和SEED要求

- Zynq UltraScale+ MPSoC中的隔離方法應用筆記

- Zynq UltraScale+ MPSoC生產勘誤表

- Zynq UltraScale+ MPSoC數據手冊:DC和AC開關特性

- Zynq UltraScale+ MPSoC驗證數據手冊

- Zynq UltraScale+ MPSoC上的單芯片FIPS 140-3

- Zynq UltraScale+ MPSoC:軟件開發者指南

- Zynq UltraScale+ MPSoC中的隔離方法

- Zynq UltraScale+ MPSoC的隔離設計示例

- 適用于Xilinx Zynq UltraScale+ MPSoC應用的電源參考設計

- Zynq UltraScale ZU19EG MPSOC評估板 4次下載

- 米爾電子zynq ultrascale+ mpsoc底板外設資源清單分享

- 如何調試 Zynq UltraScale+ MPSoC VCU DDR 控制器?

- Zynq UltraScale MPSOC數據手冊免費下載 20次下載

- 如何使用Zynq UltraScale和MPSOC管理電源和性能資料說明 18次下載

- Xilinx ZYNQ UltraScale+系列產品介紹 2405次閱讀

- FPGAs,Zynq和Zynq MPSoC器件的特點 2275次閱讀

- 借助多功能Xilinx Zynq Ultrascale+ MPSoC加速計算密集型應用開發 1659次閱讀

- 基于Xilinx Zynq UltraScale+ RFSoC ZCU216評估套件詳細內容介紹 9162次閱讀

- 基于Xilinx Zynq ultraScale+ 系列FPGA的AXU2CGB 開發板評測 9051次閱讀

- 米爾科技HELLO WORLD主板介紹 2325次閱讀

- 米爾科技Zynq UltraScale+ MPSoC技術參考手冊介紹 2975次閱讀

- 詳解Xilinx公司Zynq? UltraScale+?MPSoC產品 3184次閱讀

- Xilinx Zynq UltraScale MPSoC可擴展電源設計 1950次閱讀

- Zynq UltraScale+ MPSoC ZCU102評估套件解決方案 8640次閱讀

- Enea OSE可實現對Xilinx UltraScale+ MPSoC的支持 2790次閱讀

- Xilinx基于ARM的Zynq-7000和Zynq UltraScale+ MPSoC及RFSoC器件是否存在安全漏洞 2620次閱讀

- Zynq UltraScale+ MPSoC 上的多個Linux UIO設計 3219次閱讀

- 用ZYNQ MPSoC玩DOOM! 2539次閱讀

- Ti推出面向Zynq UltraScale+ MPSoC的電源參考設計 3588次閱讀

下載排行

本周

- 1電子電路原理第七版PDF電子教材免費下載

- 0.00 MB | 1491次下載 | 免費

- 2單片機典型實例介紹

- 18.19 MB | 95次下載 | 1 積分

- 3S7-200PLC編程實例詳細資料

- 1.17 MB | 27次下載 | 1 積分

- 4筆記本電腦主板的元件識別和講解說明

- 4.28 MB | 18次下載 | 4 積分

- 5開關電源原理及各功能電路詳解

- 0.38 MB | 11次下載 | 免費

- 6100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

- 7基于單片機和 SG3525的程控開關電源設計

- 0.23 MB | 4次下載 | 免費

- 8基于AT89C2051/4051單片機編程器的實驗

- 0.11 MB | 4次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費

- 2PADS 9.0 2009最新版 -下載

- 0.00 MB | 66304次下載 | 免費

- 3protel99下載protel99軟件下載(中文版)

- 0.00 MB | 51209次下載 | 免費

- 4LabView 8.0 專業版下載 (3CD完整版)

- 0.00 MB | 51043次下載 | 免費

- 5555集成電路應用800例(新編版)

- 0.00 MB | 33562次下載 | 免費

- 6接口電路圖大全

- 未知 | 30320次下載 | 免費

- 7Multisim 10下載Multisim 10 中文版

- 0.00 MB | 28588次下載 | 免費

- 8開關電源設計實例指南

- 未知 | 21539次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935053次下載 | 免費

- 2protel99se軟件下載(可英文版轉中文版)

- 78.1 MB | 537793次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191183次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183277次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138039次下載 | 免費

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論