+:和-:符號(hào),Verilog標(biāo)準(zhǔn)文檔中的一個(gè)語(yǔ)法資料下載

資料介紹

動(dòng)態(tài)截取固定長(zhǎng)度數(shù)據(jù)語(yǔ)法,即+:和-:的使用,這兩個(gè)叫什么符號(hào)呢?運(yùn)算符嗎?

Verilog比較方便的一個(gè)特點(diǎn)就是數(shù)據(jù)的截取和拼接功能了,截取使用方括號(hào)[],拼接使用大括號(hào){},例如

reg?[7:0]?vect; wire?a; wire?[3:0]?b, wire?[5:0]?c; assign?a?=?vect[1];???????//取其中1Bit assign?b[3:0]?=?vect[7:4];//截取4Bit assing?c[5:0]?=?{a,?b[3:0],?1'b1};?//拼接

于是舉一反三(zi zuo cong ming),為了實(shí)現(xiàn)動(dòng)態(tài)截取固定長(zhǎng)度數(shù)據(jù)的功能,使用軟件編程的思維寫(xiě)了如下語(yǔ)句,功能很好理解,根據(jù)cnt的值,每次截取vect的5Bit數(shù)據(jù)。:

reg?[7:0]?vect; reg?[1:0]?cnt; wire?[4:0]?out; assign?out?=?vect[cnt+4:cnt];

一頓操作猛如虎,編譯一看傻如狗。使用ModelSim編譯之后,提示有如下語(yǔ)法錯(cuò)誤:

**?Error:?test.v(10):?Range?must?be?bounded?by?constant?expressions.

提示vect的范圍必須為常量表達(dá)式。也就是必須為,vect[6:2]或vect[7:4],不能是vect[a:0],vect[4:b],或vect[a:b]。額,這該怎么辦呢?

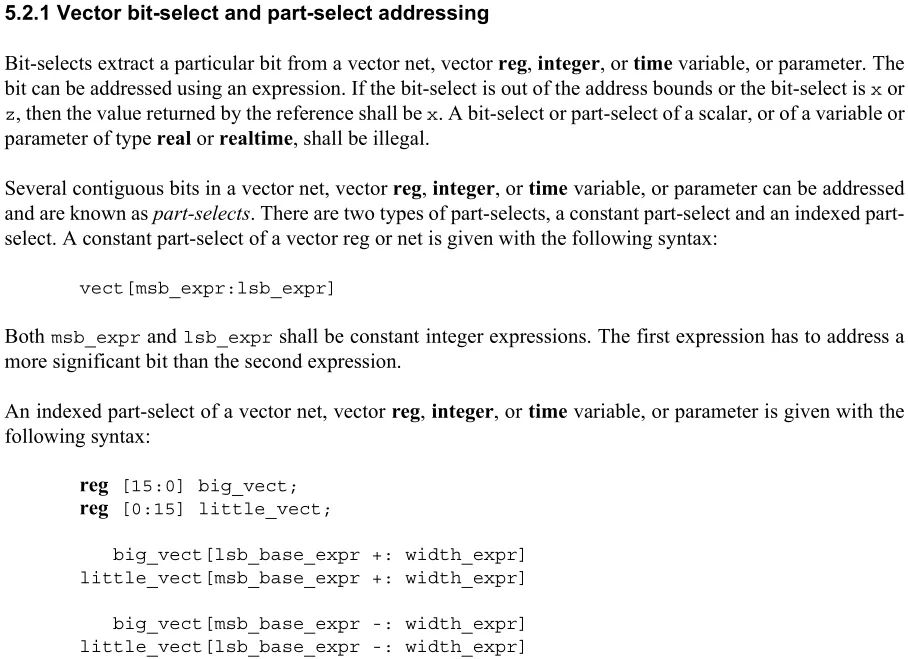

既然有這個(gè)使用場(chǎng)景,那Verilog在設(shè)計(jì)之初就應(yīng)該會(huì)考慮到這個(gè)應(yīng)用吧!于是就去翻IEEE的Verilog標(biāo)準(zhǔn)文檔,在5.2.1章節(jié)發(fā)現(xiàn)了一個(gè)用法可以實(shí)現(xiàn)我這個(gè)需求,那就是+:和-:符號(hào),這個(gè)用法很少,在大部分關(guān)于FPGA和Verilog書(shū)籍中都沒(méi)有提到。

(獲取IEEE官方Verilog標(biāo)準(zhǔn)文檔IEEE_Verilog_1364_2005.pdf下載,公眾號(hào)(ID:電子電路開(kāi)發(fā)學(xué)習(xí))后臺(tái)回復(fù)【Verilog標(biāo)準(zhǔn)】)

大致意思就是,可以實(shí)現(xiàn)動(dòng)態(tài)截取固定長(zhǎng)度的數(shù)據(jù),基本語(yǔ)法為:

vect[base+:width]或[base-:width]

其中base可以為變量,width必須為常量。

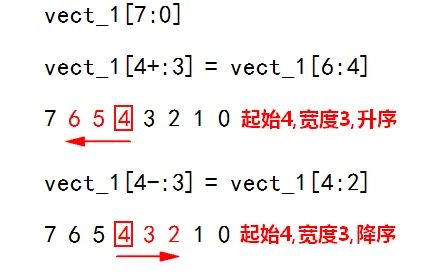

下面來(lái)舉幾個(gè)例子來(lái)理解這個(gè)符號(hào)。

有如下定義:

reg?[7:0]?vect_1; reg?[0:7]?vect_2; wire?[2:0]?out;

以下寫(xiě)法分別表示什么呢?

vect_1[4+:3]; vect_1[4-:3]; vect_2[4+:3]; vect_2[4-:3];

分為三步:

1.先看定義。

vect_1[7:0]定義是大端模式,則vect_1[4+:3]和vect_1[4-:3]轉(zhuǎn)換后也一定為大端模式;vect_2[0:7]定義是小端模式,則vect_2[4+:3]和vect_2[4-:3]轉(zhuǎn)換后也一定為小端模式。

2.再看升降序。

其中+:表示升序,-:表示降序

3.看寬度轉(zhuǎn)換。

vect_1[4+:3]表示,起始位為4,寬度為3,**升序**,則vect_1[4+:3]?=?vect_1[6:4] vect_1[4-:3]表示,起始位為4,寬度為3,**降序**,則vect_1[4-:3]?=?vect_1[4:2]

同理,

vect_2[4+:3]表示,起始位為4,寬度為3,升序,則vect_2[4+:3]?=?vect_2[4:6] vect_2[4-:3]表示,起始位為4,寬度為3,降序,則vect_2[4-:3]?=?vect_2[2:4]

ModelSim仿真驗(yàn)證,新建test.v文件:

module?test; ????reg?[7:0]?vect_1;? ????reg?[0:7]?vect_2; ????initial ????begin ????????vect_1?=?'b0101_1010; ????????vect_2?=?'b0101_1010; ????????$display("vect_1[7:0]?=?%b,?vect_2[0:7]?=?%b",?vect_1,?vect_2); ????????$display("vect_1[4+:3]?=?%b,?vect_1[4-:3]?=?%b",?vect_1[4+:3],?vect_1[4-:3]);? ????????$display("vect_2[4+:3]?=?%b,?vect_2[4-:3]?=?%b",?vect_2[4+:3],?vect_2[4-:3]);? ????????$stop; ????end endmodule

在ModelSim命令窗口輸入:

//進(jìn)入到源文件所在文件夾 cd?c:/users/whik/desktop/verilog //編譯 vlog?test.v //仿真 vsim?work.test //運(yùn)行 run?-all //運(yùn)行結(jié)果 #?vect_1[7:0]?=?01011010,?vect_2[0:7]?=?01011010 #?vect_1[4+:3]?=?101,?vect_1[4-:3]?=?110 #?vect_2[4+:3]?=?101,?vect_2[4-:3]?=?011 #?**?Note:?$stop????:?test.v(15) #????Time:?0?ps??Iteration:?0??Instance:?/test #?Break?in?Module?test?at?test.v?line?15

這種語(yǔ)法表示需要注意,前者起始位可以是變量,后者的寬度必須是常量,即vect[idx+:cnt]不符合語(yǔ)法標(biāo)準(zhǔn),vect[idx+:4]或vect[idx-:4]才符合。

- Verilog HDL入門(mén)教程-Verilog HDL的基本語(yǔ)法 170次下載

- Verilog語(yǔ)法進(jìn)階 30次下載

- Verilog的黃金參考指南資料免費(fèi)下載 24次下載

- Verilog黃金參考指南資料免費(fèi)下載 22次下載

- 可綜合的Verilog語(yǔ)法和語(yǔ)義詳細(xì)資料說(shuō)明 9次下載

- FPGA的Verilog學(xué)習(xí)教程課件免費(fèi)下載 14次下載

- 兩個(gè)運(yùn)動(dòng)員賽跑計(jì)時(shí)的秒表項(xiàng)目的verilog設(shè)計(jì)資料免費(fèi)下載 17次下載

- 基于Verilog硬件描述語(yǔ)言的IEEE標(biāo)準(zhǔn)硬件描述語(yǔ)言資料合集免費(fèi)下載 10次下載

- Verilog的學(xué)習(xí)PPT課件合集免費(fèi)下載 6次下載

- FPGA的語(yǔ)法注釋介紹資料免費(fèi)下載 2次下載

- LED流水燈的Verilog設(shè)計(jì)實(shí)例資料合集免費(fèi)下載 20次下載

- 有關(guān)Verilog中的一些語(yǔ)法詳細(xì)資料說(shuō)明 2次下載

- FPGA視頻教程之Verilog語(yǔ)法基礎(chǔ)的詳細(xì)資料說(shuō)明 16次下載

- arduino的一些常用函數(shù)語(yǔ)法資料免費(fèi)下載 19次下載

- SchLib的元件符號(hào)庫(kù)資料免費(fèi)下載 31次下載

- Verilog到VHDL轉(zhuǎn)換的經(jīng)驗(yàn)與技巧總結(jié) 1562次閱讀

- verilog中repeat必須用begin和end嗎 782次閱讀

- verilog task和function區(qū)別 688次閱讀

- verilog中數(shù)據(jù)的符號(hào)屬性(有符號(hào)數(shù)和無(wú)符號(hào)數(shù))探究根源 1070次閱讀

- verilog中有符號(hào)數(shù)和無(wú)符號(hào)數(shù)的本質(zhì)探究 749次閱讀

- 講一講芯片設(shè)計(jì)中的verilog是什么 932次閱讀

- Verilog語(yǔ)法之generate for、generate if、generate case 2453次閱讀

- Verilog比較方便的特點(diǎn) 635次閱讀

- 共享符號(hào)和局部符號(hào)的區(qū)別 1696次閱讀

- 關(guān)于verilog中的無(wú)符號(hào)數(shù)和有符號(hào)數(shù) 1.6w次閱讀

- 如何設(shè)計(jì)可綜合的Verilog代碼和應(yīng)該遵循什么原則 4333次閱讀

- 常見(jiàn)的Verilog行為級(jí)描述語(yǔ)法 1w次閱讀

- 關(guān)于Verilog語(yǔ)言標(biāo)準(zhǔn)層次問(wèn)題 4912次閱讀

- 關(guān)于verilog的學(xué)習(xí)經(jīng)驗(yàn)簡(jiǎn)單分享 2800次閱讀

- html文檔結(jié)構(gòu)基礎(chǔ)學(xué)習(xí) 1904次閱讀

下載排行

本周

- 1電子電路原理第七版PDF電子教材免費(fèi)下載

- 0.00 MB | 1491次下載 | 免費(fèi)

- 2單片機(jī)典型實(shí)例介紹

- 18.19 MB | 95次下載 | 1 積分

- 3S7-200PLC編程實(shí)例詳細(xì)資料

- 1.17 MB | 27次下載 | 1 積分

- 4筆記本電腦主板的元件識(shí)別和講解說(shuō)明

- 4.28 MB | 18次下載 | 4 積分

- 5開(kāi)關(guān)電源原理及各功能電路詳解

- 0.38 MB | 11次下載 | 免費(fèi)

- 6100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

- 7基于單片機(jī)和 SG3525的程控開(kāi)關(guān)電源設(shè)計(jì)

- 0.23 MB | 4次下載 | 免費(fèi)

- 8基于AT89C2051/4051單片機(jī)編程器的實(shí)驗(yàn)

- 0.11 MB | 4次下載 | 免費(fèi)

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費(fèi)

- 2PADS 9.0 2009最新版 -下載

- 0.00 MB | 66304次下載 | 免費(fèi)

- 3protel99下載protel99軟件下載(中文版)

- 0.00 MB | 51209次下載 | 免費(fèi)

- 4LabView 8.0 專業(yè)版下載 (3CD完整版)

- 0.00 MB | 51043次下載 | 免費(fèi)

- 5555集成電路應(yīng)用800例(新編版)

- 0.00 MB | 33562次下載 | 免費(fèi)

- 6接口電路圖大全

- 未知 | 30320次下載 | 免費(fèi)

- 7Multisim 10下載Multisim 10 中文版

- 0.00 MB | 28588次下載 | 免費(fèi)

- 8開(kāi)關(guān)電源設(shè)計(jì)實(shí)例指南

- 未知 | 21539次下載 | 免費(fèi)

總榜

- 1matlab軟件下載入口

- 未知 | 935053次下載 | 免費(fèi)

- 2protel99se軟件下載(可英文版轉(zhuǎn)中文版)

- 78.1 MB | 537793次下載 | 免費(fèi)

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費(fèi)

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費(fèi)

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費(fèi)

- 6電路仿真軟件multisim 10.0免費(fèi)下載

- 340992 | 191183次下載 | 免費(fèi)

- 7十天學(xué)會(huì)AVR單片機(jī)與C語(yǔ)言視頻教程 下載

- 158M | 183277次下載 | 免費(fèi)

- 8proe5.0野火版下載(中文版免費(fèi)下載)

- 未知 | 138039次下載 | 免費(fèi)

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問(wèn)

提問(wèn)  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評(píng)論