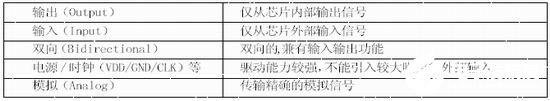

根據(jù) I/O 緩沖電路應(yīng)用目標(biāo)的不同,可將其分為輸入、輸出等幾類,詳見表 1。

表 1 I/O 緩沖電路的分類

?

輸出緩沖

輸出緩沖電路的功能要求能夠驅(qū)動大的片外負(fù)載,通常為 2~50pF,并且提供適當(dāng)?shù)纳仙?/ 下降時間。一組連續(xù)的大尺寸的緩沖器(buffer)對驅(qū)動能力的提高是有益的。大尺寸的管子容易受閂鎖效應(yīng)(latch-up)的影響,在版圖設(shè)計時建議采用保護(hù)環(huán)(Guardrings)保護(hù)以避免閂鎖效應(yīng),如圖 1-1 所示。在圖中,用 P+作為內(nèi)保護(hù)環(huán),而 N+作為外保護(hù)環(huán)(In n-well)。

?

圖 1-1 緩沖器

?

一種常見的輸出電路如圖 1-2 所示,En 是輸出電路的使能信號,Dout 是輸出數(shù)據(jù),MOS 管組合的功能如圖中所示。當(dāng) En 為低而 Dout 有效時,A、B 均為高電平,輸出 Y 為低,且由外向里看為高阻抗?fàn)顟B(tài),如果 Dout 未定,則 Y 為高阻。需要注意的是,最后輸出級的管子尺寸要大到能夠提供足夠的電流源或電流沉并且減少延遲時間。其負(fù)面影響是電流變化率(di/dt)變大而使穿過輸出點(diǎn)到封裝的壓焊線上的 L(di/dt)噪聲增大,從而導(dǎo)致較大的片上噪聲。

?

圖 1-2 常用的輸出緩沖電路

?

在高性能的芯片中,如 32 位的微處理器,如果多個 I/O 輸出驅(qū)動電路工作狀態(tài)相似時,L(di/dt)噪聲可能逐步增強(qiáng),會影響芯片速度。圖 1-3 通過加入一個閘控制信號(ST),并結(jié)合時序的控制,可以減小 L(di/dt)噪聲

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問

提問  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻

上傳資料賺積分

上傳資料賺積分

評論