資料介紹

描述

1. 背景

1A。概述

一個演示來說明:

(1) 創建/封裝用于 SoC 設計的可編程邏輯 (PL) 的定制 IP

(2) 從 SoC 處理器系統 (PS) 執行內存映射寄存器寫入/讀取操作

我在這里使用了一塊帶有 Zynq FPGA 的 MiniZed 板,但這些概念適用于任何 SoC 設計。雖然這些都是比較基礎的概念,但還是有很多的看家步驟和設置。我使用 Vivado/Vitis 2020.2,但早期版本的 Vivado/SDK 的步驟也應該非常相似。

根據需要使用下面的大綱跳過;大膽的步驟突出了關鍵的設計項目。

1B。大綱

一、概述

2. Vivado - SoC 項目設置

2A。新項目創建

2B。塊設計設置

2C。自定義 IP 設置:指定 AXI 接口和內存映射寄存器

3. Vivado - IP 編輯器項目

3A。Verilog Adder:加法器模塊的規范

3B。打包IP

4. Vivado - SoC 項目實施:在基礎項目中使用加法器

5. Vitis - 應用項目設置

5A。最初設定

5B。創建一個隨機數加法應用程序:C代碼和解釋

5C。運行應用程序:通過 UART 查看結果

六、分析與結論

2. Vivado - SoC 項目設置

2A。新項目創建

1) 打開 Vivado。點擊create a new project,給它一個名字(例如ps_pl_demo),然后點擊next。

2) RTL Project -> 不指定來源,點擊next。

3) 從 Boards 選項卡中選擇您的板*,單擊下一步,然后單擊完成。

* 對于首次設置,您可能需要開發套件的電路板定義文件。Minized位于“技術文檔”->“電路板定義文件”下。如果需要,下載并解壓縮該文件。開發板的頂級目錄(本例中為minized/ )必須復制您的 Vivado 安裝目錄(例如/home/user/Applications/Xilinx/Vivado/2020.2/data/boards/board_files/ )。

2B。塊設計設置

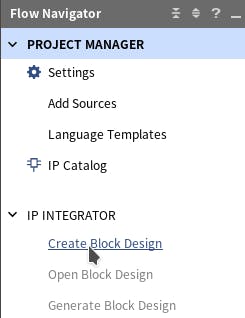

1) 完成 Vivado 的新項目 GUI 后,您將進入標準項目摘要頁面。從 Flow Navigator 窗格中單擊 Create Block Design。

2) 出現一個彈出窗口,要求輸入塊設計名稱:默認名稱就可以了。

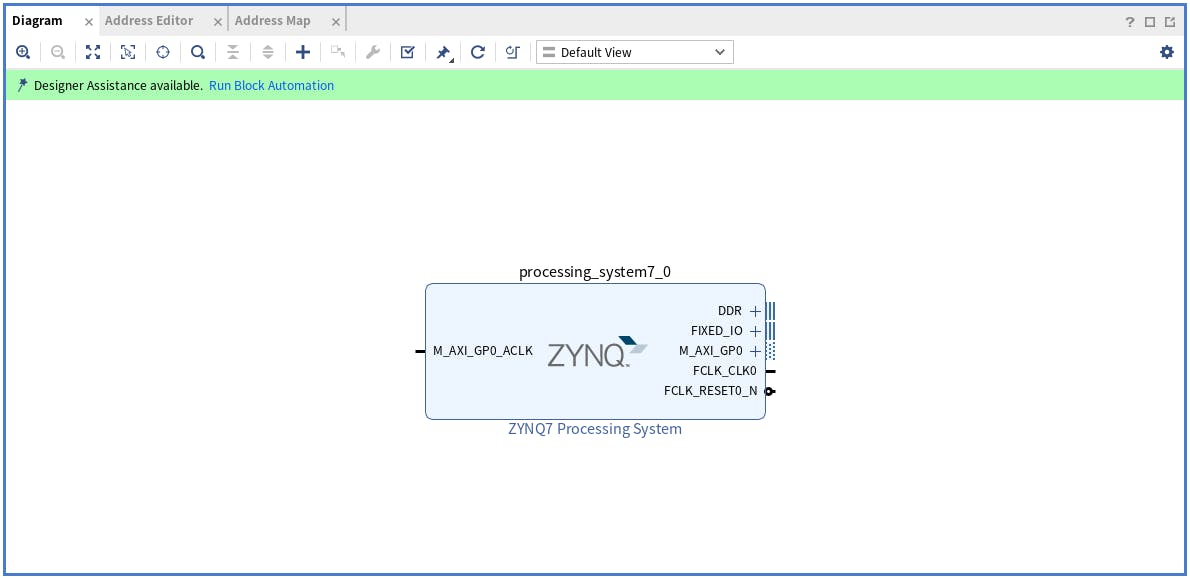

3) 現在出現“圖表”窗格。單擊“+”按鈕并在彈出菜單中雙擊“ZYNQ7 處理系統”。出現 PS 塊:

2C。自定義 IP 設置

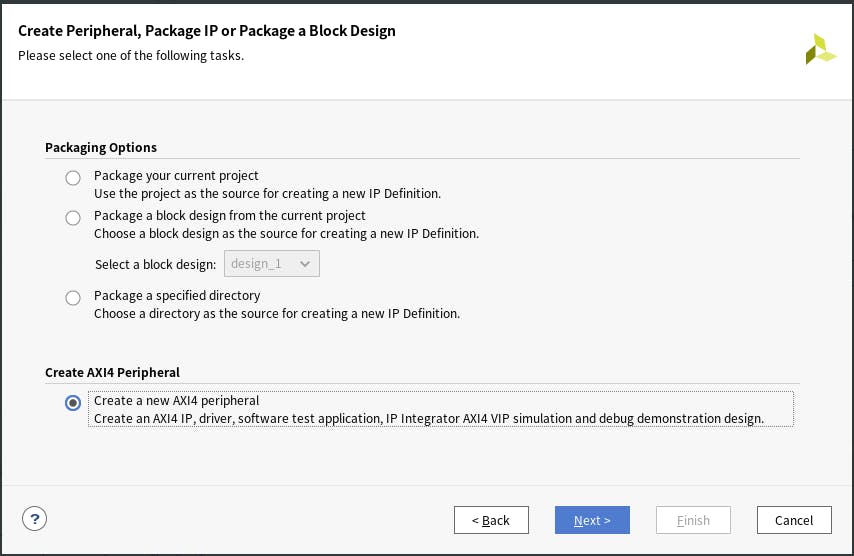

1) 現在,從頂部菜單欄中,單擊“工具 -> 創建和打包新 IP”。單擊下一步,然后在以下屏幕上單擊“創建新的 AXI4 外圍設備”并再次單擊下一步:

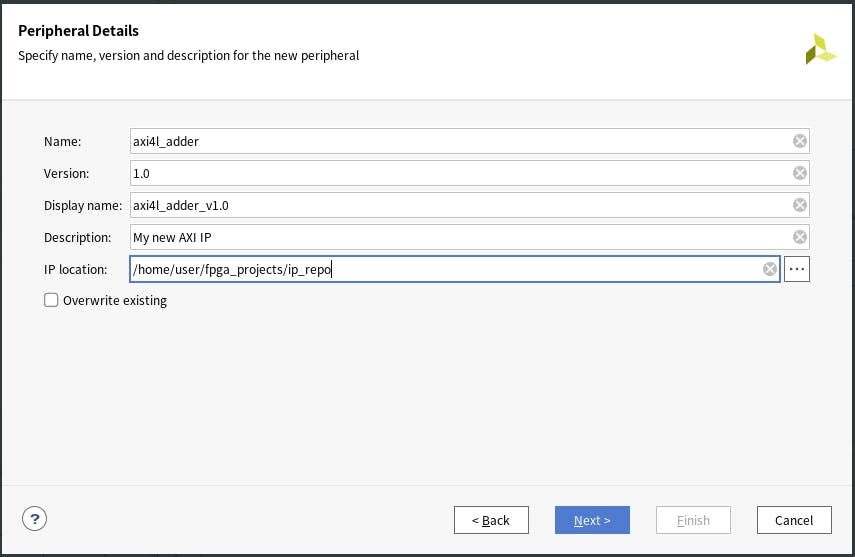

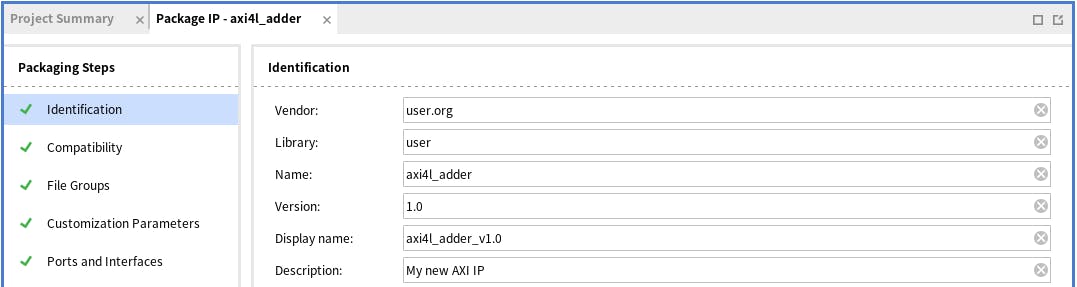

2) 在以下屏幕上,為 IP 命名。在這個演示中,我將展示一個簡單的加法器,所以我的 IP 名稱是axi4l_adder 。請注意底部字段中的目錄位置,我們將很快導航到那里:

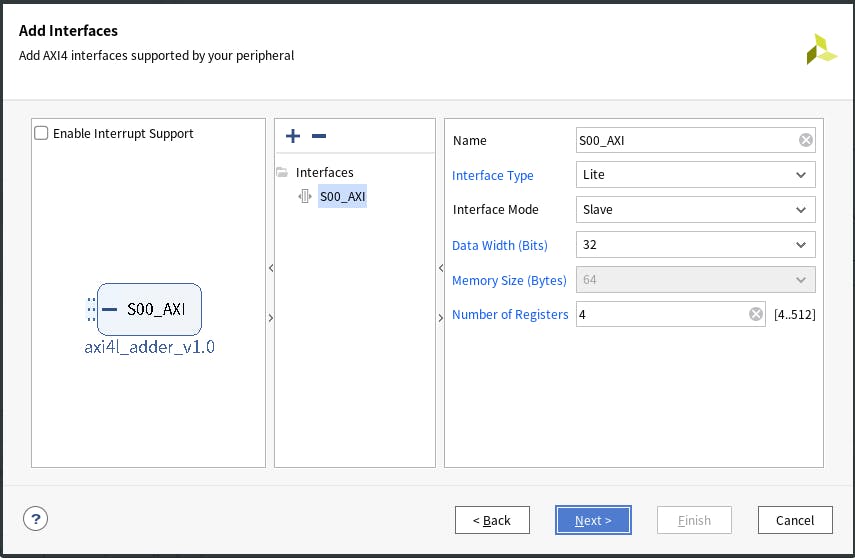

3)點擊下一步,出現如下頁面:

此演示的默認設置很好。它們將在 PL 中生成四個 32 位寄存器。4*32 = 128 位,因此 PS 將能夠在此 PL 模塊中尋址 16 字節的內存映射寄存器空間。

4) 單擊下一步并滾動到“下一步”部分。選擇“編輯 IP”,然后單擊完成。將打開一個新的 Vivado 項目。

3. Vivado - IP 編輯器項目

3A。Verilog 加法器

1) 我們將在這個新的 Vivado 項目中編輯axi4l_adder IP。默認窗格應包含所有先前的信息:

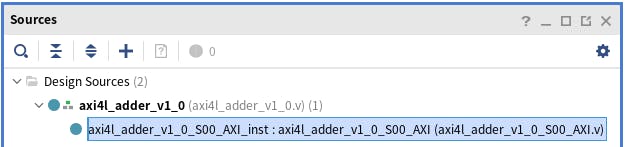

并且 Design Sources 窗格應該包含一些自動生成的 Verilog:

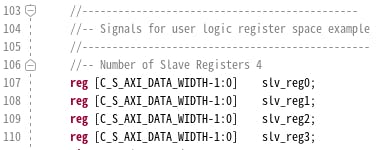

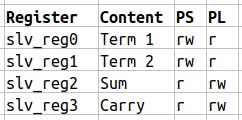

2) 雙擊axi4l_adder_v1_0_S00_AXI.v ,Vivado 將打開一個包含 HDL 源代碼的新選項卡。模塊 I/O 具有 AXI4-Lite 從接口的所有信號;不要碰。四個預期的寄存器位于 I/O 區域下方:

讓我們定義加法器的預期行為:

- slv_reg0 : 附加項 1,由 PS 編寫

- slv_reg1 : 加法項 2,由 PS 編寫

- slv_reg2 : 項 1 和 2 的總和,由 PL 計算

- slv_reg3 : 加法進位,由 PL 計算

所以我們定義他們的權限:

回到 Verilog 文件中,在 reg 聲明下方,有自動生成的進程有助于 AXI 信號發送以及寄存器寫入/讀取管理。我們需要做幾件事:(1) 防止 PS 寫入 slv_reg2 和 slv_reg3,(2) 計算和并進位 PL,(3) 將它們寫入 slv_reg2 和 slv_reg3。

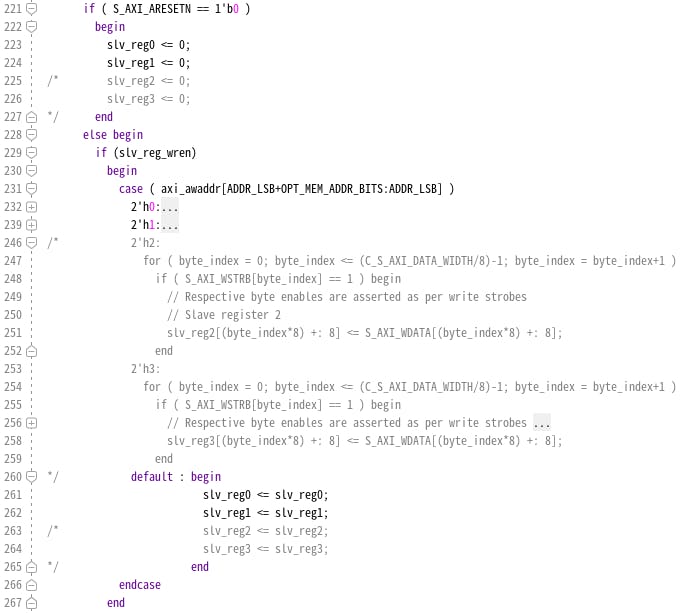

3) 為了防止 PS 寫入禁止的寄存器,我們必須更新管理內存映射寄存器寫入的專用進程。在第 210 行附近搜索注釋“// 實現內存映射寄存器選擇和寫入邏輯生成” 。注釋掉 slv_reg2 和 slv_reg3 分配,或完全刪除它們:

現在 PL 可以改為管理這些寄存器。

4) 返回到第 115 行左右。提供一種稱為sum的加法 reg 類型。它的大小將比slv_reg*信號大一位,以容納進位位。

reg [C_S_AXI_DATA_WIDTH-0:0] sum;

5) 現在,導航到文件底部(“ //在此處添加用戶邏輯”)。創建一個計算 reg0 和 reg1 之和的進程,然后寫入slv_reg2&3。

// Add user logic here

always @( posedge S_AXI_ACLK )

begin

if ( S_AXI_ARESETN == 1'b0 )

begin

sum <= 0;

slv_reg2 <= 0;

slv_reg3 <= 0;

end

else begin

sum <= slv_reg0 + slv_reg1;

slv_reg2 <= sum[$high(sum)-1:0]; // lower 32 bits

slv_reg3[0] <= sum[$high(sum)]; // top carry bit

end

end

// User logic ends

粘貼此代碼后按 Ctrl+E。在源文件屬性窗格中,將類型:Verilog 更改為類型:SystemVerilog。這對于使用諸如 $high() 之類的系統調用是必要的。

保存文件,讓我們把 IP 包起來。

3B。打包IP

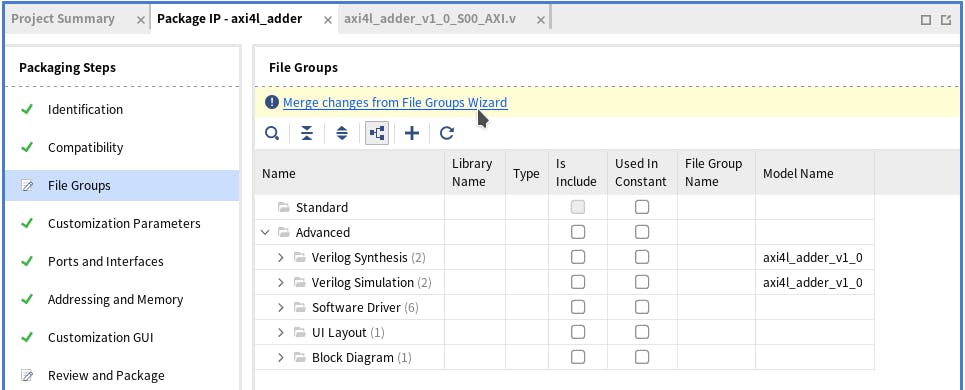

1) 返回“包 IP”選項卡。自從我們修改了 Verilog 源后,復選標記已從“文件組”部分中刪除。點擊“合并更改”:

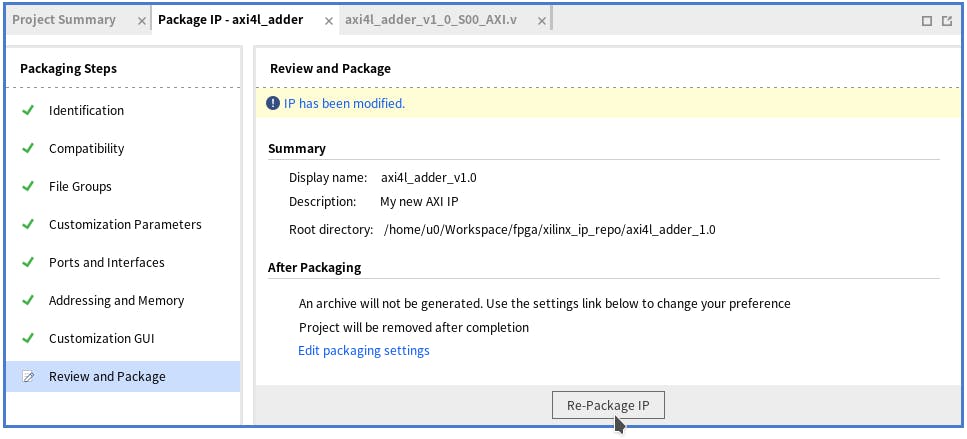

2) 現在在“Review”部分下,點擊“Re-package”:

3)現在應該出現一個彈出窗口;關閉 IP 項目并返回 SoC 項目。

4. Vivado - SoC 項目實施

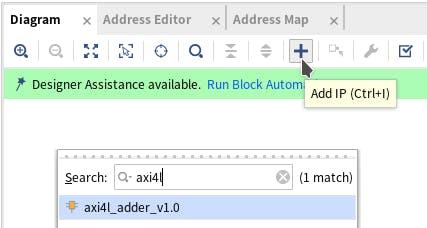

1) 回到 SoC 項目,我們可以使用新的 adder IP:

搜索 axi4l_adder,雙擊搜索結果,然后點擊“運行連接自動化”的綠色橫幅文本并使用默認設置。此步驟通過 AXI 互連模塊從 Zynq M_AXI_GP0 連接到加法器 IP。

然后單擊“運行塊自動化”并使用默認設置。這一步對于在軟件開發過程中使用 Zynq 的 UART1 接口是必要的。

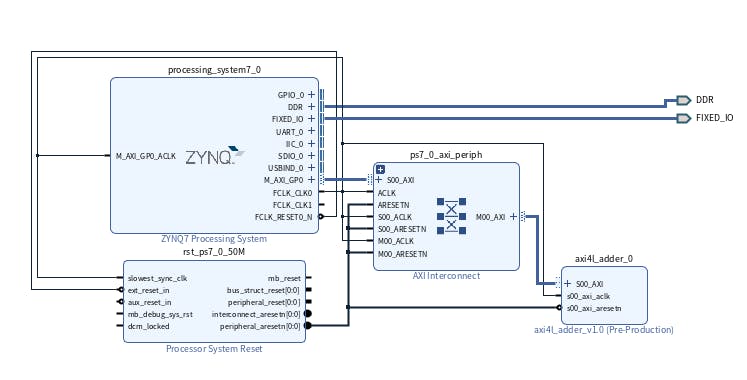

2) 模塊設計應填充 AXI 互連和復位管理器:

PS 的 M_AXI_GP0 應連接到 AXI 互連,互連的 M00_AXI 應連接到 AXI4L 加法器 IP。如果您在 PS 塊上看不到 M_AXI_GP0,則需要雙擊該塊并在“AXI Non Secure Enablement”下拉列表下的 PS-PL 配置選項卡上選擇“M AXI GP0 接口”。

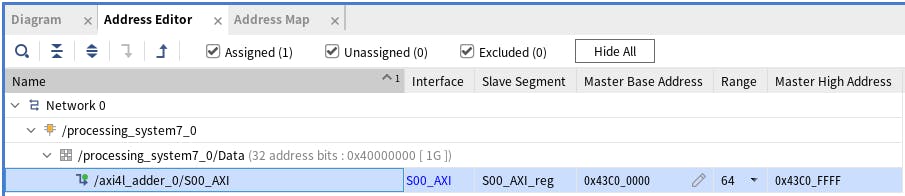

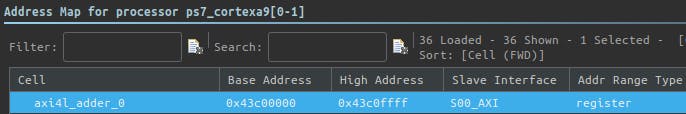

3) 在地址編輯器選項卡(“窗口”->“地址編輯器”)中,您應該看到列出的加法器 IP:

4) 按 F6 鍵驗證模塊設計。

5) 在 Sources 窗格中的 Design Sources 下,右鍵單擊 .bd 文件并選擇“Create HDL wrapper”->“Let Vivado manage and auto-update”。

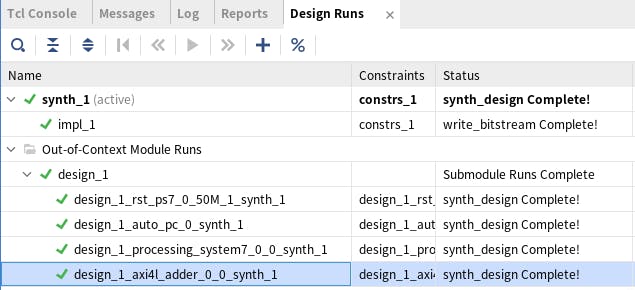

6) 點擊“Generate Bitstream”按鈕(或“Flow”->“Generate Bitstream”)讓綜合和實現運行。因為這是一個簡單的 PS 項目,所以不需要 Vivado 約束。在設計運行下,您將看到 OOC 運行下的加法器 IP:

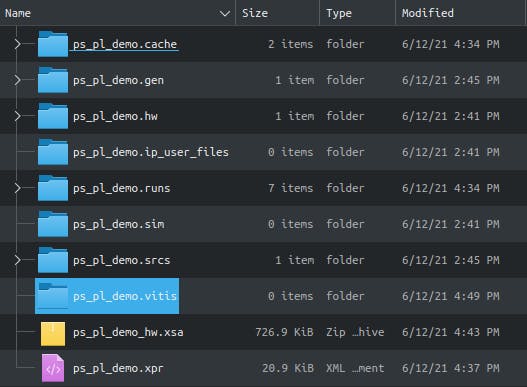

7) 一旦比特流生成完成,關閉彈出窗口并導航到“文件”->“導出”->“導出硬件”。在歡迎屏幕上點擊下一步。在以下屏幕上,選擇“包括比特流”。為硬件規范命名,并將其保存在 SoC 項目目錄中。輸出是在下面的 Vitis 中使用的 XSA 文件。

5. Vitis - 應用項目

5A。最初設定

1) [可選] 創建一個 Vitis 工作區文件夾(例如,在 SoC 項目文件夾中)。

2) 在 Vivado 中,點擊“工具”->“啟動 Vitis IDE”

3) Vitis 可以加載到歡迎屏幕,也可以在之前的工作區中開始。如果它從前一個工作區開始,點擊“文件”->“切換工作區”并指向新目錄[也是可選的]。

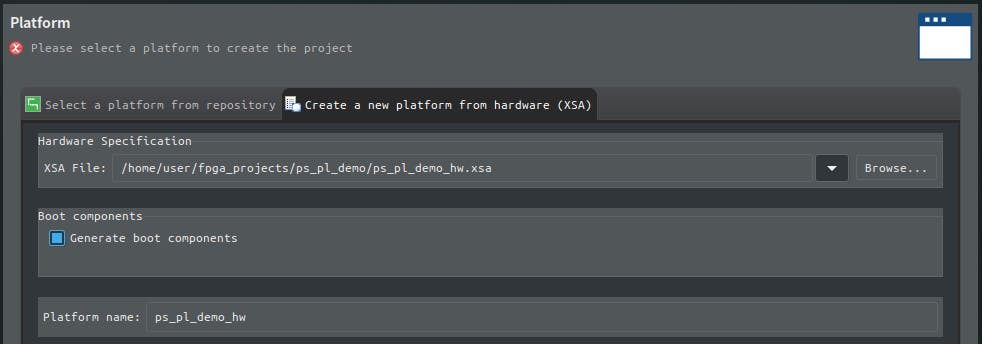

4) 單擊創建應用程序項目(“文件”->“新建”->“應用程序項目”)。在歡迎頁面點擊下一步。

5) 在平臺頁面上,單擊“從硬件創建新平臺 (XSA)”選項卡。現在瀏覽以選擇從 Vivado 導出的 XSA 文件。

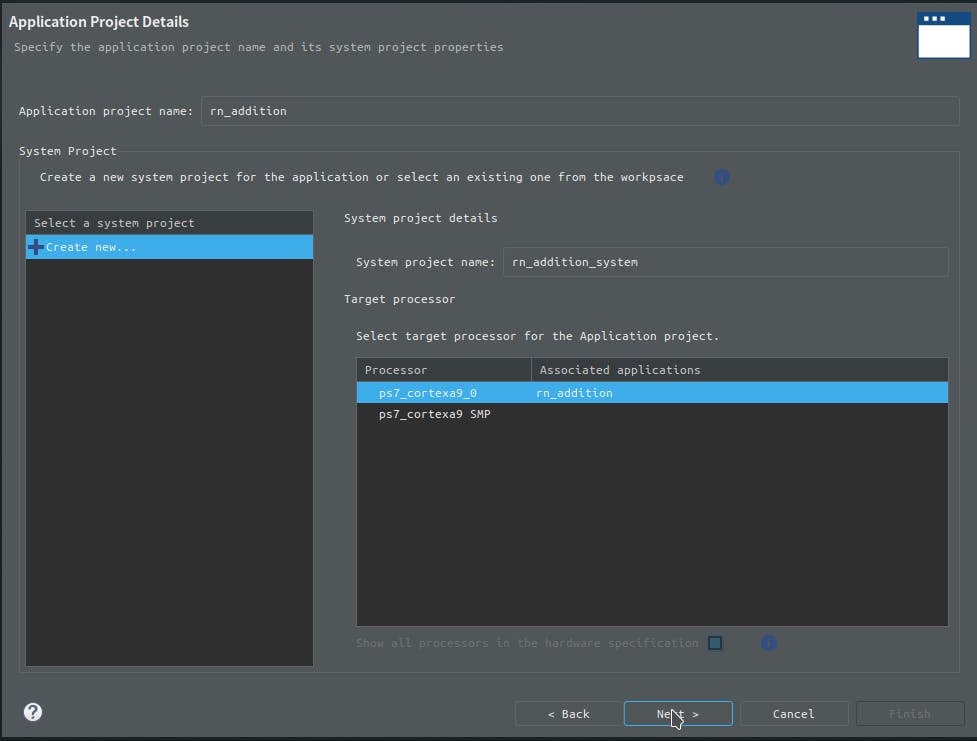

6)我們將添加一些隨機數。創建一個名為rn_addition的新應用程序項目,然后單擊 Next。

7)在下一頁“域”上,默認設置就可以了。

8) 在“模板”頁面上,選擇 Hello World 模板并點擊完成。

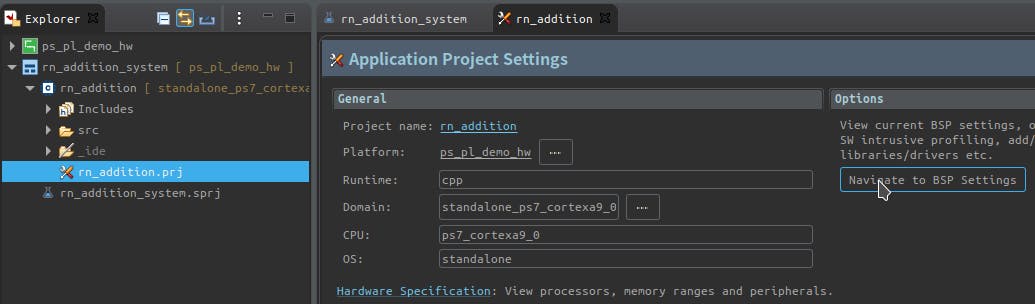

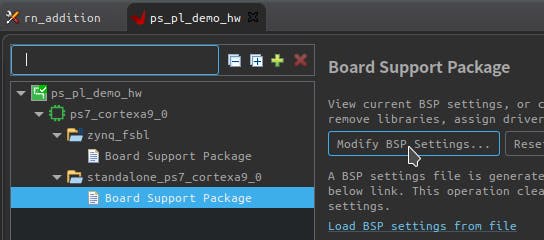

9) 現在在 Vitis 資源管理器中,選擇 Application Project settings entry (rn_addition.prj) 并單擊“Navigate to BSP settings”,

10) 現在點擊“修改 BSP 設置”:

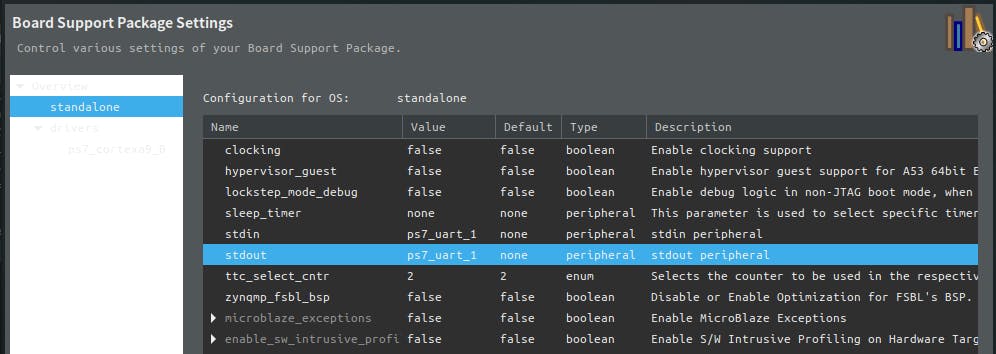

11) 在“Standalone”選項卡下,將 stdout 設置為 ps7_uart1。這可以使用 Zynq 的 UART 進行軟件打印。單擊確定并返回到應用程序項目設置選項卡。

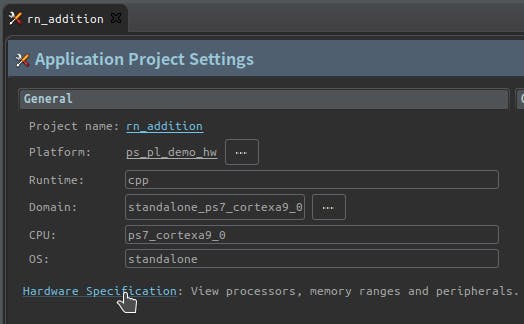

12) 在應用程序項目設置選項卡上,單擊硬件規格:

13) 在結果選項卡中,AXI4L 加法器應位于地址映射中:

5B。創建隨機數加法應用程序

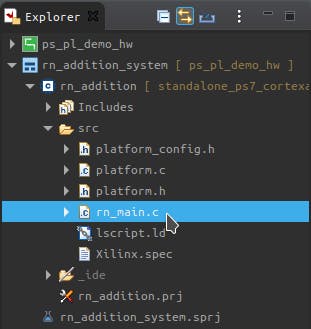

1) 現在我們可以做一些有用的事情了。在 Vitis 資源管理器窗格中,展開src 。將helloworld.c重命名為rn_main.c并雙擊進行編輯。

將 helloworld 代碼替換為以下內容:

// J. Abate '21

#include // for random number function

#include // for sleep function

#include "platform.h"

#include "xil_printf.h"

#include "xil_io.h"

#define ADDER_b 0x43C00000

#define REG_0_o 0x0

#define REG_1_o 0x4

#define REG_2_o 0x8

#define REG_3_o 0xC

int main()

{

init_platform();

print("\nps7_uart_1 @ 115200 baud\n\n\r");

// random numbers; bottom and top of range

u32 rn_lo = 0x40000000, rn_hi = 0xBFFFFFFF;

// register data

u16 test_count = 1;

u32 slv_reg0_wdata = 0xFFFFFFFF;

u32 slv_reg0_rdata;

u32 slv_reg1_wdata = 0x1;

u32 slv_reg1_rdata;

u32 slv_reg2_rdata;

u8 slv_reg3_rdata;

while(1)

{

xil_printf("test #%d\n\r", test_count);

// Write then read slv_reg0

Xil_Out32(ADDER_b + REG_0_o, slv_reg0_wdata);

slv_reg0_rdata = Xil_In32(ADDER_b + REG_0_o);

xil_printf("slv_reg0 [w]|[r] = 0x%08X | 0x%08X (%u) \n\r", slv_reg0_wdata, slv_reg0_rdata, slv_reg0_rdata);

// Write then read slv_reg1

Xil_Out32(ADDER_b + REG_1_o, slv_reg1_wdata);

slv_reg1_rdata = Xil_In32(ADDER_b + REG_1_o);

xil_printf("slv_reg1 [w]|[r] = 0x%08X | 0x%08X (%u) \n\r", slv_reg1_wdata, slv_reg1_rdata, slv_reg1_rdata);

// Read slv_reg2&3

slv_reg2_rdata = Xil_In32(ADDER_b + REG_2_o);

slv_reg3_rdata = Xil_In8(ADDER_b + REG_3_o);

xil_printf("sum [r] | c [r] = 0x%08X | 0x%01X (%u) \n\n\r", slv_reg2_rdata, slv_reg3_rdata, slv_reg2_rdata);

// update terms for next iteration and increment the test count

slv_reg0_wdata = ( rand() % (rn_hi - rn_lo + 1) ) + rn_lo;

slv_reg1_wdata = ( rand() % (rn_hi - rn_lo + 1) ) + rn_lo;

test_count += 1;

sleep(10);

}

cleanup_platform();

return 0;

}

2)代碼解釋。我包括以下文件:

- rand() 函數的 stdlib.h

- unistd.h 用于 sleep() 函數

- xil_io.h用于內存映射寄存器 R/W 函數 Xil_In() 和 Xil_Out()

然后我定義要使用的內存地址。Vivado 地址編輯器和 Vitis 地址映射在基址 0x43C00000(偏移量 0x0 到 0xFFFF)處為加法器 IP 保留 64KB 地址。

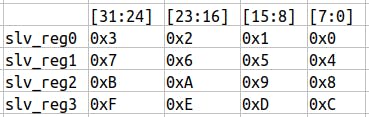

但是,請記住,加法器 IP 只有四個 32 位寄存器,總共 16 個字節(0x0 到 0xF):

- slv_reg0(偏移量 0x0 到 0x3):在此處寫入第一個加法項

- slv_reg1(偏移量 0x4 到 0x7):在此處寫入第二個加法項

- slv_reg2(偏移量 0x8 到 0xB):在此處讀取總和

- slv_reg3 (offsets 0xC to 0xF): 在這里讀取進位位

在 while(1) 循環中,Xil_Out() 和 Xil_In() 語句管理每個寄存器的寫入/讀取。

5C。運行應用程序

1) 返回 Vitis 資源管理器窗格,折疊所有展開的條目。突出顯示平臺項目和應用程序項目,然后右鍵單擊并點擊“構建項目”。構建完成后,點擊 Bug 按鈕旁邊的下拉菜單,然后單擊 Debug Configurations。

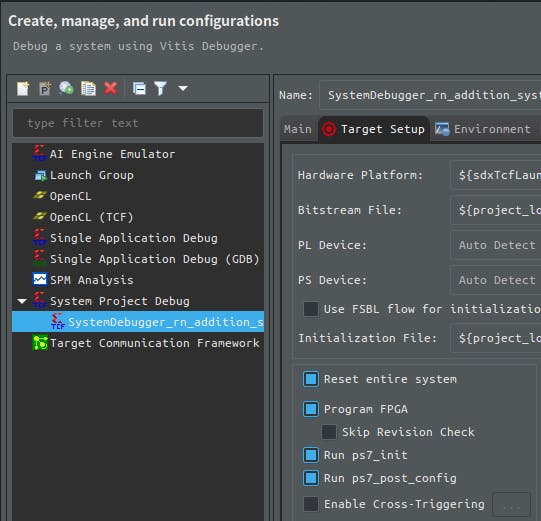

2) 在出現的彈出窗口中,雙擊“System Project Debug”并移動到 Target Setup 選項卡。確保選擇“Program FPGA”,然后點擊 Debug 關閉彈出窗口。

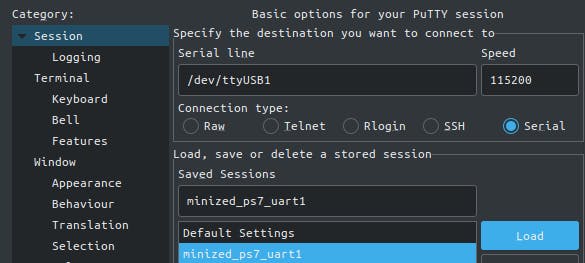

3) 現在,將 USB 電纜從計算機連接到 MiniZed 的 USB/JTAG/UART 端口。以 115200 波特率打開與 MiniZed UART 的串行會話:

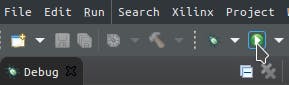

4) 回到 Vitis,點擊運行按鈕:

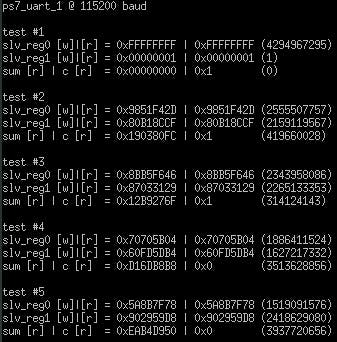

5) 在串行會話中,您應該會看到類似這樣的打印:

每個測試顯示以下內容:

- 測試ID#

- 寫入 slv_reg0 和 slv_reg1 的項,在每個等號的右側

- 從 slv_reg0 和 slv_reg1 讀取的術語位于每個管道符號的右側(括號中為無符號)。

- 從 slv_reg2 和 slv_reg3 讀回的總和和進位結果(括號中的無符號總和)。

第一個測試是硬編碼的,以顯示從進位寄存器成功讀取。隨后的測試是偽隨機的。

六、分析與結論

此演示展示了使用 PS 中的 Xil_In() 和 Xil_Out() 通過 AXI4-Lite 接口傳輸 PS-PL 數據。每當 PS 發出 Xil_Out() 以在 slv_reg0 或 slv_reg1 寫入新項時,PL總是更新 slv_reg0 和 slv_reg1 項的總和。

在 PS 寫入任一項之后的第一個時鐘周期,PL 計算新的總和。在第二個時鐘周期,它用和結果更新 slv_reg3,用進位結果更新 slv_reg4。與 Xil_Out32() 到 slv_reg1 和 slv_reg2 的 Xil_In32() 之間經過的時間相比,該延遲很小(兩個 FCLK_0 周期 = 40 ns)。從這個意義上說,此演示假定 PL 在 PS 讀取 slv_reg2 和 slv_reg3 時始終具有有效結果。

- ZMID4200 寄存器映射

- ZMID4200 寄存器映射

- STM32-寄存器地址名稱映射分析

- STM32F103系列芯片的地址和寄存器映射原理、LED輪流閃爍實現

- STM32F103系列芯片的地址映射和寄存器映射原理,GPIO端口的初始化

- UG-1168:AD9544寄存器映射參考手冊

- UG-1167:AD9543寄存器映射參考手冊

- UG-1146:AD9545寄存器映射參考手冊

- 寄存器的名稱和地址的映射詳細資料分析

- 如何進行寄存器名稱和地址的映射分析

- HELLODSP中F2812寄存器速查 12次下載

- 多寄存器Load/Store內存訪問指令 1次下載

- 移位寄存器及其應用實驗 22次下載

- 寄存器與移位寄存器

- 集成移位寄存器

- 寄存器和內存的區別 935次閱讀

- ARM通用寄存器及狀態寄存器詳解 6337次閱讀

- CPU、寄存器和內存單元的物理結構 3962次閱讀

- FPGAs,Zynq和Zynq MPSoC器件的特點 2275次閱讀

- ZYNQ7020的PS端的基本開發流程 7018次閱讀

- 寄存器與內存的區別 9939次閱讀

- 計算機中內存、cache和寄存器之間的關系 4874次閱讀

- 寄存器變量 2243次閱讀

- 寄存器比內存快的原理是什么? 5212次閱讀

- Linux驅動開發筆記:對zynq PL部分IP核的驅動開發過程 9483次閱讀

- zynq中PL部分的物理地址操作函數 6815次閱讀

- 逆向基礎之寄存器和內存詳解 2902次閱讀

- 為什么寄存器比內存快_原因是這個 6874次閱讀

- Zynq PS/ PL第五篇:Adam Taylor MicroZed系列之25 539次閱讀

- Zynq PS / PL 第四篇:Adam Taylor MicroZed系列之 24 1056次閱讀

下載排行

本周

- 1山景DSP芯片AP8248A2數據手冊

- 1.06 MB | 532次下載 | 免費

- 2RK3399完整板原理圖(支持平板,盒子VR)

- 3.28 MB | 339次下載 | 免費

- 3TC358743XBG評估板參考手冊

- 1.36 MB | 330次下載 | 免費

- 4DFM軟件使用教程

- 0.84 MB | 295次下載 | 免費

- 5元宇宙深度解析—未來的未來-風口還是泡沫

- 6.40 MB | 227次下載 | 免費

- 6迪文DGUS開發指南

- 31.67 MB | 194次下載 | 免費

- 7元宇宙底層硬件系列報告

- 13.42 MB | 182次下載 | 免費

- 8FP5207XR-G1中文應用手冊

- 1.09 MB | 178次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 2555集成電路應用800例(新編版)

- 0.00 MB | 33566次下載 | 免費

- 3接口電路圖大全

- 未知 | 30323次下載 | 免費

- 4開關電源設計實例指南

- 未知 | 21549次下載 | 免費

- 5電氣工程師手冊免費下載(新編第二版pdf電子書)

- 0.00 MB | 15349次下載 | 免費

- 6數字電路基礎pdf(下載)

- 未知 | 13750次下載 | 免費

- 7電子制作實例集錦 下載

- 未知 | 8113次下載 | 免費

- 8《LED驅動電路設計》 溫德爾著

- 0.00 MB | 6656次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935054次下載 | 免費

- 2protel99se軟件下載(可英文版轉中文版)

- 78.1 MB | 537798次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420027次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191187次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183279次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138040次下載 | 免費

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論