資料介紹

描述

我對本教程采用了快速入門的方法,即盡早開始編寫代碼。編寫代碼不需要對 FPGA 了解太多,就像你為 CPU 編寫軟件而沒有真正了解 CPU 的細節一樣。但是,FPGA 是一種資源受限的設備,在某些時候您會想了解這些資源是什么以及如何測量它們。今天,我們將仔細研究 FPGA 的組成部分,以便您可以做到這一點。

如果您是本系列的新手,您可能想回到硬件即代碼第 I 部分。

FPGA 元素

讓我們首先介紹 FPGA 內部的主要元素。

可編程邏輯- 這是 FPGA 中可用的主要和最豐富的資源。正如我在第一部分中所描述的,數字邏輯由邏輯門(與、或、非等)組成,該邏輯可用于實現算術運算,以及計算機所做的一切。可編程邏輯元件通常稱為 LE(邏輯元件)或 LUT。在最大的 FPGA 中,LE 容量可以從數百到超過一百萬不等。

寄存器- (非數組)變量的值存儲在由稱為觸發器的硬件元素組成的寄存器中。每個觸發器(或只是 FF)存儲一個位值,因此 8 位變量將在硬件中使用 8 個 FF。每個 LE 通常有一個或兩個 FF 配對,因此觸發器容量通常與 LE 的順序相同。

DSP 模塊——所謂的“數字信號處理”模塊主要由一個硬編碼(即固定功能,不可編程)乘法器和一個加法器組成。有幾種變體,但乘法器 + 加法器是所有變體共有的關鍵功能。盡管這兩者都可以純粹在可編程邏輯中實現,但 DSP 模塊的效率要高得多,而且它們對許多應用非常重要。DSP 塊數范圍從 10 以下到 1000 以上。

如果沒有足夠的 DSP 模塊可用,綜合工具將為乘法器和加法器使用可編程邏輯。這對于加法器來說很常見,雖然效率較低,但它們仍然相當有效。另一方面,乘法器作為可編程邏輯非常浪費,如果您需要許多乘法器超出可用 DSP 模塊的數量,您可能會發現自己很快就會耗盡空間。

嵌入式 RAM - 我們在第四部分詳細介紹了嵌入式 RAM。這些元素通常被稱為 EBR(嵌入式 RAM)、塊 RAM 或 BRAM。每個嵌入式 RAM 的容量通常以數千位為單位。嵌入式 RAM 的數量可能從幾萬到幾千不等。一些 FPGA 在同一個 FPGA 中也有多種尺寸。例如,許多較小的 RAM 和一些大型 RAM。

I/O - 這些重要的元件使用芯片的外部引腳提供輸入和輸出。在本系列中,我們不會過多擔心這些,因為我們將始終使用 HLS 工具中內置的預先設計的塊,將我們的設計與外部世界連接起來。但是,只是為了完整性... I/O 元素包括通用 I/O(或 GPIO),可以驅動具有高/低輸出值的引腳或讀取高/低輸入值。除了 GPIO,FPGA 通常還提供其他固定功能 I/O 元件,這些元件可以使用 DDR、SPI、I2C、PCIe 等特定協議與外部設備進行通信。

FPGA 規格

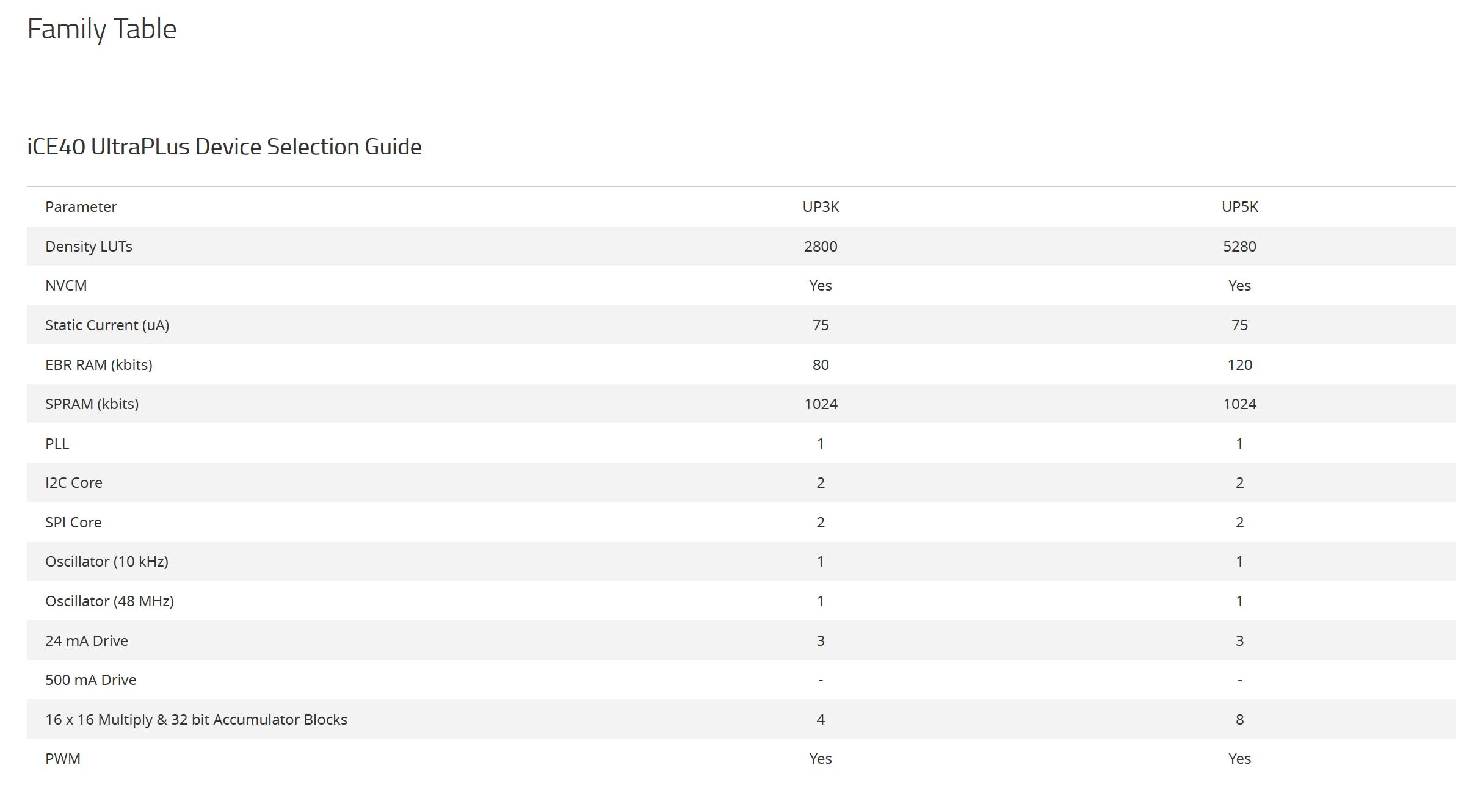

幾乎所有 FPGA 供應商都提供不同系列的 FPGA,它們針對不同類別的應用,稱為器件系列。每個系列將包括幾個不同尺寸的部件(無論是在物理上還是在可用資源方面)、封裝和特殊功能。當您訪問設備系列的網站時,頁面上或附件中將有一個系列表,其中總結了系列中每個設備的可用資源。

這是我們正在使用的 UPDuino 板上 FPGA 的族表:

希望您現在可以確定我們感興趣的 4 個主要資源(實際上是 3 個,因為缺少一個)。UPDuino 包含一個 UP5K 設備(第二列),因此我們的開發板有以下資源:

- 可編程邏輯:5、280個元素(表中的LUT)

- 寄存器:未明確給出,但假設類似于 LUT 計數(數據表將提供更多詳細信息。)

- 嵌入式 RAM:120Kb(這是總位容量。數據表將詳細說明各個塊的數量和大小。)

- DSP 塊:8 個(表中的乘法和累加器塊)

作為獎勵,這些芯片有一些更大的塊 RAM(表中的 SPRAM)。

即使您不了解文檔其余部分的大部分內容,通常也值得查看數據表的前幾頁。在概述之后,通常會有一個比您在網站上找到的更詳細的家庭表。

查看 UP5K 設備的數據表(下載數據表),我們發現它有 30 個嵌入式 RAM,每個 4096 位 (30 * 4Kb = 120Kb),以及 4 個 256Kb (4 * 256Kb = 1Mb) 的大 RAM 塊。

路由(隱藏資源)

在將設計映射到數字邏輯(和 DSP 模塊等)之后,工具必須在芯片上布局這些元素。在幾何上不可能以一種一切都與它們所連接的事物直接相鄰的方式來布局設計。因此,存在“路由”資源,這些資源基本上是電線和可編程開關,允許連接芯片的不同部分。

不幸的是,這是一種難以定量描述的資源。因此,您不會在 FPGA 規范中看到任何數字來描述可用的布線(不過,數據表可能會有對布線架構的描述),并且工具很少或根本沒有關于設計布線多少的輸出正在利用。充其量,您可能會看到這樣的警告,例如這種設計具有高度擁塞。

在實踐中,布線并不是您會直接擔心的事情,但它會影響最大可實現的芯片容量。未使用的邏輯和其他元素越多,布局的靈活性就越大,工具就越有可能找到可行的布局。反過來說,您使用的資源百分比越高,布局的靈活性就越小,工具就越有可能無法找到可行的布局。

我發現一旦 FPGA 的利用率達到 70-75%,這些工具可能會在布局期間開始出現問題。一旦達到 80% 或更多,您可能會遇到徹底的失敗。這只是我的經驗,YMMV。此時,簡單的解決方案是升級到更大的 FPGA。可以做一些事情來突破設備利用率的極限,但這些事情超出了本系列的水平,需要數字硬件設計師的幫助。

資源使用報告

現在您至少了解了最重要的感興趣的資源,我們現在可以查看工具報告,告訴我們我們的設計正在使用多少資源。當您單擊上傳按鈕構建您的設計并將其上傳到 FPGA 時,您會看到大量信息飛過,包括資源使用信息。您也可以運行這些工具,而無需使用以下命令實際上傳到 UPDuino 板:(pio run --target bitstream如果之前構建了比特流,您可能需要先清理項目)。

工具完成后,向后滾動幾頁,直到看到如下所示的表格:

Info: Device utilisation:

Info: ICESTORM_LC: 544/ 5280 10%

Info: ICESTORM_RAM: 0/ 30 0%

Info: SB_IO: 6/ 96 6%

Info: SB_GB: 4/ 8 50%

Info: ICESTORM_PLL: 0/ 1 0%

Info: SB_WARMBOOT: 0/ 1 0%

Info: ICESTORM_DSP: 1/ 8 12%

Info: ICESTORM_HFOSC: 1/ 1 100%

Info: ICESTORM_LFOSC: 0/ 1 0%

Info: SB_I2C: 0/ 2 0%

Info: SB_SPI: 0/ 2 0%

Info: IO_I3C: 0/ 2 0%

Info: SB_LEDDA_IP: 0/ 1 0%

Info: SB_RGBA_DRV: 0/ 1 0%

Info: ICESTORM_SPRAM: 0/ 4 0%

這是布局工具的輸出。第一行使用另一個術語來表示邏輯元件:LC(邏輯單元),即 LUT + FF。之后是嵌入式 RAM,再往下是 DSP。

這個實際輸出來自我們在第二部分的第一個示例:Hello FPGA。這種設計只使用了 10% 的 LE 資源,因此有足夠的空間來做更多的事情。事實上,這 10% 的大部分實際上是由工具產生的開銷,用于將你的函數連接到 USB,因此我們可以從計算機調用它。

要進行實驗,請使用我們介紹過的任何示例,并嘗試對代碼進行各種更改,以查看此使用情況報告表如何更改。5K 并不多,但我已經使用此設備構建了許多復雜的應用程序,例如喚醒詞檢測和圖像分類。

感知器挑戰

在第四部分中,我要求您修改多類感知器示例以并行計算 3 個輸出。這是該問題的解決方案:

// Multi-class perceptron is a matrix/vector multiplication

void mat_vec_mul(in_array,4> features, out_array,4> out) {

int16_t coef0[4] = { -9, 25, -28, -27 };

int16_t coef1[4] = { -3, -31, 58, -31 };

int16_t coef2[4] = { -10, 4, 80, 79 };

int16_t acc0 = 0;

int16_t acc1 = 0;

int16_t acc2 = 0;

for (uint8_t j = 0; j < 4; j++) {

int16_t x = features[j];

acc0 += coef0[j] * x;

acc1 += coef1[j] * x;

acc2 += coef2[j] * x;

}

out.resize(3); // set the actual output size

out[0] = acc0;

out[1] = acc1;

out[2] = acc2;

}

解決方案的關鍵是利用每個嵌入式 RAM 以及數組變量可以同時并行訪問這一事實。通過將coef 變量拆分為三個單獨的變量并展開外部循環,我們可以使每個輸出的乘法和累加步驟并行發生。如果我們展開了循環,但沒有拆分coef,那么工具鏈仍然會為三個乘法和加法語句生成單獨的硬件,但它們需要輪流從coef 數組中獲取值而不是實際執行在平行下。如所寫,上述循環每次迭代將使用 2 個周期:一個用于讀取數組,一個用于執行乘法和累加。幾周后,我們將了解如何將其進一步改進為每次迭代 1 個周期。

這是此示例的資源使用情況:

Info: Device utilisation:

Info: ICESTORM_LC: 686/ 5280 12%

Info: ICESTORM_RAM: 2/ 30 6%

Info: SB_IO: 6/ 96 6%

Info: SB_GB: 8/ 8 100%

Info: ICESTORM_PLL: 0/ 1 0%

Info: SB_WARMBOOT: 0/ 1 0%

Info: ICESTORM_DSP: 3/ 8 37%

Info: ICESTORM_HFOSC: 1/ 1 100%

Info: ICESTORM_LFOSC: 0/ 1 0%

Info: SB_I2C: 0/ 2 0%

Info: SB_SPI: 0/ 2 0%

Info: IO_I3C: 0/ 2 0%

Info: SB_LEDDA_IP: 0/ 1 0%

Info: SB_RGBA_DRV: 0/ 1 0%

Info: ICESTORM_SPRAM: 0/ 4 0%

正如預期的那樣,此設計使用 3 個 DSP 模塊,每個輸出一個。但是,您可能想知道為什么只使用了 2 個嵌入式 RAM 塊,盡管該函數使用了 5 個數組。在某些情況下,如果數組非常小,綜合工具可能會使用觸發器來存儲數組數據,而不是使用嵌入式 RAM。這里的系數數組總共只有 64 位,將其存儲在 4096 RAM 中會有些浪費。

下一步

本教程系列的前半部分到此結束,我希望您現在對如何使用 C++ 創建自定義 FPGA 設計有一個基本概念。但是,還有很多東西要學!接下來,我們將討論另一個性能優化主題:如何消除(或至少隱藏)I/O 開銷。

連接

在我發布新的分期付款時,請關注我以保持最新狀態。還有一個 Discord 服務器(公共聊天平臺),用于您在https://discord.gg/3sA7FHayGH上可能有的任何評論、問題或討論

- 硬件即代碼第三部分:空間與時間

- 硬件即代碼第四部分:嵌入式RAM

- 《Eric S. Raymond五部曲》pdf 0次下載

- 單片機匯編語言編程,《單片機原理及接口技術》,單片機考研,期末匯編考試寶典,《單片機原理及應用》,第一版,單片機匯編考研(初試或復試考試題) 0次下載

- ADC和DAC基礎 (共五部分,完整版) 0次下載

- 安信Windows驅動開發教程第五部分 16次下載

- 什么是低壓降穩壓器(LDO)的壓降? - 第五部分

- 自動控制原理第五章_頻域分析法_Part1部分 0次下載

- 自動控制原理第五章_頻域分析法_Part2部分 0次下載

- 自動控制原理第五章_頻域分析法_Part3部分 0次下載

- MATLAB仿真在現代通信中的應用_部分1 2次下載

- MATLAB信號處理詳解_部分5 16次下載

- ADC和DAC基礎 (共五部分,完整版) 0次下載

- 火力發電廠水汽分析方法 第五部分:酸度的測定

- USB開發指導內部資料

- fpga語言是什么?fpga語言與c語言的區別 723次閱讀

- 代碼即注釋,注釋即代碼的概念是如何形成的 597次閱讀

- 3D結構光內部硬件拆解 665次閱讀

- SystemVerilog在硬件設計部分有哪些優勢 925次閱讀

- 雙極踏腳車(第二部分):微步和衰減模式 461次閱讀

- 代碼質量如何影響企業的投資回報率 484次閱讀

- 使用安森美新型SiC模塊構建25kW快速電動汽車充電樁 2859次閱讀

- 了解FPGA的芯片內部資源:IO是什么 1w次閱讀

- 實時數據體系建設的總體方案的三部分 6598次閱讀

- 半導體器件型號的命名方法和半導體二極管參數符號及其意義說明 1.9w次閱讀

- FPGA的工作原理以及內部結構 2.5w次閱讀

- FPGA的幾點重要總結 4020次閱讀

- 關于如何「訓練」神經網絡的一部分經驗與見解 7450次閱讀

- 用純硬件解決方案加速部分重配置進程 1660次閱讀

- 混合信號系統接地揭秘之第二部分 1663次閱讀

下載排行

本周

- 1山景DSP芯片AP8248A2數據手冊

- 1.06 MB | 532次下載 | 免費

- 2RK3399完整板原理圖(支持平板,盒子VR)

- 3.28 MB | 339次下載 | 免費

- 3TC358743XBG評估板參考手冊

- 1.36 MB | 330次下載 | 免費

- 4DFM軟件使用教程

- 0.84 MB | 295次下載 | 免費

- 5元宇宙深度解析—未來的未來-風口還是泡沫

- 6.40 MB | 227次下載 | 免費

- 6迪文DGUS開發指南

- 31.67 MB | 194次下載 | 免費

- 7元宇宙底層硬件系列報告

- 13.42 MB | 182次下載 | 免費

- 8FP5207XR-G1中文應用手冊

- 1.09 MB | 178次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 2555集成電路應用800例(新編版)

- 0.00 MB | 33566次下載 | 免費

- 3接口電路圖大全

- 未知 | 30323次下載 | 免費

- 4開關電源設計實例指南

- 未知 | 21549次下載 | 免費

- 5電氣工程師手冊免費下載(新編第二版pdf電子書)

- 0.00 MB | 15349次下載 | 免費

- 6數字電路基礎pdf(下載)

- 未知 | 13750次下載 | 免費

- 7電子制作實例集錦 下載

- 未知 | 8113次下載 | 免費

- 8《LED驅動電路設計》 溫德爾著

- 0.00 MB | 6656次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935054次下載 | 免費

- 2protel99se軟件下載(可英文版轉中文版)

- 78.1 MB | 537798次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420027次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191187次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183279次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138040次下載 | 免費

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論