資料介紹

描述

目標:該項目的主要目標是展示高級綜合設計流程在實現數字系統中的能力和能力。

由于這是我在 hackster 中的第一個項目,因此我嘗試逐步解釋所有細節。如果您有興趣學習高級合成技術來設計數字系統,請參閱此處。

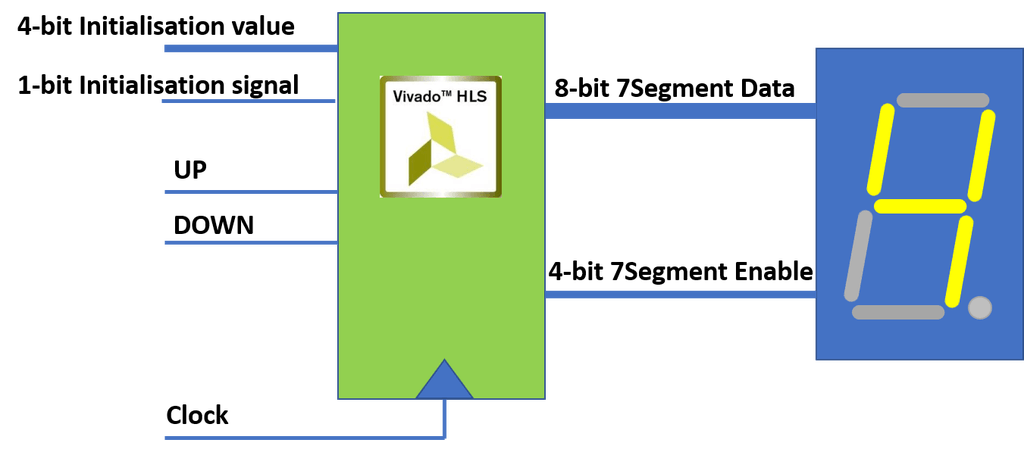

項目描述:在這個項目中,我將設計一個帶有初始化信號的 0-9 加/減計數器。圖 1 顯示了該項目的概覽。

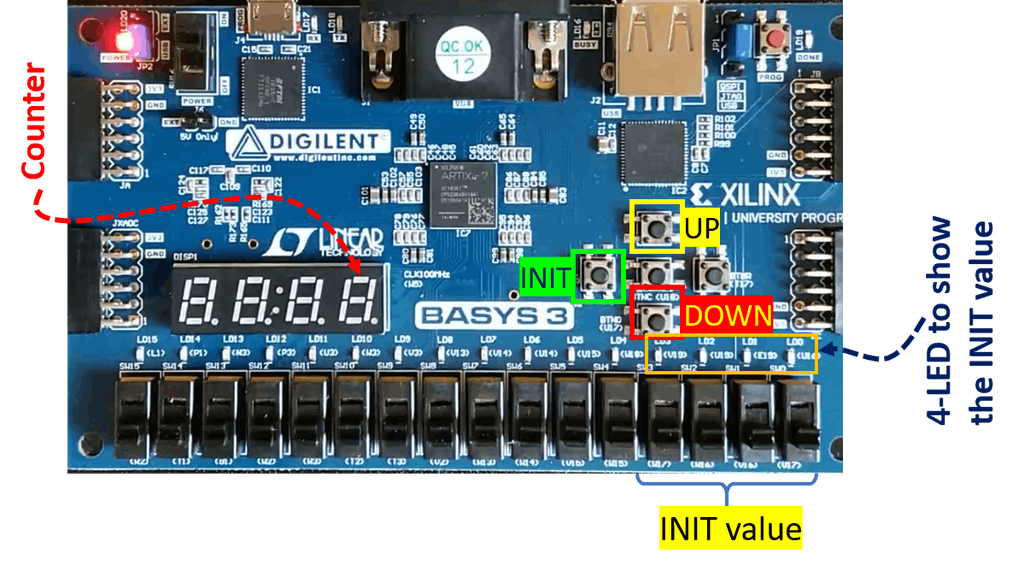

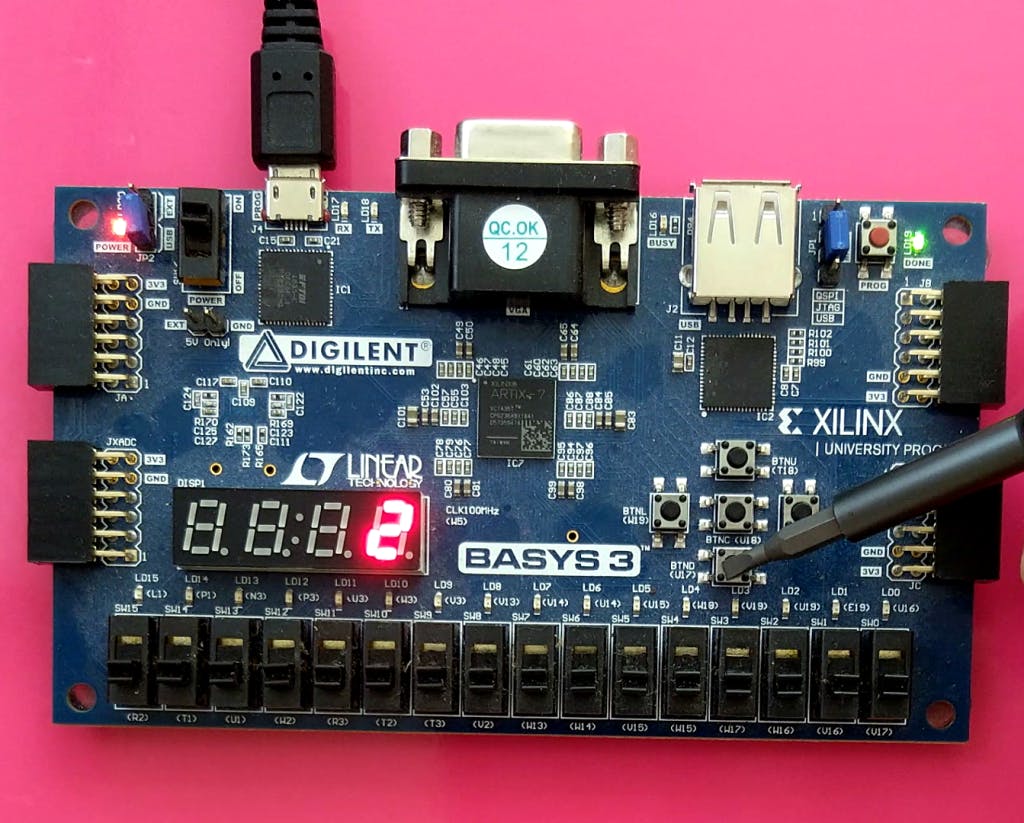

為了實現這個項目,我使用了 Vivado Design Suite – HLx Editions 提供的 Xilinx HLS 平臺。此外,我將使用 Basys 3 評估板作為目標 FPGA 平臺。圖 2 顯示了板上最終遞增/遞減計數器的布局。右側的 7 段顯示計數器。UP 按鈕用于向上計數,DOWN 按鈕用于向下計數。INIT 按鈕初始化計數器。用“INIT value”表示的四個滑動開關用于輸入初始化編號。此外,四個 LED 顯示該值。

我們分三個階段來實施這個項目:C/C++ 描述、邏輯綜合和電路板編程。

第 1 階段:C/C++ 描述(Vivado-HLS 項目)

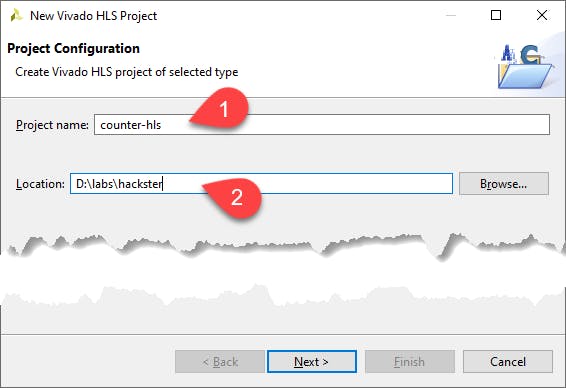

1- 運行 Vivado-HLS IDE 并創建一個新項目。

2- 在創建新項目向導的第一頁中,插入“counter-vhls”作為項目名稱,并為項目文件選擇適當的位置。

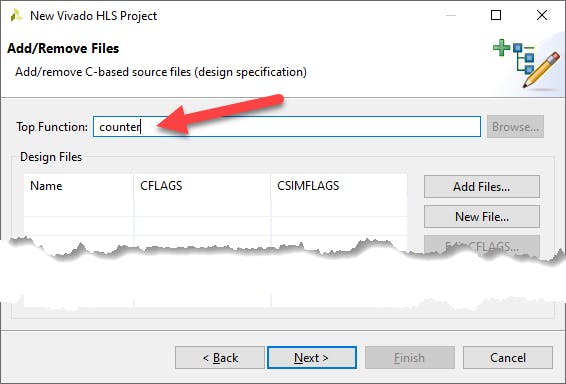

3-選擇“計數器”作為頂級功能名稱。

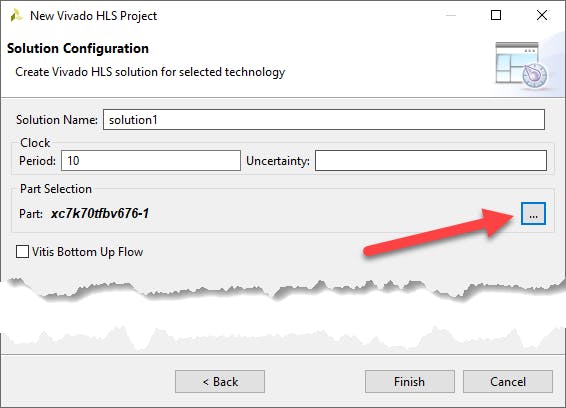

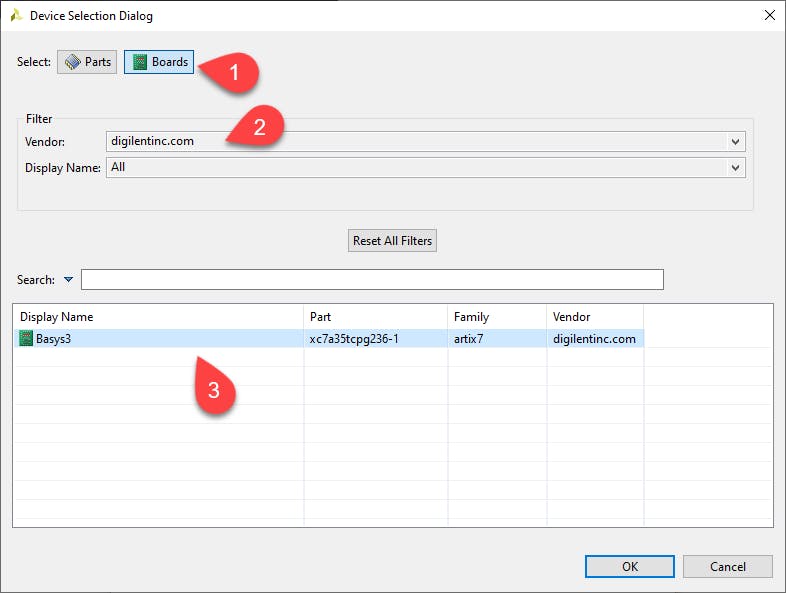

4- 在“解決方案配置”頁面中,單擊省略號按鈕選擇 FPGA 平臺。

5- 設備選擇對話框將打開。點擊Boards,找到digilent vendor,選擇Basys3 board,點擊OK。

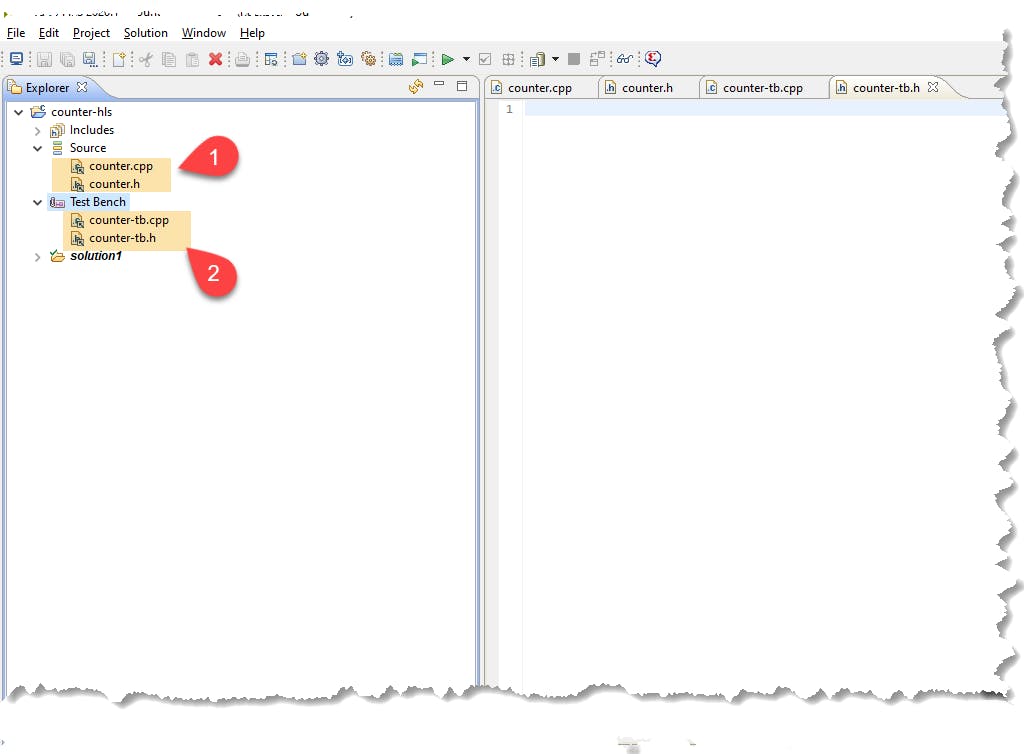

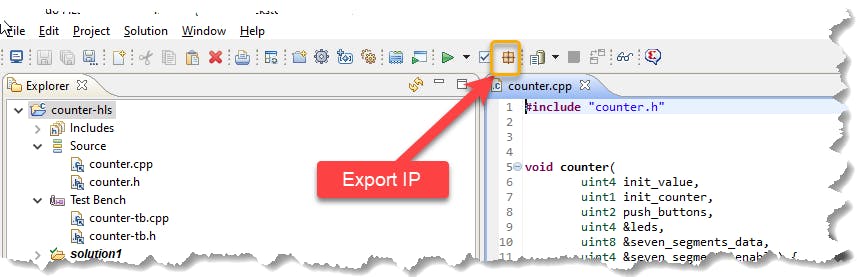

6- 在 Source 文件夾下創建兩個名為“counter.cpp”和“counter.h”的新文件。

7- 在 Test Bench 文件夾下創建兩個名為“counter-tb.cpp”和“counter-tb.h”的新文件。

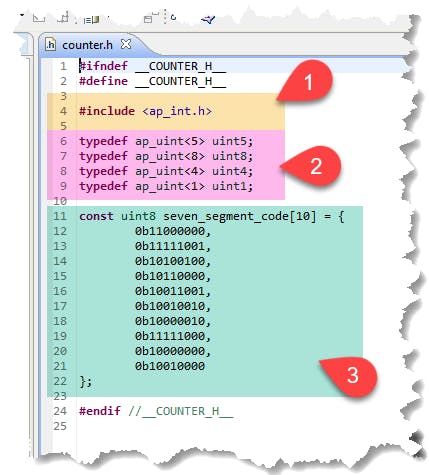

8-讓我們編寫設計頭文件如下。如下圖所示,該文件中的代碼分為三個部分:

1- 首先,由于我們要使用 HLS 任意精度數據類型,我們應該包含“ap_int.h”頭文件。2- 其次,我們定義了一些稍后在設計中使用的數據類型 3- 最后,我們定義了一個常量數組,用于保存對應于從 0 到 9 的數字的 7 段代碼。

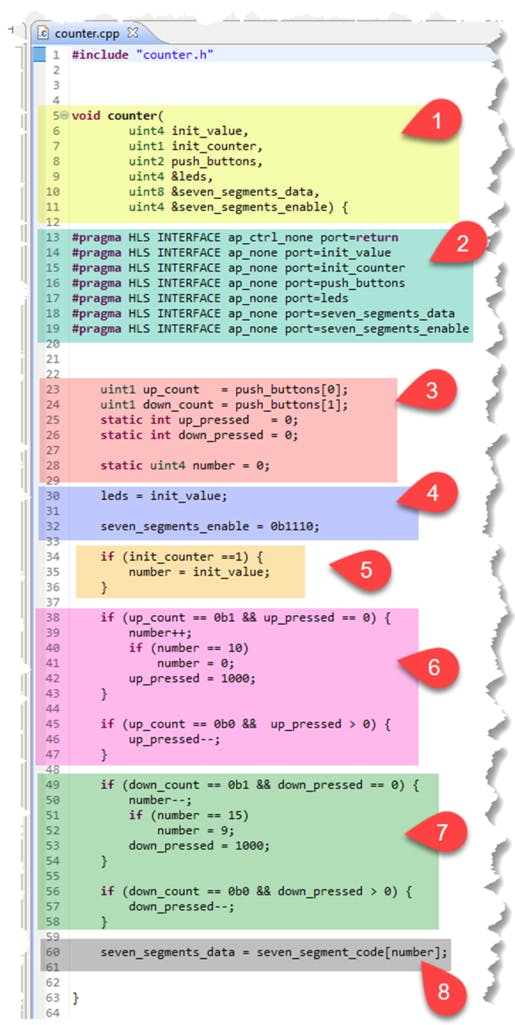

9- 設計源文件包含頂層功能描述。它由八個部分組成。

1-頂級函數參數:該函數包含三個輸入和兩個輸出參數。

init_value變量包含計數器初始值。

reset_counter變量確定何時應該初始化計數器。當它為 1 時,計數器獲取init_value參數中的值。

push_buttons變量確定向上或向下計數。

Seven_segments_data變量包含對應于計數器狀態的 7 段代碼

Seven_segments_enable變量啟用目標 7 段。

2-端口接口:本節定義與頂級函數參數對應的端口接口。這些接口定義了實現參數數據事務的硬件結構。由于我們有一個簡單的設計,并且我們希望簡單的電線實現參數,我選擇了ap_none作為接口模式。

3-聲明變量:在這里,我聲明了一些要在設計中使用的變量。如果按下 UP 按鈕,up_count 變量將為1 。如果按下 DOWN 按鈕,則 down_count 將為1 。up_pressed和down_pressed被聲明為靜態變量以保存按鈕的歷史記錄。number變量保持計數器狀態,因此定義為靜態變量。

4-設置輸出:此部分將 INIT 值發送到 LED 并啟用右側 7 段。

5-初始化:如果reset_counter信號被激活,這個if 語句初始化計數器狀態。

6-向上計數:這部分由兩個if 語句組成。第一個檢查是否按下了向上按鈕。第二個if檢查 UP 按鈕是否已被釋放。

7-向下計數:這部分與向上計數部分非常相似。

8- 7 段碼:最后一段發出計數器狀態對應的 7 段碼。

10- 現在,我們需要一個 C/C++ 測試平臺來測試設計。可以在此處找到測試臺文件。測試臺分為三個步驟:

— 生成測試向量, — 將測試向量應用于設計, — 最后,將硬件輸出與黃金模型的輸出進行比較并報告任何差異

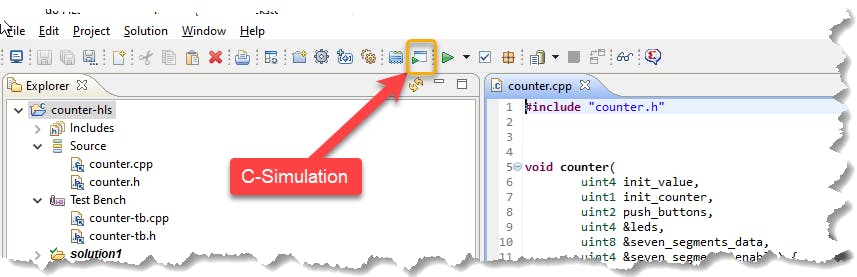

11- 現在我們可以通過單擊工具欄中的圖標來運行 C 模擬。

12-成功完成C-Simulation后,我們可以運行高級綜合。

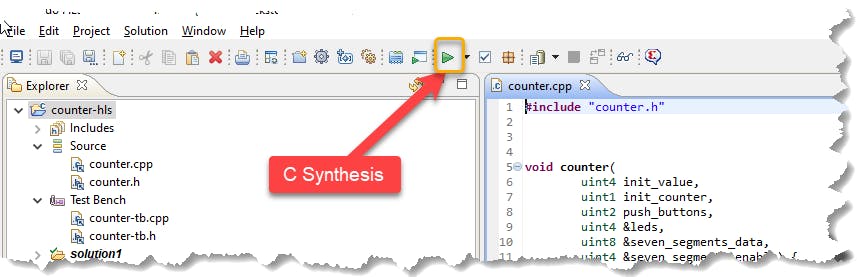

圖 13 顯示了綜合報告的部分內容。它有三個主要部分:

1- 時序信息 2- 資源利用 3- 端口接口

13- 最后,我們應該通過單擊其圖標來生成和導出設計 RTL-IP。

第 2 階段:邏輯綜合(Vivado 項目)

現在,我們已準備好進行邏輯綜合和生成 FPGA 比特流。

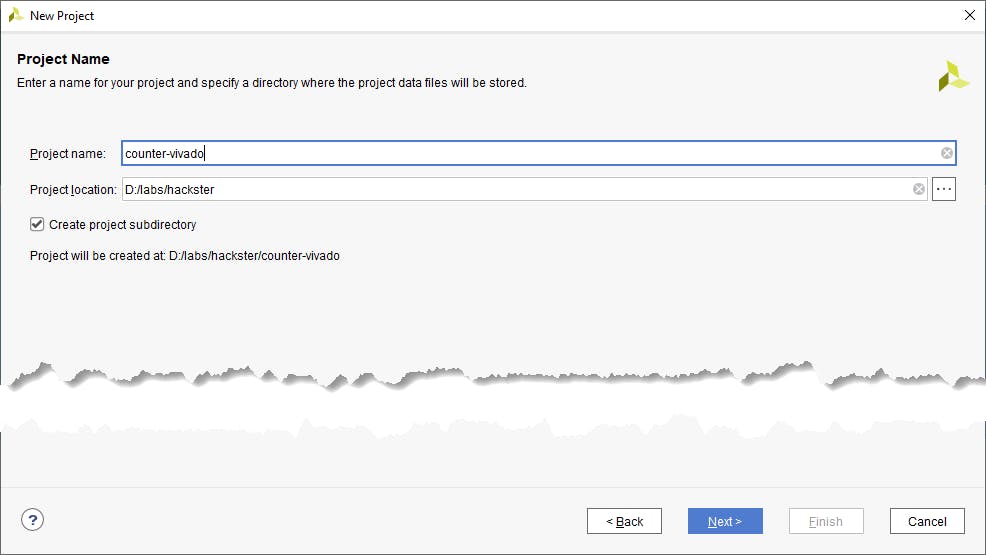

1-創建一個名為counter-vivado的新Vivado項目。請注意,該項目沒有任何源文件。

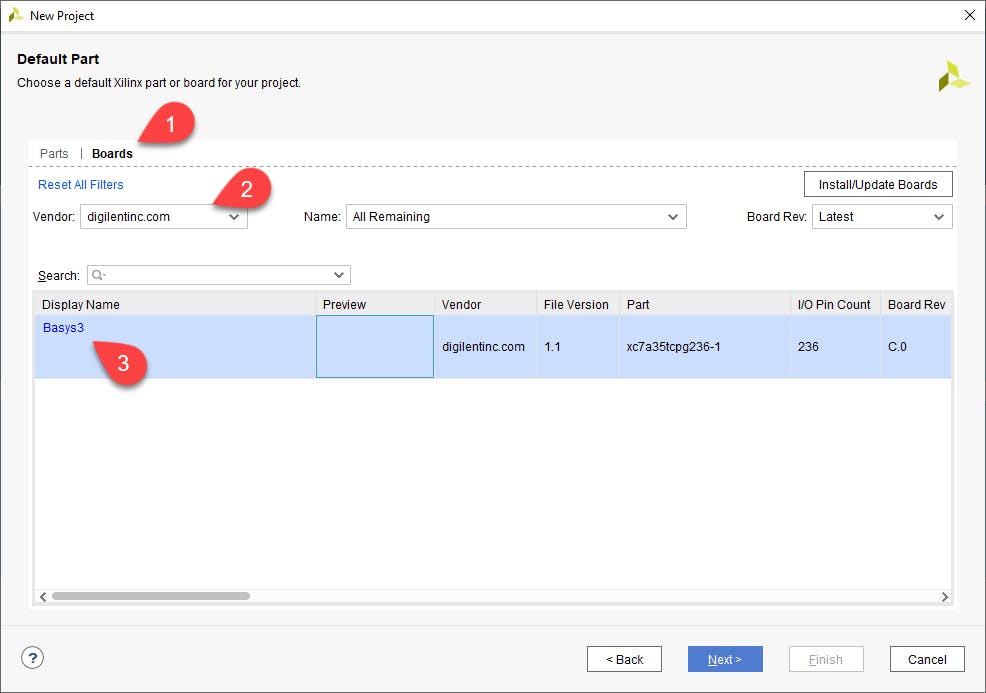

2- 不要忘記選擇 Basys-3 板作為目標 FPGA。

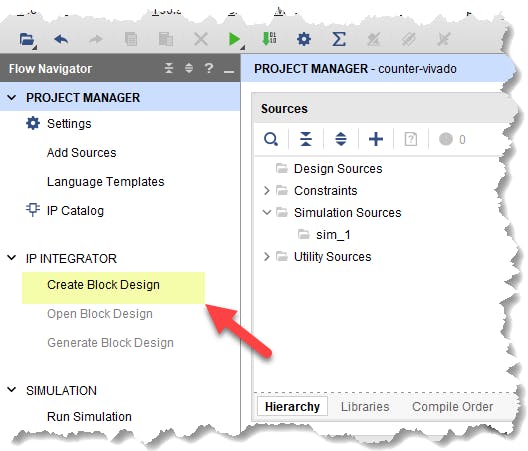

3-創建一個新的塊設計

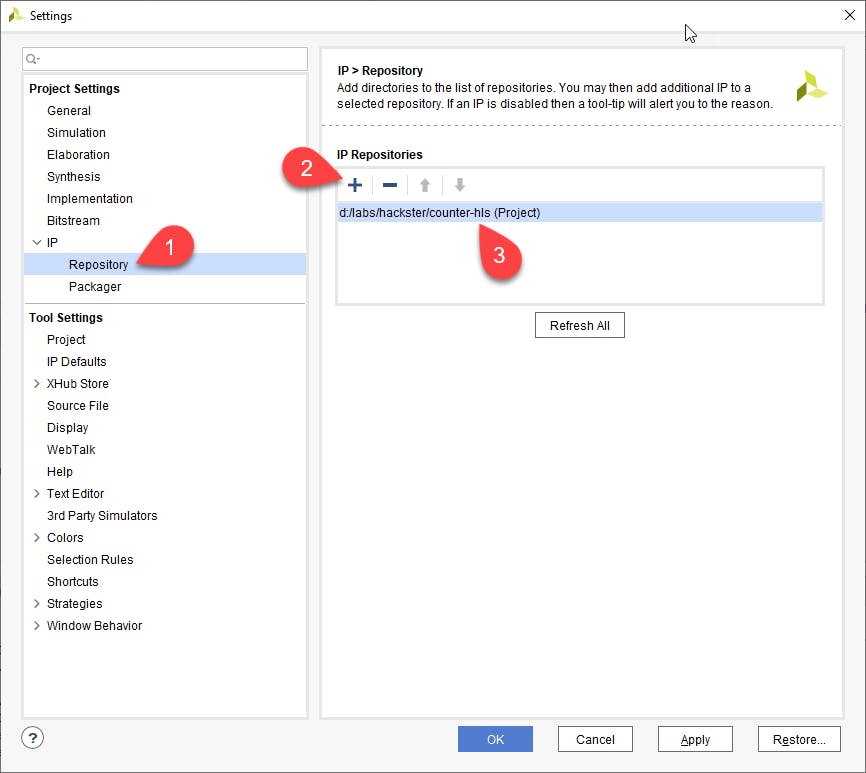

4-右鍵單擊圖表區域內的某處并選擇“IP設置...”選項

5-然后單擊設置對話框中IP下的存儲庫選項。然后點擊右側的加號,瀏覽到counter HLS項目文件夾。Vivado 在文件夾中搜索任何可能的 IP 并將其添加到其存儲庫中。

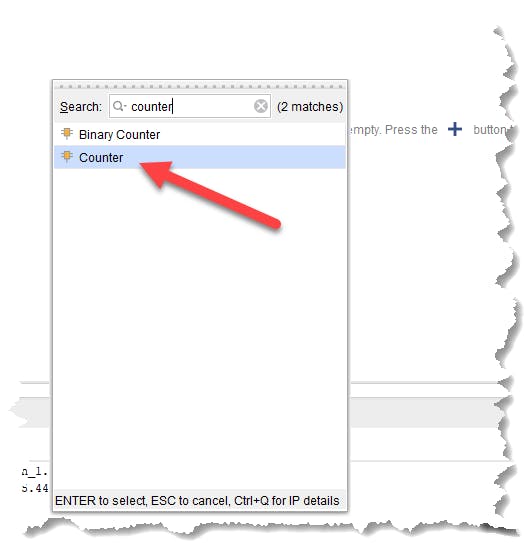

6- 右鍵單擊??圖表區域內的某處并選擇“添加..”選項。然后搜索計數器 IP 并將其添加到 vivado 項目中。

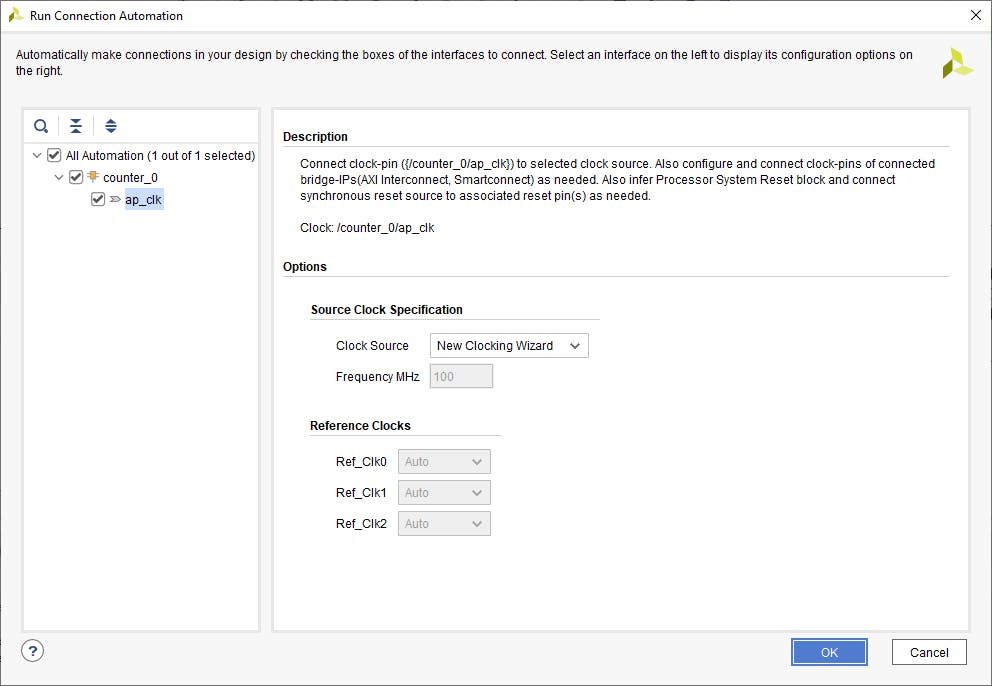

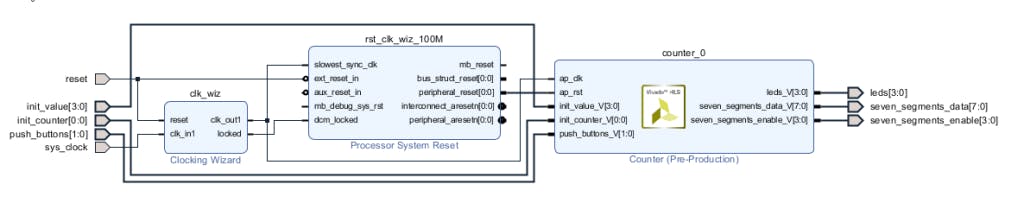

17- 單擊圖表區域頂部的“運行連接自動化”。

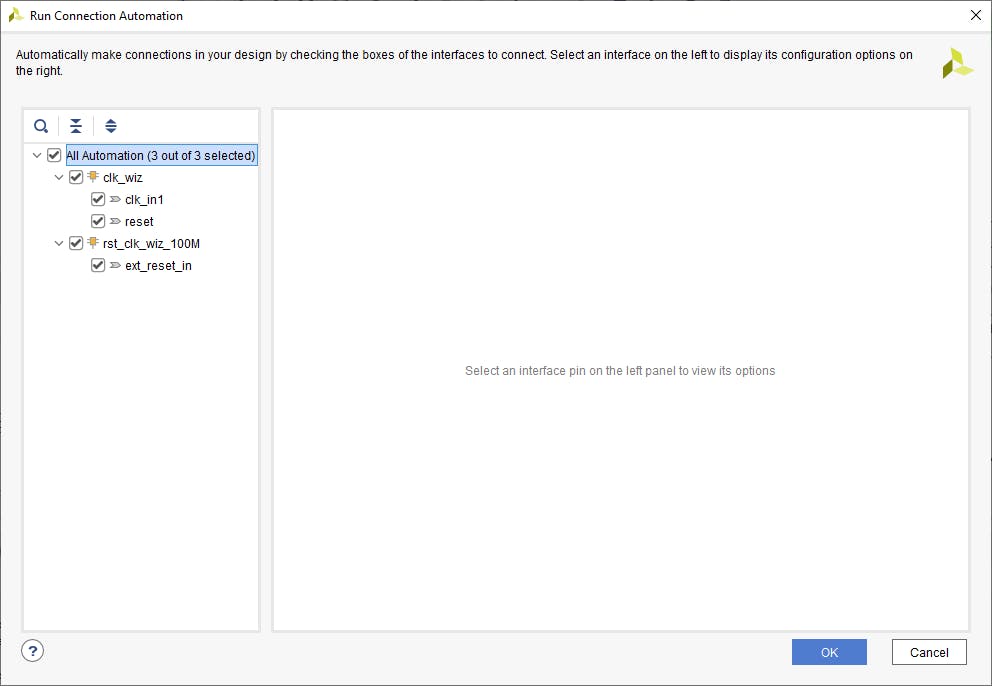

18- 再次單擊圖表區域頂部的“運行連接自動化”。

9- 在我們的計數器 IP 上選擇未連接的端口并將它們設為外部(右鍵單擊端口名稱,您將在下拉菜單中看到“設為外部”選項)。

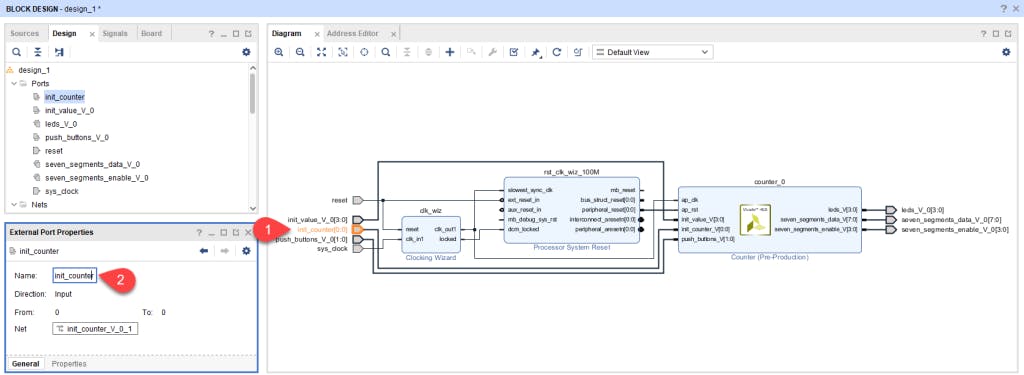

10-您可以通過選擇端口并使用“外部端口屬性”窗口來重命名端口。

init_counter_V_0 -----------> init_counter

push_buttons_V_0------------> push_buttons

init_value_V_0--------------> init_value

init_counter----------------> init_counter

leds_V_0--------------------> leds

seven_segments_data_V_0 ----> seven_segments_data

seven_segments_enable_V_0---> seven_segments_enable

11- 現在創建一個約束文件,并添加以下約束以將 IP 端口連接到具有適當 I/O 標準的 FPGA 引腳。

## Switches

set_property PACKAGE_PIN V17 [get_ports {init_value[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {init_value[0]}]

set_property PACKAGE_PIN V16 [get_ports {init_value[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {init_value[1]}]

set_property PACKAGE_PIN W16 [get_ports {init_value[2]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {init_value[2]}]

set_property PACKAGE_PIN W17 [get_ports {init_value[3]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {init_value[3]}]

# LEDs

set_property PACKAGE_PIN U16 [get_ports {leds[0]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {leds[0]}]

set_property PACKAGE_PIN E19 [get_ports {leds[1]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {leds[1]}]

set_property PACKAGE_PIN U19 [get_ports {leds[2]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {leds[2]}]

set_property PACKAGE_PIN V19 [get_ports {leds[3]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {leds[3]}]

#7 segment display

set_property PACKAGE_PIN W7 [get_ports {seven_segments_data[0]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[0]}]

set_property PACKAGE_PIN W6 [get_ports {seven_segments_data[1]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[1]}]

set_property PACKAGE_PIN U8 [get_ports {seven_segments_data[2]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[2]}]

set_property PACKAGE_PIN V8 [get_ports {seven_segments_data[3]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[3]}]

set_property PACKAGE_PIN U5 [get_ports {seven_segments_data[4]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[4]}]

set_property PACKAGE_PIN V5 [get_ports {seven_segments_data[5]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[5]}]

set_property PACKAGE_PIN U7 [get_ports {seven_segments_data[6]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[6]}]

set_property PACKAGE_PIN V7 [get_ports seven_segments_data[7]]?

set_property IOSTANDARD LVCMOS33 [get_ports seven_segments_data[7]]

set_property PACKAGE_PIN U2 [get_ports {seven_segments_enable[0]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_enable[0]}]

set_property PACKAGE_PIN U4 [get_ports {seven_segments_enable[1]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_enable[1]}]

set_property PACKAGE_PIN V4 [get_ports {seven_segments_enable[2]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_enable[2]}]

set_property PACKAGE_PIN W4 [get_ports {seven_segments_enable[3]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_enable[3]}]

#Buttons

set_property PACKAGE_PIN T18 [get_ports push_buttons[0]]?

set_property IOSTANDARD LVCMOS33 [get_ports push_buttons[0]]

set_property PACKAGE_PIN W19 [get_ports init_counter[0]]?

set_property IOSTANDARD LVCMOS33 [get_ports init_counter[0]]

set_property PACKAGE_PIN U17 [get_ports push_buttons[1]]?

set_property IOSTANDARD LVCMOS33 [get_ports push_buttons[1]]

12- 現在右鍵單擊圖表區域內的某處并選擇“驗證設計”選項。

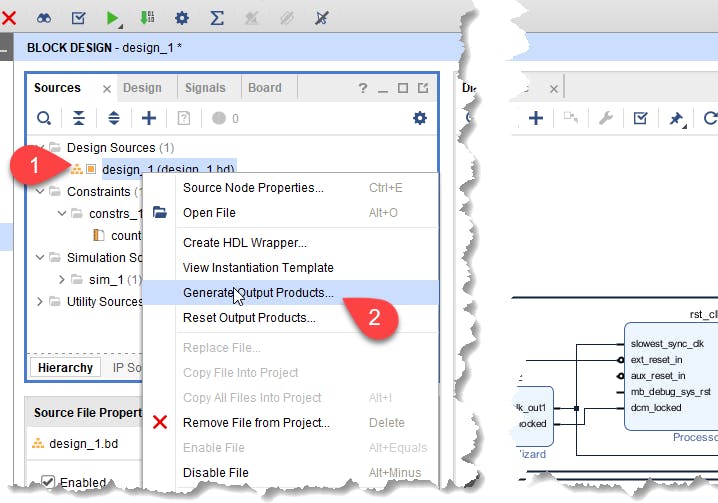

13-成功驗證設計后,右鍵單擊“Design Sources”文件夾下的“ design_1 ”并選擇“Generate Output Products...”

14- 然后,再次右鍵單擊“Design Sources”文件夾下的“design_1”并選擇“Create HDL Wrapper...”

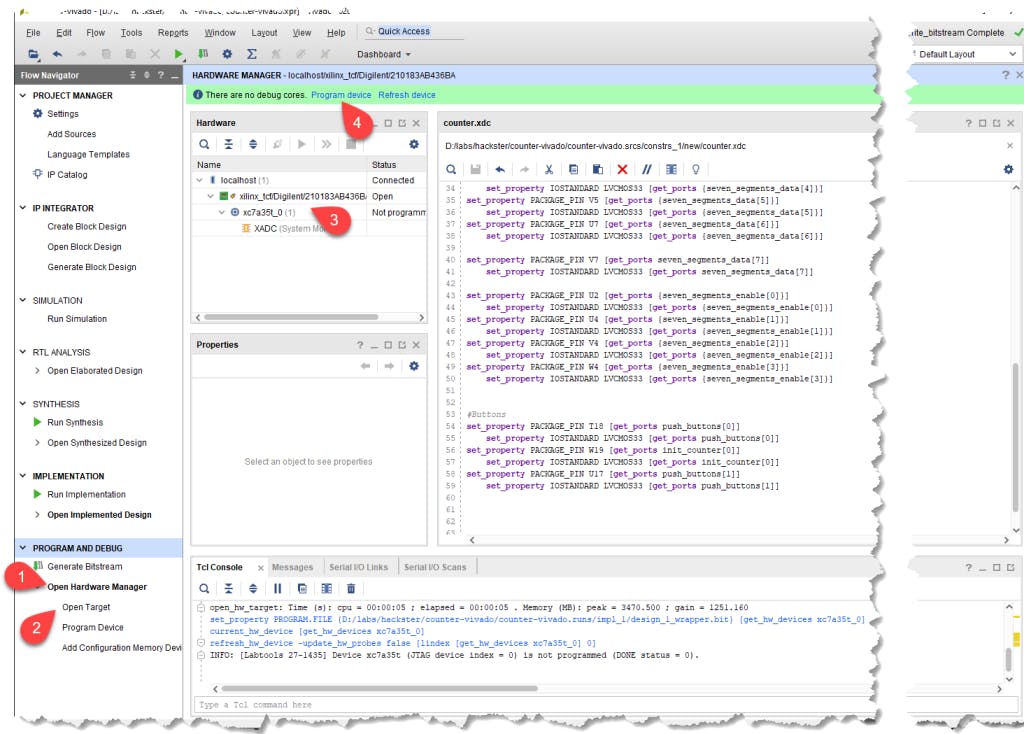

15- 現在單擊左側 Flow Navigator 中 PROGRAM and DEBUG 下的“Generate Bitstream”選項。

第 3 階段:電路板編程

1- 最后,對電路板進行編程并檢查設計。

如果您對使用 HLS 進行設計感興趣,請查看具有FPGA 高級合成的數字系統設計:組合電路

- 簡單的0至9計數器開源分享

- CC2530中斷初始化和中斷函數

- 單片機 -定時/計數器的初始化編程及應用

- 51單片機單個數碼管0-9循環秒計數

- 51單片機定時/計數器的工作原理

- C51單片機中的定時器和計數器的詳細介紹

- 在51平臺下初始化文件的引入導致全局變量無法初始化的問題如何解決

- 單片機計數器的應用資料說明

- 使用單片機設計0到9999計數器并帶有暫停清零功能的程序資料免費下載

- 計數器邏輯功能測試實驗報告 15次下載

- 如何排除代碼編寫器Studio 2和2.10的初始化問題 4次下載

- SEED-DEC2812初始化函數說明 11次下載

- 定時計數器初始化 16次下載

- Proteus之定時_計數器0用于計數的應用 0次下載

- 單片直接驅動數碼管的計數器程序 187次下載

- 同步計數器和異步計數器的區別 2435次閱讀

- 字符型、指針型等變量等該如何初始化 868次閱讀

- 計數器怎么用 計數器的作用有哪些 4090次閱讀

- SIMATIC S7-1500 PLC加減計數器簡述 6326次閱讀

- 什么是指定初始化? 730次閱讀

- 西門子S7-300PLC高速計數器的計數方式簡介 5778次閱讀

- SCL語言之加計數-計數器函數S_CU 1428次閱讀

- RT-Thread自動初始化機制 2362次閱讀

- 如何使用SPI總線設計正交編碼器計數器 3921次閱讀

- 鴻蒙內核源碼:內核空間是怎么初始化的? 1735次閱讀

- 計數器函數S_CU的操作步驟 8075次閱讀

- 單片機定時器/計數器的結構 7860次閱讀

- 如何有效地對神經網絡參數進行初始化 4006次閱讀

- PCIe總線必須要先完成Flow Control初始化 7780次閱讀

- 8253初始化程序分享_8253應用案例 2.1w次閱讀

下載排行

本周

- 1山景DSP芯片AP8248A2數據手冊

- 1.06 MB | 532次下載 | 免費

- 2RK3399完整板原理圖(支持平板,盒子VR)

- 3.28 MB | 339次下載 | 免費

- 3TC358743XBG評估板參考手冊

- 1.36 MB | 330次下載 | 免費

- 4DFM軟件使用教程

- 0.84 MB | 295次下載 | 免費

- 5元宇宙深度解析—未來的未來-風口還是泡沫

- 6.40 MB | 227次下載 | 免費

- 6迪文DGUS開發指南

- 31.67 MB | 194次下載 | 免費

- 7元宇宙底層硬件系列報告

- 13.42 MB | 182次下載 | 免費

- 8FP5207XR-G1中文應用手冊

- 1.09 MB | 178次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 2555集成電路應用800例(新編版)

- 0.00 MB | 33566次下載 | 免費

- 3接口電路圖大全

- 未知 | 30323次下載 | 免費

- 4開關電源設計實例指南

- 未知 | 21549次下載 | 免費

- 5電氣工程師手冊免費下載(新編第二版pdf電子書)

- 0.00 MB | 15349次下載 | 免費

- 6數字電路基礎pdf(下載)

- 未知 | 13750次下載 | 免費

- 7電子制作實例集錦 下載

- 未知 | 8113次下載 | 免費

- 8《LED驅動電路設計》 溫德爾著

- 0.00 MB | 6656次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935054次下載 | 免費

- 2protel99se軟件下載(可英文版轉中文版)

- 78.1 MB | 537798次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420027次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191187次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183279次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138040次下載 | 免費

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論