資料介紹

描述

注意:模糊和偽像是手機攝像頭偽像,不存在于生成的電子 VGA 信號中)

分形生成是一種流行的 FPGA 設(shè)計練習(xí)。例如,斯坦福大學(xué)在 2002 年就已將其用作實驗室作業(yè)。一定是在那個時候,我在某個交易會上看到了類似的演示,并且從那時起就渴望嘗試一下。

好吧,我最終解決了它。

花了很長時間。

動機

FPGA 業(yè)余項目增加了一個獨特的設(shè)計挑戰(zhàn):它需要始終充滿樂趣。

有時,通往終點線的路變得筆直、明顯且乏味。就像徒步旅行與通勤一樣,這不僅僅是以最有效的方式從 A 地到達 B 地……所以你提出了一個新的想法,讓它再次變得有趣。沖洗并重復(fù)。

概述

“樂趣因素驅(qū)動的需求管理”最終沿著這些路線發(fā)展:

- 實時計算

- 60 Hz 時的全高清分辨率 (1920x1080)

- 明智地使用 FPGA:最終實現(xiàn)接近每個時鐘周期每個乘法器一個操作。在 USB 總線功率預(yù)算約為 2 瓦的 35 尺寸 Artix 上,這是每秒 180 億次乘法運算。

- 執(zhí)行動態(tài)資源分配。分形算法有些不尋常,因為所需的迭代次數(shù)因點而異。與簡單地設(shè)置固定的迭代次數(shù)相比,復(fù)雜度大大增加(一個時鐘周期內(nèi)可能出現(xiàn)隨機數(shù)量的結(jié)果,結(jié)果是無序的)但性能也是如此。

- 限制為 18 位乘法,因為它是 Xilinx 6/7 系列 DSP48 塊的原生寬度。為更高分辨率增加內(nèi)部位寬很簡單,但資源使用量猛增。

- (合理地)獨立于供應(yīng)商。我決定使用開源“J1B”軟核 CPU,而不是 Microblaze MCS,后者會非常簡單。

- 我決定使用我自己的簡單編譯器/匯編器“forthytwo.exe”,而不是用于 J1B 的原始“gforth”工具鏈,它在整個過程中得到了清理。

-

CPU 上對性能無關(guān)緊要的代碼的浮點數(shù)學(xué)運算。

“因為當(dāng)你凝視兔子洞時,兔子洞也在凝視你”。

我自己的“最小”浮點數(shù)實現(xiàn)并沒有像 IEEE 754 那樣精致或安全,但它很小并且到目前為止做得很好。 - 普通 UART 上的 CPU 引導(dǎo)加載程序(意味著沒有專有的 Xilinx JTAG)。包含的引導(dǎo)加載程序?qū)崿F(xiàn)了強大的同步和高效的二進制文件上傳。

- 沒有深奧的工具,能夠在 Windows 上運行(同樣,Linux 會更容易)。在干凈的 Windows PC 上,可以通過安裝 MinGW(開發(fā)人員設(shè)置)、Vivado 和 Verilator 來設(shè)置構(gòu)建系統(tǒng)。有關(guān)后者,請參閱我的安裝說明。將例如 Teraterm 與引導(dǎo)加載程序一起使用。

- 包含電池的項目,旨在通過刪除不需要的內(nèi)容來重用(也許這更多是在微控制器方面,因為分形部分是針對特定問題的)

就緒/有效的設(shè)計模式說明

計算引擎在很大程度上依賴于有效/就緒的握手范例,該范例在整個鏈中一致使用。

在這里,它非常重要,原因很簡單:分形發(fā)生器的 200 MHz 時鐘速率小于 VGA 像素速率的兩倍。任何需要空閑時鐘周期來恢復(fù)的“次優(yōu)”握手方案都會破壞體系結(jié)構(gòu)。

就緒/有效組合路徑問題

在典型的處理塊中,數(shù)據(jù)通過一系列寄存器以鎖步方式移動。當(dāng)通過就緒/有效接口級聯(lián)任意數(shù)量的此類塊時,“就緒”信號形成從鏈的末端到開始的組合路徑。這會使時序收斂變得困難或不可能。當(dāng)考慮處理鏈末端發(fā)出“未準備好”(接受數(shù)據(jù))信號時會發(fā)生什么時,問題就很明顯了:整個管道長度上的數(shù)據(jù)無處可去,因此整個鏈必須在一個時鐘周期。

解決方案是使用 FIFO 將鏈分成多個段(2 個插槽就足夠了)。有一個問題:我可以設(shè)計一個“優(yōu)化的”FIFO,即使數(shù)據(jù)已滿,只要在同一時鐘周期內(nèi)從輸出中取出一個元素,它也會接受數(shù)據(jù)。這種“優(yōu)化”將準確地引入 FIFO 應(yīng)該打破的組合路徑,因此它對于解耦組合鏈是無用的。換句話說,F(xiàn)IFO的輸入端不能組合使用輸出端的“就緒”信號。

就緒/有效流控

也許這是顯而易見的,但就緒/有效鏈中的數(shù)據(jù)流可以在任何時候停止,只需插入一個將有效和就緒信號都強制為零(未斷言)的塊即可。該塊可以是組合的并且可以取決于觀察到的數(shù)據(jù)值。該模式用于阻止計算引擎運行在監(jiān)視器電子束之前太遠。

RTL實現(xiàn)

時鐘域

共有三個時鐘域:

- 200 MHz 的計算引擎(大部分設(shè)計)。這可以推得更高,但會使設(shè)計更難處理。現(xiàn)在,沒有理由這樣做,芯片已經(jīng)很熱了。

- 像素頻率為 148.5 MHz 的 VGA 監(jiān)視器信號

- J1B CPU 在 100 MHz,因為它的關(guān)鍵路徑對于 200 MHz 操作來說太慢了。

數(shù)據(jù)流

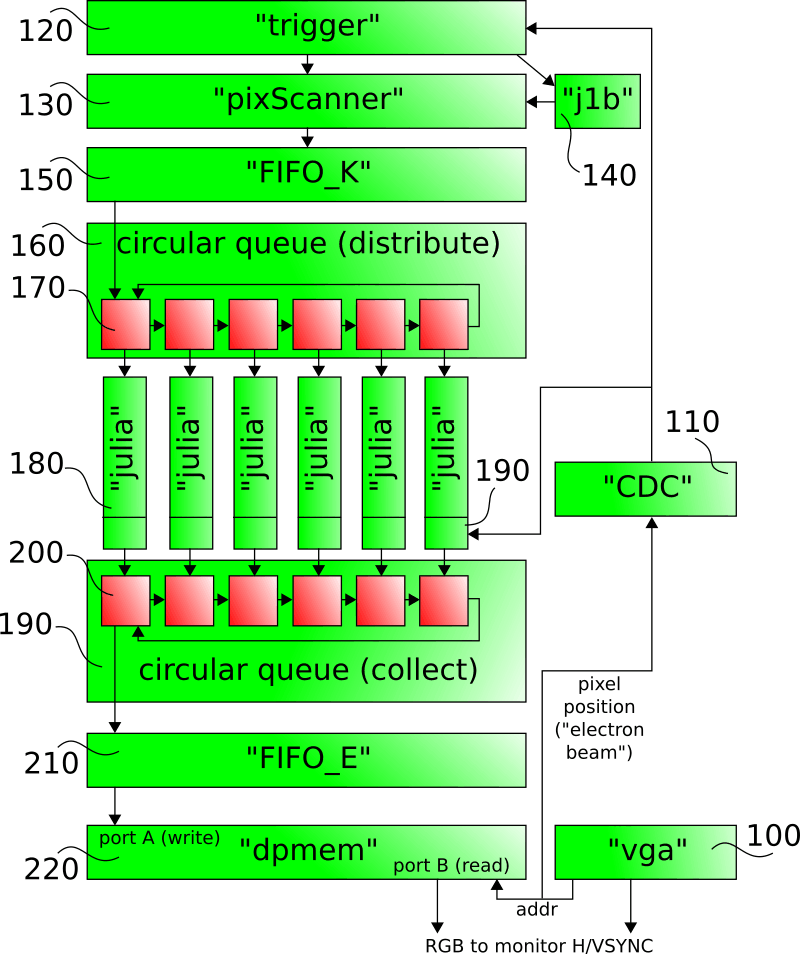

注:圖中名稱對應(yīng)Verilog實現(xiàn)

塊“vga” 100創(chuàng)建 VGA 監(jiān)視器時序。它的輸出之一是當(dāng)前在電子束下的像素數(shù)。

像素位置經(jīng)由格雷編碼通過時鐘域交叉點110進入“觸發(fā)”塊120 。這里,當(dāng)像素位置返回到零時,檢測到新幀的開始。這在最后一個可見像素已被發(fā)送到顯示器之后立即發(fā)生,因此前沿/VSYNC/后沿時間間隔可用于預(yù)先計算圖像數(shù)據(jù),直到緩沖器RAM 220的容量。

新幀開始的檢測觸發(fā)以下“pixScanner” 130 。該塊已經(jīng)從 CPU 140接收到分形坐標(biāo)并使用兩對增量逐行掃描它們:第一對增量 X/Y 用于電子束向右移動(列),第二對用于向下移動(行)。使用適當(dāng)?shù)脑隽浚瑘D片可以旋轉(zhuǎn)任何角度。

該塊保留一個幀計數(shù)器,CPU 140會對其進行輪詢,以在先前的幀坐標(biāo)已存儲后立即開始計算下一幀坐標(biāo)。

生成的像素坐標(biāo)向前移動到FIFO 150 。這只是為了解耦組合接受/就緒路徑。它不會提高吞吐量,因為像素掃描儀已經(jīng)能夠在每個時鐘周期生成一個輸出。

“像素坐標(biāo)”由分形空間中的 X 和 Y 位置以及線性像素位置形成,相當(dāng)于它在 vga 塊100中的對應(yīng)位置。后者是必需的,因為結(jié)果需要重新排序。

像素坐標(biāo)現(xiàn)在移動到循環(huán)分配隊列160中。其目的是為并行“julia”(分形)計算引擎180提供像素坐標(biāo)。如果一個計算引擎準備好接受一項新工作,該值將從隊列中刪除,否則它將右移通過插槽170并最終循環(huán)回到隊列的頭部。

當(dāng)沒有數(shù)據(jù)循環(huán)時,隊列160將只接受來自 FIFO_K 150的新輸入。ready/valid 協(xié)議的使用使得此功能的實現(xiàn)相對簡單。

計算引擎180將迭代 Mandelbrot 集算法(“轉(zhuǎn)義時間”算法,參見維基百科:https://en.wikipedia.org/wiki/Mandelbrot_set)。

使用默認設(shè)置(很容易更改),實現(xiàn)使用 30 個“julia”引擎180 。它們中的每一個都由 12 個管道級別組成。換句話說,每個引擎一次處理多達 12 個獨立的計算。每個“julia”引擎執(zhí)行三個并行乘法(xx、yy、xy),總共使用 90 個乘法器,每個周期在滿負載下執(zhí)行一次運算。

由于下游 RAM 220中的緩沖空間相當(dāng)有限——遠小于全幀——必須防止計算引擎180在電子束位置之前運行太遠。因此,流量控制機制190內(nèi)置于計算引擎中。它根據(jù)電子束檢查每個條目的像素編號,如果它會導(dǎo)致 RAM 220中的循環(huán)溢出,則阻止它離開計算引擎180 。如果拒絕退出,該值將繼續(xù)通過計算引擎進行虛擬迭代。時鐘域穿越110相對于實際圖像生成將像素位置延遲幾個時鐘周期,因此流量控制將始終(保守地)滯后于幾個像素。

類似于循環(huán)分發(fā)隊列160 ,結(jié)果被收集到循環(huán)收集隊列190中。如果槽200為空,它將接受來自計算引擎180的結(jié)果,否則計算引擎將繼續(xù)對結(jié)果進行虛擬迭代。

來自收集隊列190的退出數(shù)據(jù)項移動到FIFO_E 210 ,然后移動到雙端口存儲器220 。這個 FIFO 不再是絕對必要的:因為雙端口 ram 220總是準備好接受數(shù)據(jù),它可以用更便宜的寄存器代替。

雙端口存儲器220在其第二端口上由來自“vga”塊100的電子束位置索引。dp-memory 實現(xiàn)數(shù)據(jù)到 VGA 像素時鐘域的交叉。RAM 的輸出連同 HSYNC 和 VSYNC 信號一起最終轉(zhuǎn)發(fā)到監(jiān)視器輸出。

雖然圖中未顯示,但可通過連接到 CPU 的 IO 端口的寄存器訪問按鈕和 LED。

“julia”計算引擎

文檔待續(xù)……請暫時參考代碼(“julia”模塊)。

運行演示

- 獲取 CMOD A7-35 板(或修改項目)。該設(shè)計對于 15 尺寸的變體來說太大了。

- 上傳預(yù)構(gòu)建的“最終”比特流

- CPU 運行時,這兩個按鈕將分別切換紅色和綠色 LED。

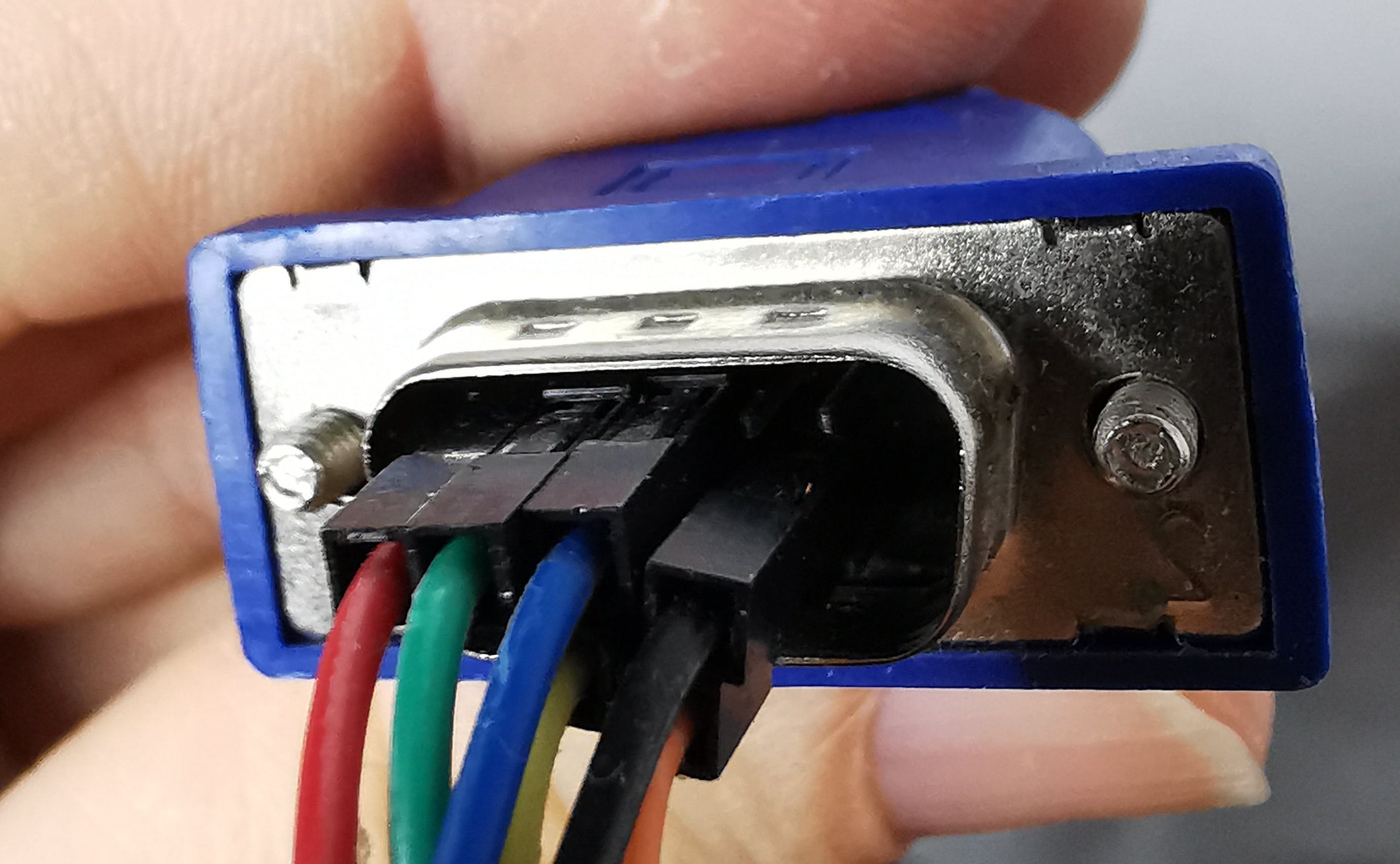

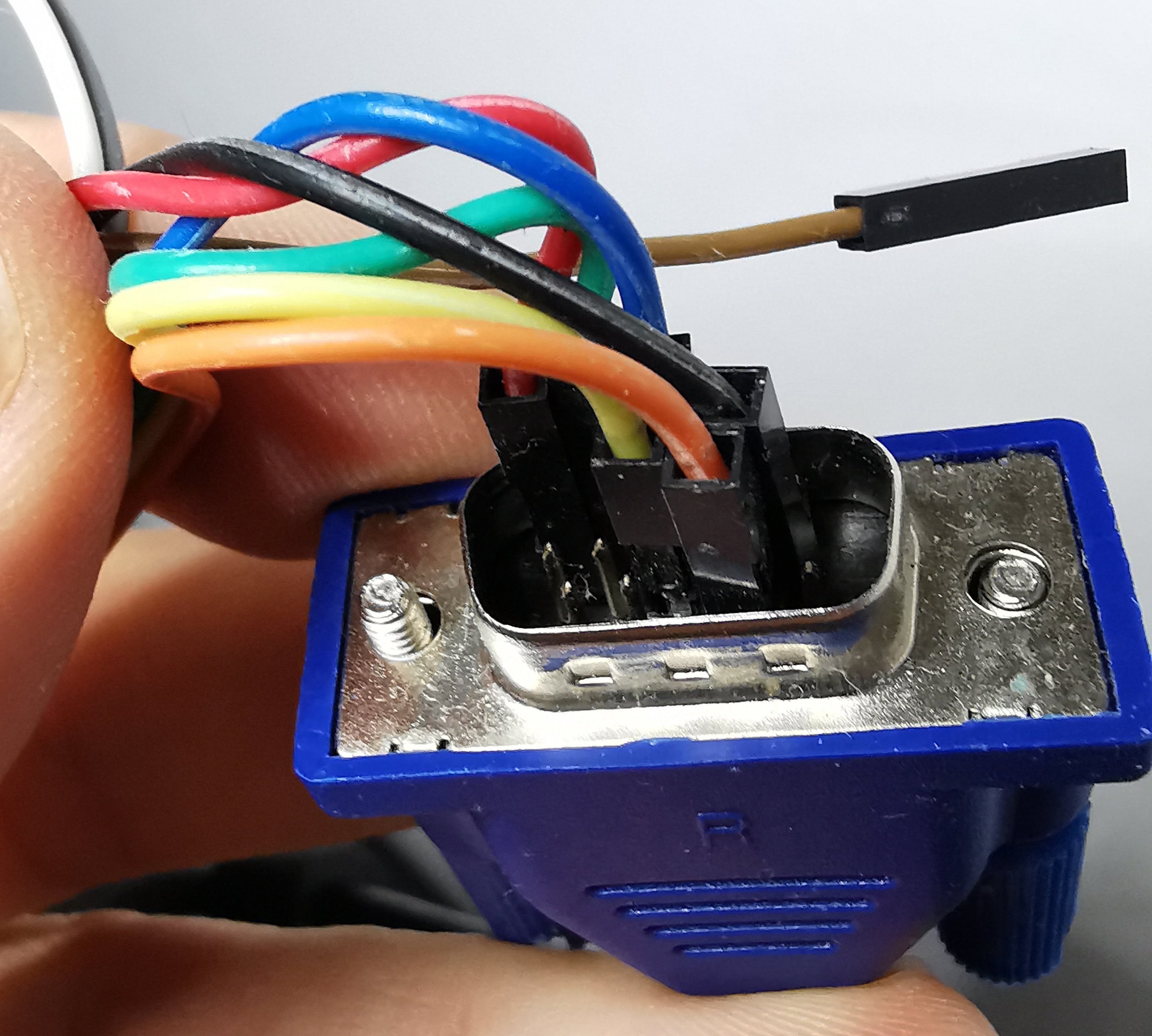

- 使用跨接電纜將顯示器連接到 DIL48 插座

默認引出線

- 引腳 1:紅色(照片中的紅線)

- 引腳 2:綠色(照片中的綠線)

- 引腳 3:藍色(照片中的藍線)

- 引腳 4:HSYNC(照片中的黃線)

- 引腳 5:VSYNC(照片中的橙色線)

- pin 25 or PMOD header: common GND (照片中的黑線)

請注意:3.3 V 不符合 VGA 模擬信號的規(guī)格。我從來沒有遇到過在相當(dāng)多的顯示器/投影儀上直接接線的問題,但請務(wù)必使用常識。

?

?

。

構(gòu)建項目

請使用 Vivado 2019.2。免費的“網(wǎng)絡(luò)版”就足夠了。

要重建比特流,請從頂級目錄運行

- make forthytwo:構(gòu)建編譯器

然后...

...對于“引導(dǎo)加載程序”版本(如果您想編輯微控制器代碼)

- 制作分形(仍然來自頂級目錄)。這將創(chuàng)建包含 J1B rom 內(nèi)容的 main.v 文件

- 在 fractalsProject/CMODA7_fractalDemo 中打開 Vivado 工程

- 生成比特流

- 上傳比特流

- 將 teraterm 連接到串行端口。測試按鍵是否回顯“x”=> 引導(dǎo)加載程序正常運行

- 通過 Teraterm 的“發(fā)送文件”功能以二進制模式發(fā)送“fractalsProject/out/main.bootBin”(!!)。請注意,“main.bootBin”是在啟用或禁用引導(dǎo)加載程序的情況下編譯的并不重要。

- 正確上傳打印一個字母“1”,按鈕將點亮 LED。只有現(xiàn)在 VGA 信號存在

...對于“發(fā)布”版本(在 FPGA 比特流中帶有微控制器代碼)

- 根據(jù)第一行中的說明編輯 bootloader/bootloader.txt(注釋掉第一個 BRA: 并取消注釋第二個 BRA:)

- 從頂層:制作分形

- 從 Vivado 構(gòu)建比特流

- 程序比特流(或?qū)懭腴W存)。一旦黃色“prog ready”LED 亮起,紅色/綠色 LED 應(yīng)響應(yīng)按鈕按下并且 VGA 信號存在。

Git 倉庫

- 在這里(用于在線閱讀。請克隆頂級“forthytwo”repo 并從頂級使用“make”。

執(zhí)照

請注意,J1B CPU 仍保留其原始 BSD 3-clause 許可,而我自己的文件是根據(jù) MIT 許可發(fā)布的。

- 結(jié)合DCT補償?shù)?b class="flag-6" style="color: red">分形圖像編碼_張愛華

- 移動社交網(wǎng)絡(luò)多重分形分析方法及其實驗 8次下載

- 在復(fù)雜網(wǎng)絡(luò)下的帶權(quán)圖的多重分形度量 10次下載

- 分形插值算法的詳細資料說明 0次下載

- 基于Y分形的平面微帶分形天線的設(shè)計與優(yōu)化的詳細資料說明 7次下載

- 如何以分形圖形為載體的信息隱藏算法 1次下載

- 如何使用IFS分形算法進行樹木形態(tài)的分析和實現(xiàn) 8次下載

- 改進的分形圖像編碼方法 2次下載

- 基于Curvelet變換與分形的遙感圖像融合 26次下載

- 改進型Sierpinski分形微帶天線仿真 58次下載

- 分形分維在數(shù)字全息顯示中的應(yīng)用 0次下載

- 海雜波的多重分形關(guān)聯(lián)特性與微弱目標(biāo)檢測

- 基于分形理論對天線的討論

- 基于OpenGL和分形技術(shù)的真實感云彩生成

- 一種新的非線性分形壓縮算法

- FPGA中時鐘的用法 1368次閱讀

- 壓線鉗四邊形與六邊形的特征、性質(zhì)以及應(yīng)用 3908次閱讀

- 基于幾何的泰森多邊形來生成形體骨架 820次閱讀

- 多頁式或堆疊式分形面板分組 570次閱讀

- LTspice:生成三角形和鋸齒波 1.2w次閱讀

- 使用Verilog/SystemVerilog硬件描述語言練習(xí)數(shù)字硬件設(shè)計 1485次閱讀

- 字符串函數(shù)重寫練習(xí) 1872次閱讀

- 如何利用智能語音交互芯片實現(xiàn)模擬練習(xí)器的設(shè)計 1574次閱讀

- 基于分形圖像編碼改進算法提高分形編碼的速度和壓縮比 1987次閱讀

- 組合邏輯生成的時鐘有哪些危害 3992次閱讀

- 如何快速入門FPGA 5398次閱讀

- 基于FPGA的圖像差分處理 7092次閱讀

- 鉗形電流表原理及使用 1.8w次閱讀

- 基于FPGA和高速D/A的多功能信號源生成系統(tǒng) 4256次閱讀

- FPGA創(chuàng)建一個程序生成規(guī)范 776次閱讀

下載排行

本周

- 1山景DSP芯片AP8248A2數(shù)據(jù)手冊

- 1.06 MB | 532次下載 | 免費

- 2RK3399完整板原理圖(支持平板,盒子VR)

- 3.28 MB | 339次下載 | 免費

- 3TC358743XBG評估板參考手冊

- 1.36 MB | 330次下載 | 免費

- 4DFM軟件使用教程

- 0.84 MB | 295次下載 | 免費

- 5元宇宙深度解析—未來的未來-風(fēng)口還是泡沫

- 6.40 MB | 227次下載 | 免費

- 6迪文DGUS開發(fā)指南

- 31.67 MB | 194次下載 | 免費

- 7元宇宙底層硬件系列報告

- 13.42 MB | 182次下載 | 免費

- 8FP5207XR-G1中文應(yīng)用手冊

- 1.09 MB | 178次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 2555集成電路應(yīng)用800例(新編版)

- 0.00 MB | 33566次下載 | 免費

- 3接口電路圖大全

- 未知 | 30323次下載 | 免費

- 4開關(guān)電源設(shè)計實例指南

- 未知 | 21549次下載 | 免費

- 5電氣工程師手冊免費下載(新編第二版pdf電子書)

- 0.00 MB | 15349次下載 | 免費

- 6數(shù)字電路基礎(chǔ)pdf(下載)

- 未知 | 13750次下載 | 免費

- 7電子制作實例集錦 下載

- 未知 | 8113次下載 | 免費

- 8《LED驅(qū)動電路設(shè)計》 溫德爾著

- 0.00 MB | 6656次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935054次下載 | 免費

- 2protel99se軟件下載(可英文版轉(zhuǎn)中文版)

- 78.1 MB | 537798次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420027次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191187次下載 | 免費

- 7十天學(xué)會AVR單片機與C語言視頻教程 下載

- 158M | 183279次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138040次下載 | 免費

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問

提問  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評論