作為半導體制造的后工序,

封裝工藝包含:

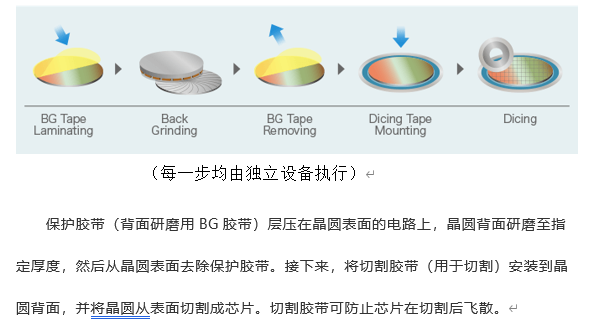

背面研磨(Back Grinding)

劃片(Dicing)

芯片鍵合(Die Bonding)

引線鍵合(Wire Bonding)

成型(Molding)

這些工藝的順序可根據封裝技術的變化進行調整、相互結合或合并。

芯片鍵合(die bonding)工藝,采用這種封裝工藝可在劃片工藝之后將從晶圓上切割的芯片黏貼在封裝基板(引線框架或印刷電路板)上。

1.什么是鍵合(Bonding)?

鍵合類型

Wire Bonding

Bump bonding

Wedge Bonding

Solder Paste Dispensing

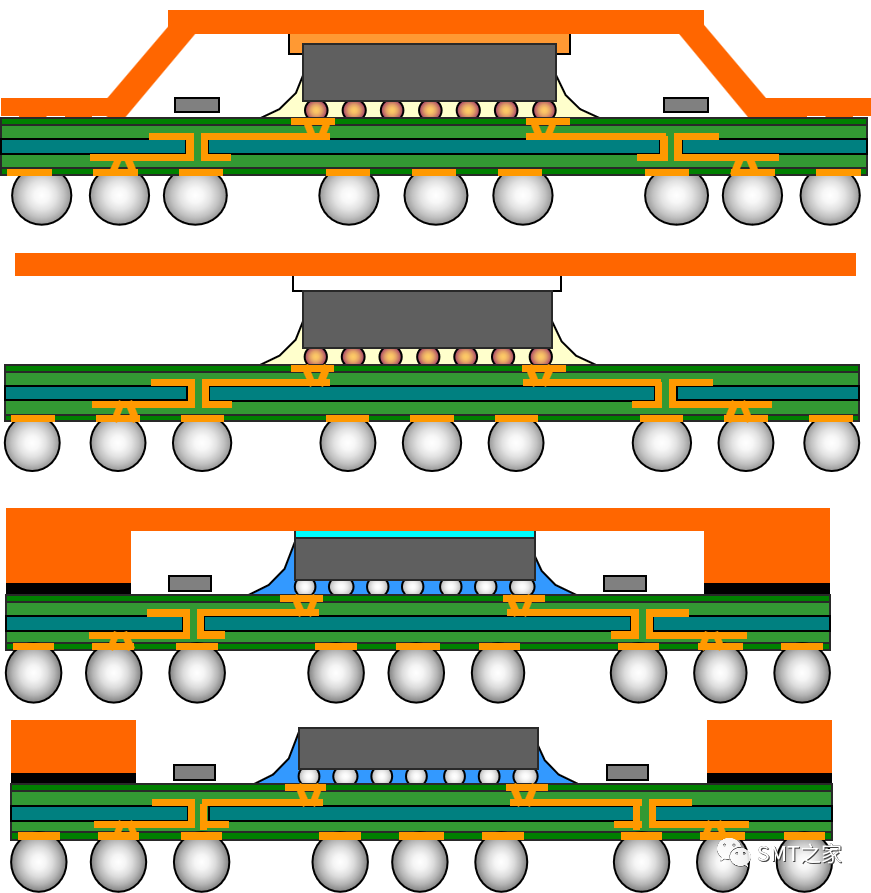

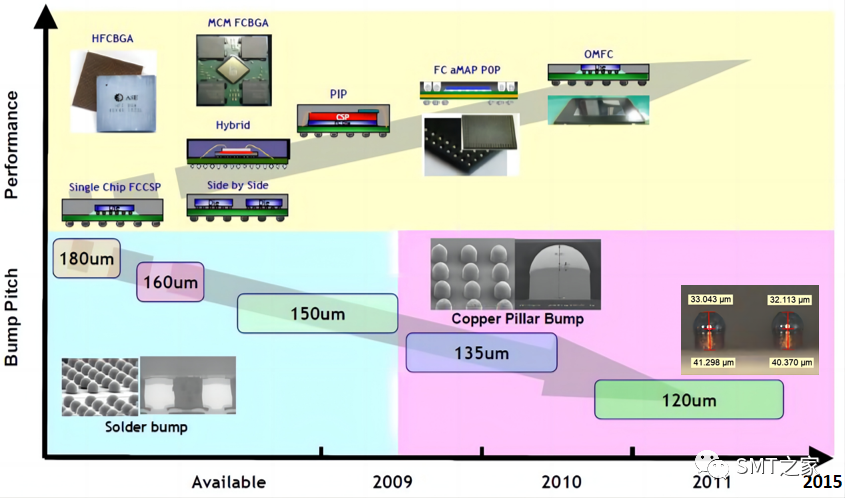

Flip chip Package Process typeIntroduction

倒裝芯片封裝工藝類型介紹

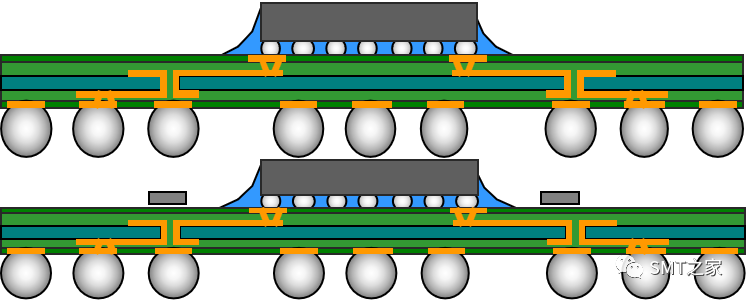

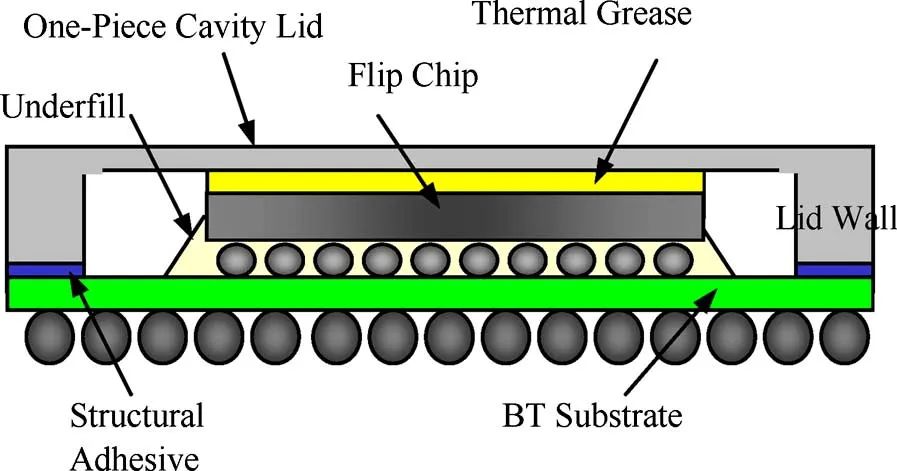

(PI)-EHS2-FCBGA

(Passive Integrated Exposed 2 pieces of Heat Sink Flip Chip BGA)

無源集成裸露2片散熱片倒裝BGA

(PI)-EHS-FCBGA

(Passive Integrated Exposed Heat Sink Flip Chip BGA)

無源集成暴露式散熱器倒裝芯片BGA

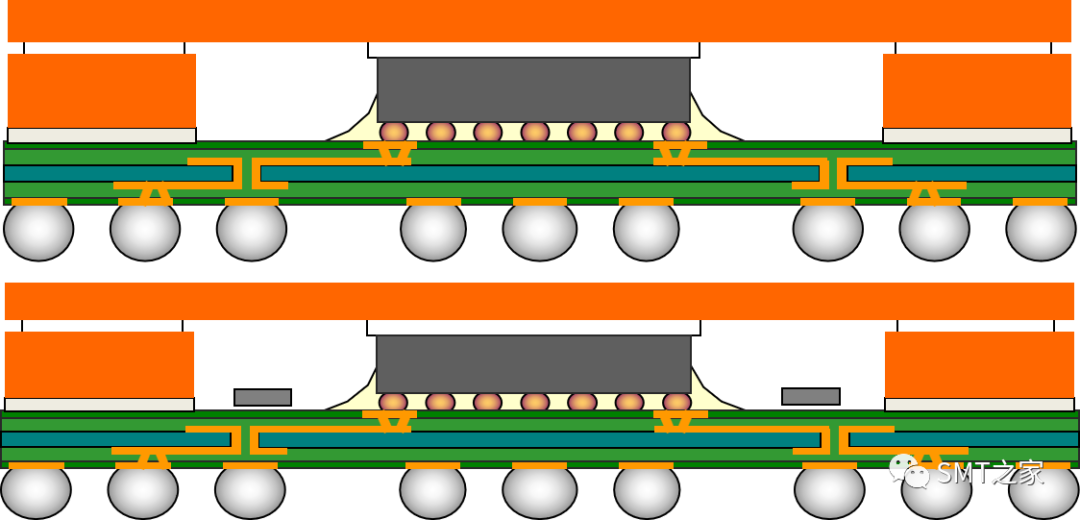

PI-EHS-MP-FCBGA

(Passive Integrated Exposed Heat Sink Multi Package Flip Chip)

無源集成暴露式散熱器多封裝倒裝芯片

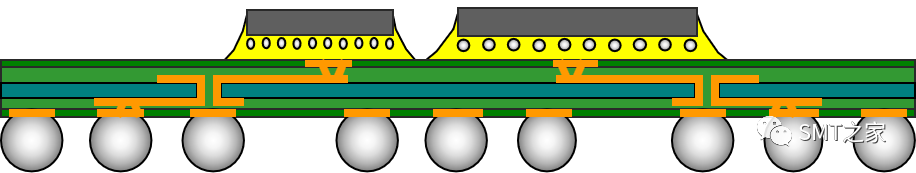

MCM-FCBGA

(Multi-Chip-Module FCBGA)

多芯片模塊FCBGA

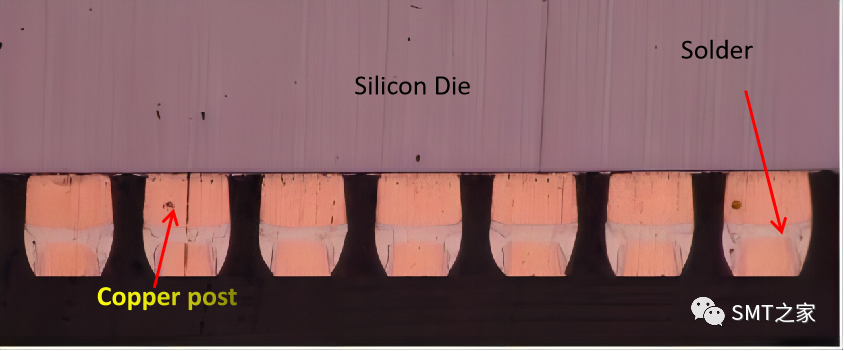

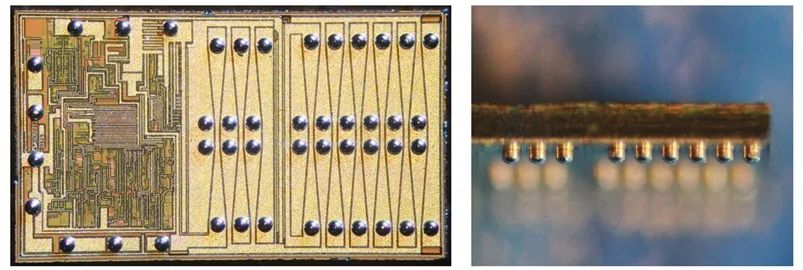

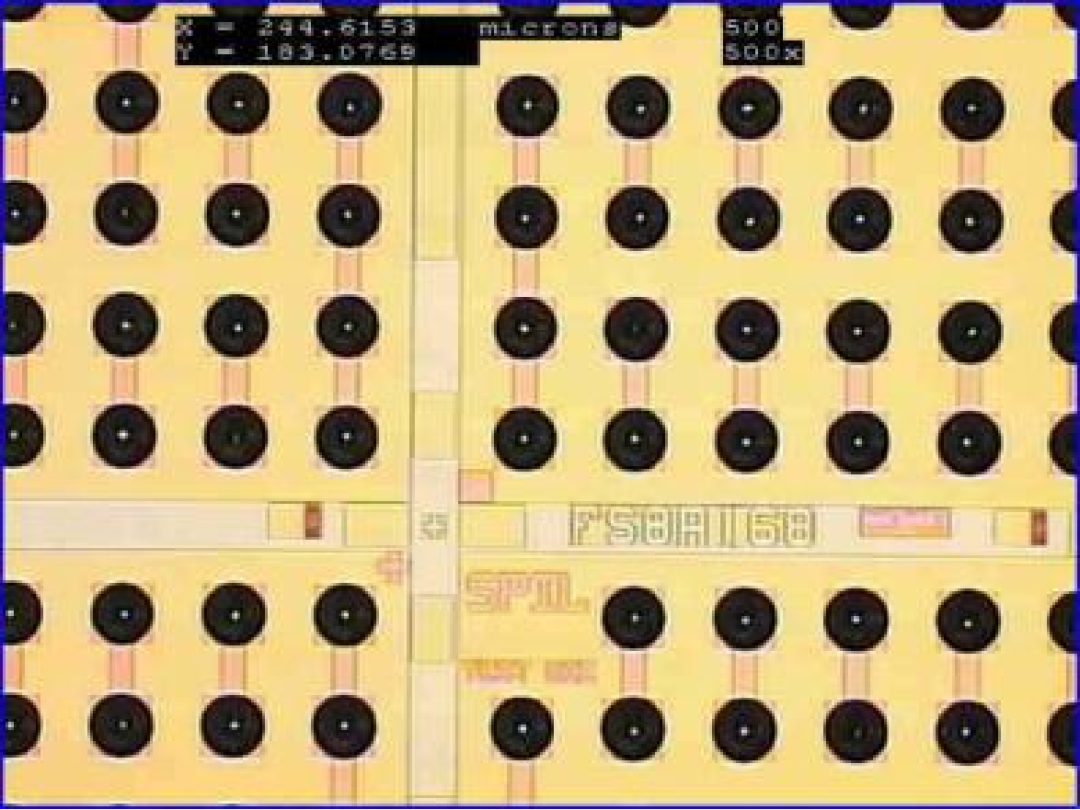

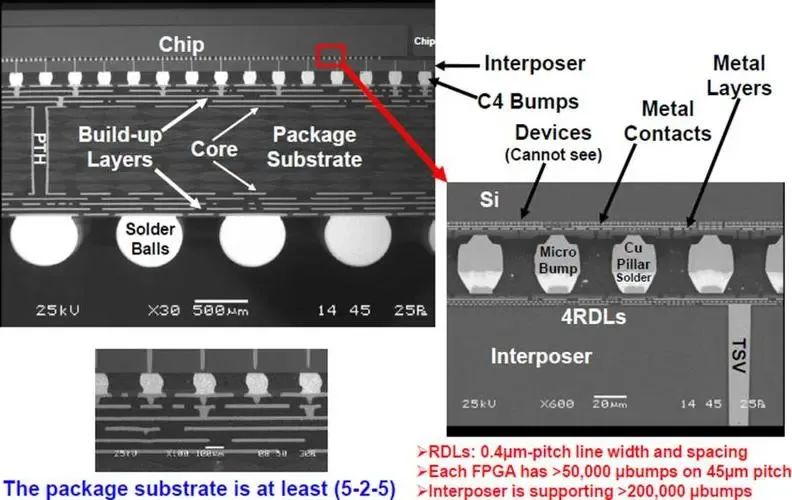

What’s C2 Flip Chip?

C2 is: Chip Connection

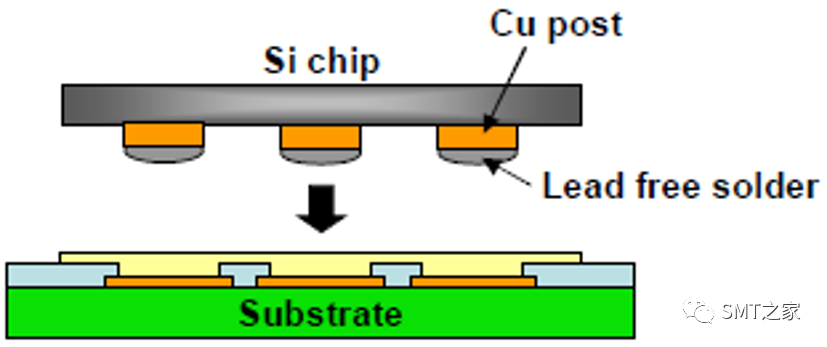

Chip is connected to substrate by copper post

Bump material type: copper post with solder plating

什么是C2倒裝芯片

C2是指:芯片,連接

芯片通過銅柱連接到基板上

凸點材質類型:銅柱鍍錫

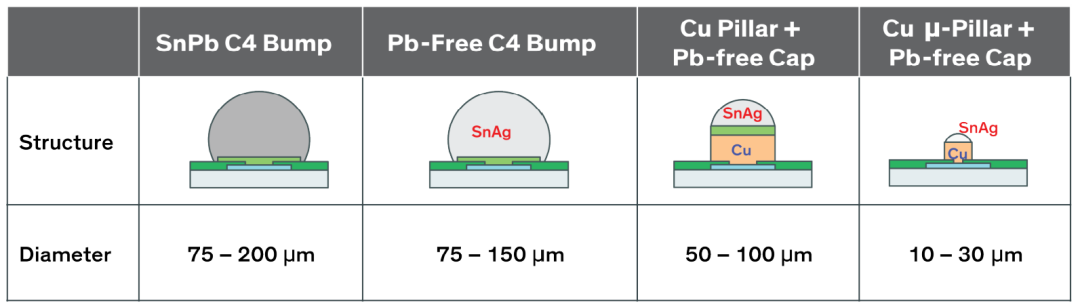

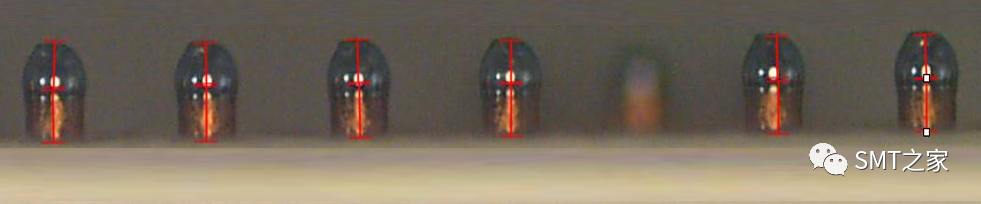

What’s C4 Flip Chip?

C4 is: Controlled Collapsed Chip Connection

Chip is connected to substrate by RDL and Bump

Bump material type: solder, gold

什么是C4倒裝芯片

C4是指:受控,折疊,芯片,連接

芯片通過RDL和Bump連接到基板

凸點材質類型:焊錫、金

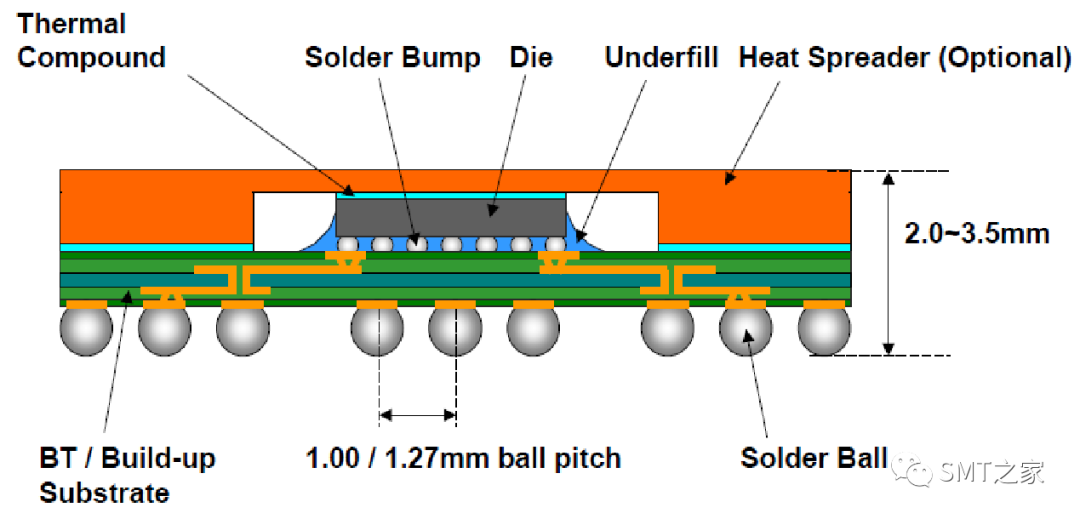

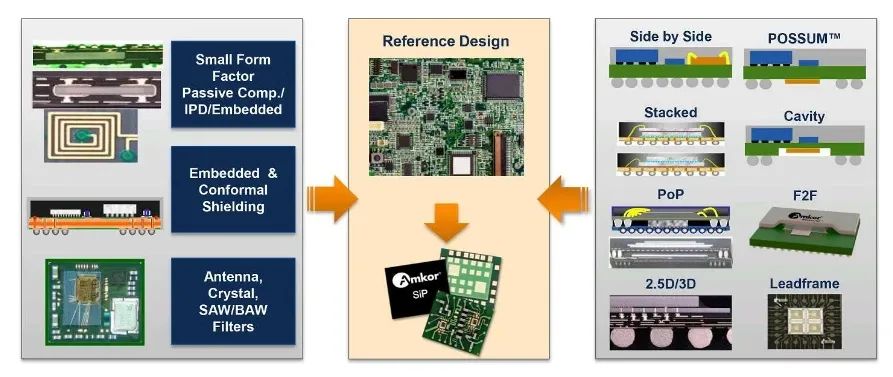

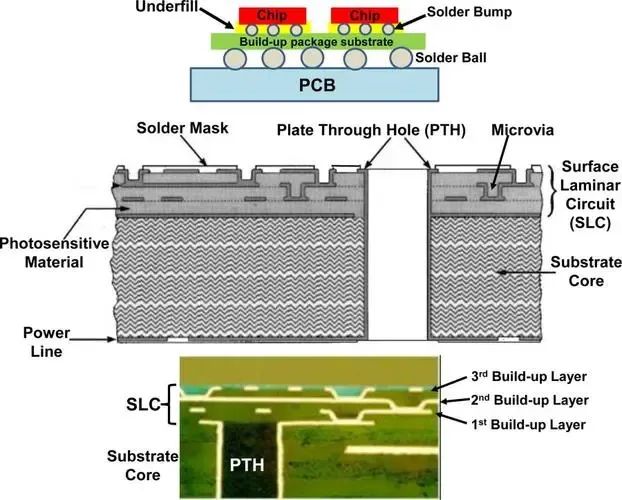

Main Features

Ball Pitch:0.15mm - 1.27mm

Ball diamete:0.01mm -0.20mm

Package size: up to 100mmx100mm

Substrate layer: 4-16 Layers

Ball Count: up to 2912

Target Market: CPU、FPGA、Processor、 Chipset 、Memory、Router、 Switches、 and DSP etc.

主要特點

球間距:0.15毫米–1.27毫米

球直徑:0.01毫米-0.20毫米(10um-200um)

封裝尺寸:最大100mmx100mm

基材層:4-16層

球數:最多2912

目標市場:CPU,FPGA,處理器芯片組、存儲器、路由器、交換機、和DSP等。

Main Benefits

Reduced Signal Inductance

Reduced Power/Ground Inductance

Higher Signal Density

Die Shrink & Reduced Package Footprint

High Speed and High thermal support

主要優點

減小的信號電感

降低電源/接地電感

更高的信號密度

管芯收縮和減少封裝尺寸

高速和高熱支持

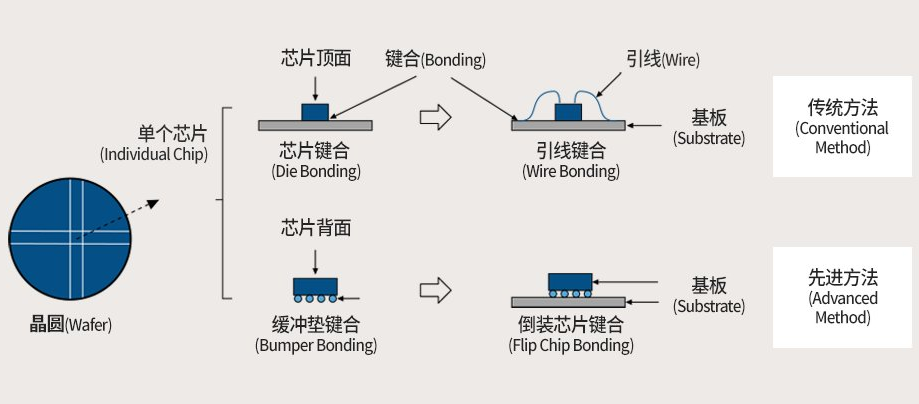

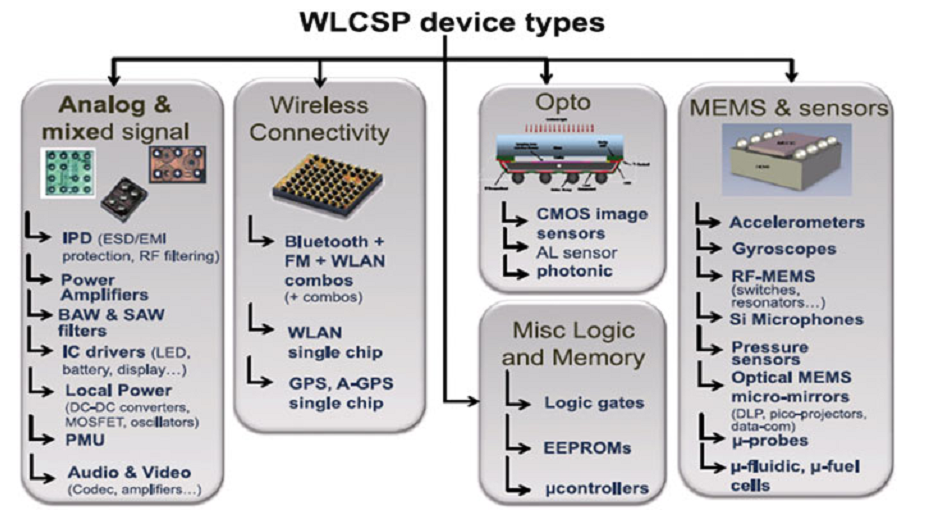

在半導體工藝中,"鍵合"是指將晶圓芯片固定于基板上。

鍵合工藝可分為傳統方法和先進方法兩種類型。

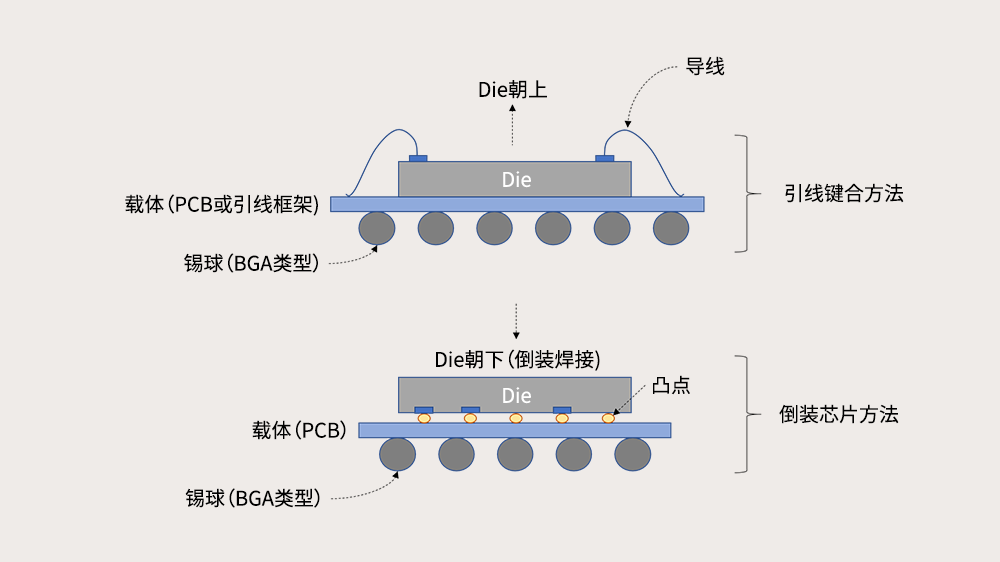

傳統方法采用芯片鍵合(Die Bonding)(或芯片貼裝(Die Attach))和引線鍵合(Wire Bonding),而先進方法則采用IBM于60年代后期開發的倒裝芯片鍵合(Flip Chip Bonding)技術。

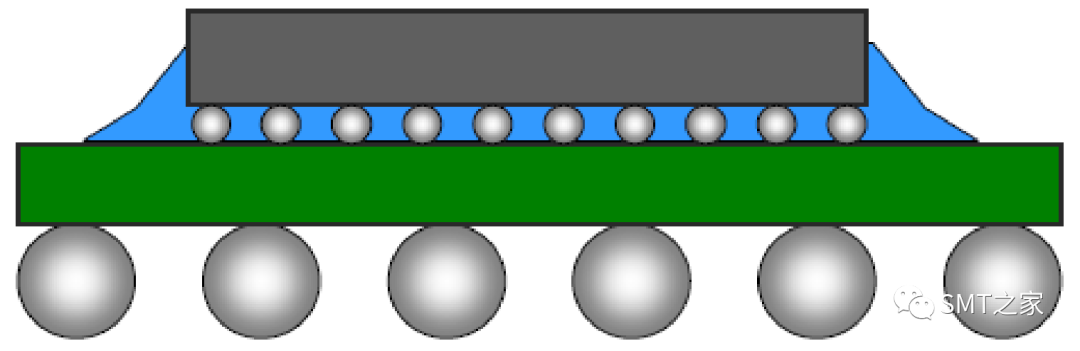

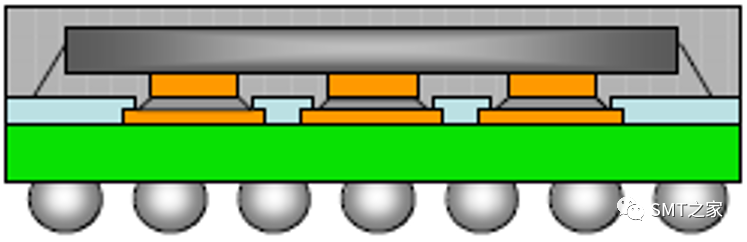

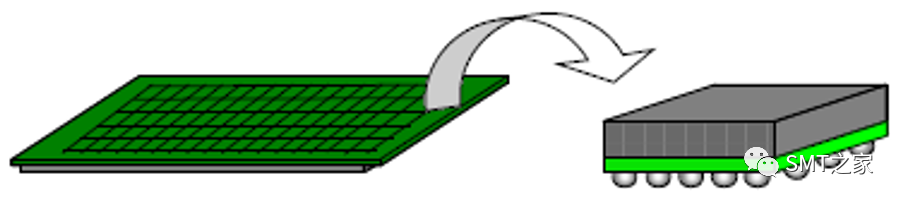

倒裝芯片鍵合技術將芯片鍵合與引線鍵合相結合,并通過在芯片焊盤上形成凸塊(Bump)的方式將芯片和基板連接起來。

就像發動機用于為汽車提供動力一樣,芯片鍵合技術通過將半導體芯片附著到引線框架(Lead Frame)或印刷電路板(PCB, Printed Circuit Board)上,來實現芯片與外部之間的電連接。完成芯片鍵合之后,應確保芯片能夠承受封裝后產生的物理壓力,并能夠消散芯片工作期間產生的熱量。必要時,必須保持恒定導電性或實現高水平的絕緣性。

因此,隨著芯片尺寸變得越來越小,鍵合技術變得越來越重要。

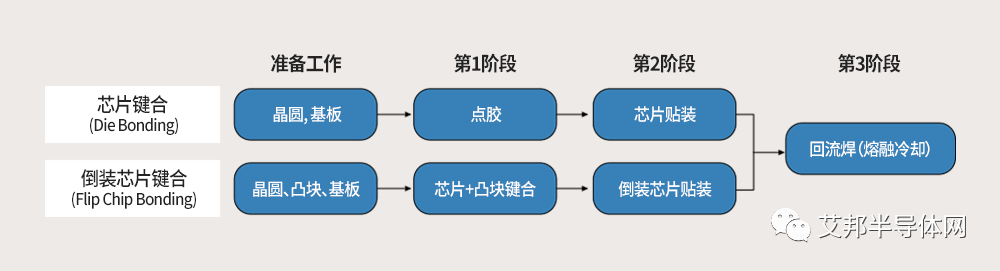

2. 芯片鍵合步驟

芯片鍵合與倒裝芯片鍵合之間的比較

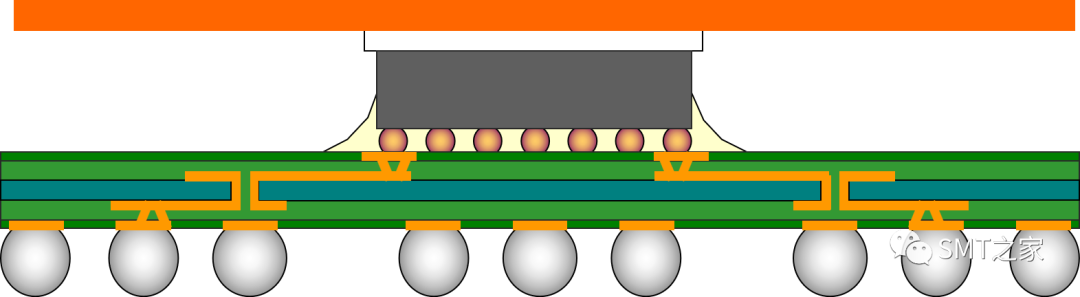

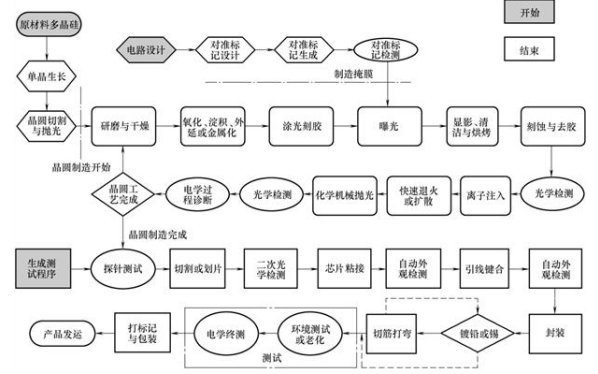

Package Process Flow封裝工藝流程

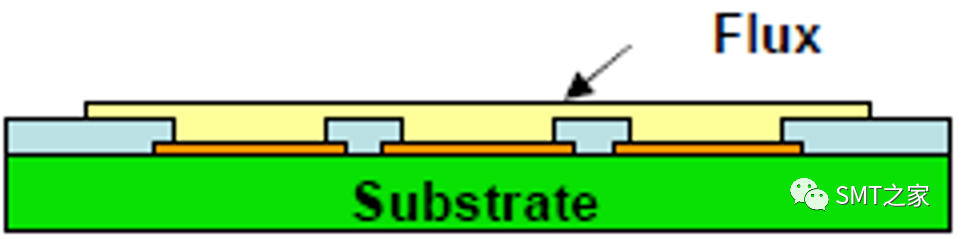

1. Dipping Flux 粘醮助焊劑

2. ChipMount芯片貼裝

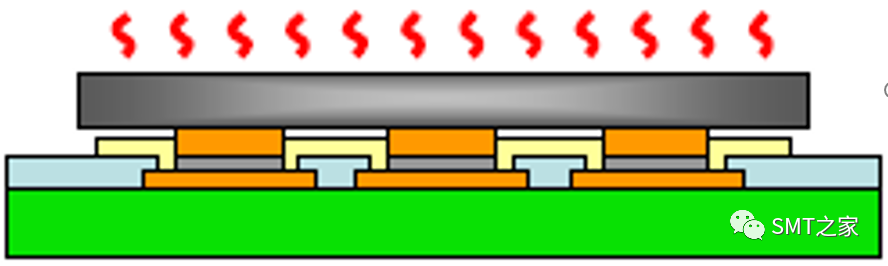

3.Reflow 回流焊接

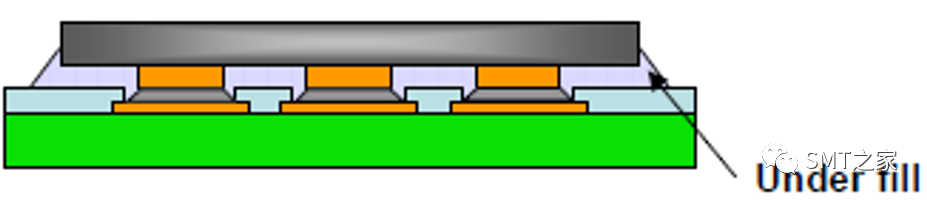

4.Under fill底部填充膠涂覆

5.(Molding),Ball mount 植球

6.Board separation分板

在芯片鍵合過程中,首先需在封裝基板上點上粘合劑。

接著,將芯片頂面朝上放置在基板上。與此相反,倒裝芯片鍵合則是一種更加先進的技術,首先,將稱為"焊球(Solder Ball)"的小凸塊附著在芯片焊盤上。

其次,將芯片頂面朝下放置在基板上。在這兩種方法中,組裝好的單元將經過一個被稱為溫度回流(Temperature Reflow)的通道,該通道可隨著時間的推移調節溫度,以熔化粘合劑或焊球。然后,在其冷卻后將芯片(或凸塊)固定到基板上。

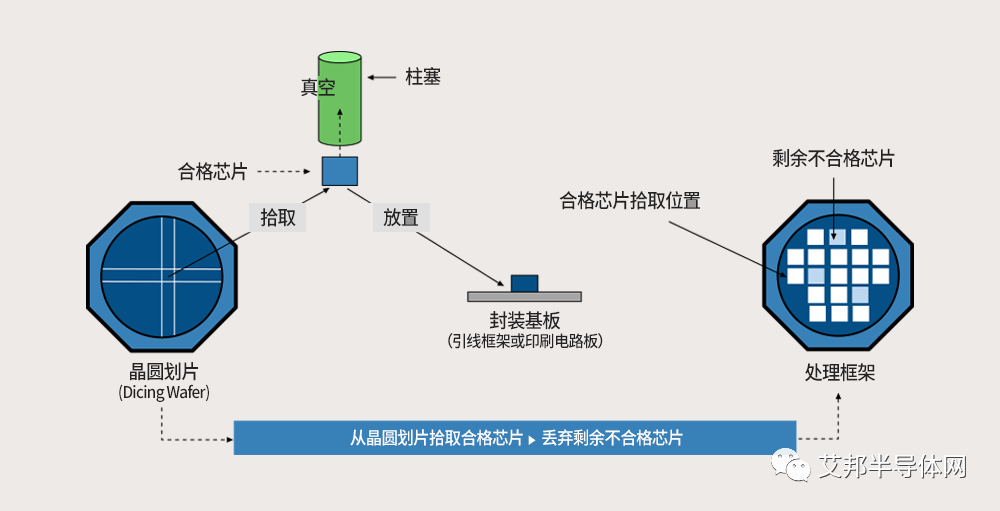

3.芯片拾取與放置(Pick & Place)

芯片拾取和放置

逐個移除附著在切割膠帶上數百個芯片的過程稱為"拾取"。使用柱塞從晶圓上拾取合格芯片并將其放置在封裝基板表面的過程稱為"放置"。這兩項任務合稱為"拾取與放置",均在固晶機1上完成。完成對所有合格芯片的芯片鍵合之后,未移除的不合格芯片將留在切割膠帶上,并在框架回收時全部丟棄。在這個過程中,將通過在映射表2中輸入晶圓測試結果(合格/不合格)的方式對合格芯片進行分類。

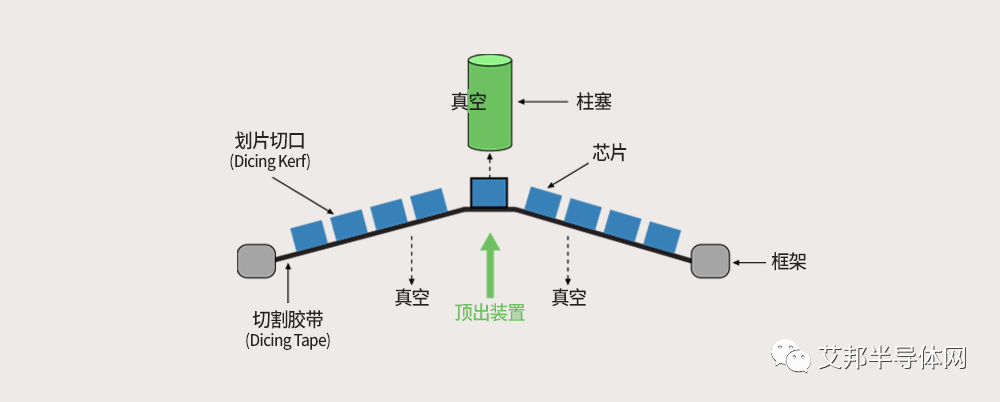

4. 芯片頂出(Ejection)工藝

芯片頂出工藝:在三個方向施加力時的放大圖

完成劃片工藝之后,芯片將被分割成獨立模塊并輕輕附著在切割膠帶(Dicing Tape)上。此時,逐個拾取水平放置在切割膠帶上的芯片并不容易。因為即使使用真空也很難輕易拾取芯片,如果強行拉出,則會對芯片造成物理損壞。

為此,可采用"頂出(Ejection)工藝",通過頂出裝置3對目標芯片施加物理力,使其與其他芯片形成輕微步差,從而輕松拾取芯片。頂出芯片底部之后,可使用帶有柱塞的真空吸拾器從上方拉出芯片。與此同時,使用真空吸拾器將切割膠帶底部拉起,以使晶圓保持平整。

5. 使用環氧樹脂(Epoxy)實現粘合的芯片鍵合工藝

在執行芯片鍵合時,可使用金或銀(或鎳)制成合金,特別是對于大型密封封裝。也可通過使用焊料或含有金屬的糊劑(Power Tr)進行連接,或使用聚合物-聚酰亞胺(Polymer, Polyimide)進行芯片鍵合。在高分子材料中,含銀糊狀或液體型環氧樹脂(Epoxy)相對易于使用且使用頻率較高。

使用環氧樹脂進行芯片鍵合時,可將極少量環氧樹脂精確地點在基板上。將芯片放置在基板上之后,通過回流(Reflow)或固化(Curing),在150°C至250°C的溫度條件下使環氧樹脂硬化,以將芯片和基板粘合在一起。此時,若所使用環氧樹脂的厚度不恒定,則會因膨脹系數差異而導致翹曲(Warpage),從而引起彎曲或變形。因此,盡管使用少量環氧樹脂較為有利,但只要使用環氧樹脂就會發生不同形式的翹曲。

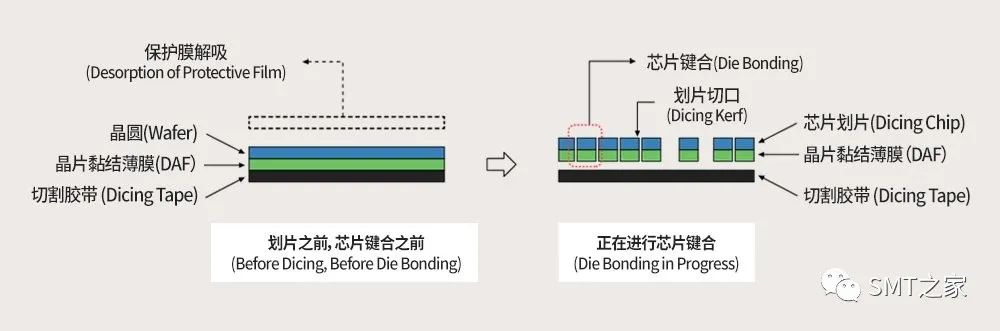

正因為如此,一種使用晶片黏結薄膜(Die Attach Film, DAF)的先進鍵合方法成為近年來的首選方法。盡管DAF具有價格昂貴且難以處理的缺點,但卻易于掌握使用量,簡化了工藝,因此使用率正在逐漸增加。

6. 使用晶片黏結薄膜(DAF)的芯片鍵合工藝

使用晶片黏結薄膜(DAF)的芯片鍵合工藝

DAF是一種附著在晶粒底部的薄膜。相比高分子材料,采用DAF可將厚度調整至非常小且恒定的程度。DAF不僅應用于芯片和基板之間的鍵合,還廣泛應用于芯片與芯片之間的鍵合,從而形成多晶片封裝(MCP)。換句話說,緊密粘合在芯片上的DAF等待切割工藝完成,然后在芯片鍵合過程中發揮自身的作用。

從切割芯片的結構來看,位于芯片底部的DAF支撐著芯片,而切割膠帶則以弱粘合力牽拉著位于其下方的DAF。在這種結構中,要進行芯片鍵合,就需要在移除切割膠帶上的芯片和DAF之后立即將晶粒放置在基板上,并且不得使用環氧樹脂。由于在此過程中可跳過點膠工序,因此環氧樹脂的利弊被忽略,取而代之的是DAF的利弊。

使用DAF時,部分空氣會穿透薄膜,引起薄膜變形等問題。因此,對處理DAF的設備的精度要求格外高。盡管如此,DAF仍然是首選方法,因為它能夠簡化工藝并提高厚度均勻性,從而降低缺陷率并提高生產率。

用于放置芯片的基板類型(引線框架或印刷電路板)不同,執行芯片鍵合的方向也存在很大差異。很久以前,基于PCB的基板已經因其可應用于小尺寸批量生產封裝而得到廣泛使用。相應地,隨著鍵合技術的日益多樣化,用于烘干粘合劑的溫度曲線(Temperature Profile)也在不斷變化。其中一些具有代表性的鍵合方法包括加熱粘接和超聲波粘接。隨著集成技術的不斷提高,封裝工藝繼續朝著超薄方向發展,封裝技術也變得多樣化。

審核編輯:湯梓紅

-

封裝

+關注

關注

125文章

7597瀏覽量

142152 -

smt

+關注

關注

40文章

2834瀏覽量

68516 -

倒裝芯片

+關注

關注

1文章

83瀏覽量

16165 -

半導體制造

+關注

關注

8文章

378瀏覽量

23982

原文標題:【干貨】半導體封裝丨 后工序SMT端Flip chip solution倒裝芯片解決方案(2023精華版),你值得擁有!

文章出處:【微信號:SMT頂級人脈圈,微信公眾號:SMT頂級人脈圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

半導體制造之外延工藝詳解

半導體制程

半導體制造工藝教程的詳細資料免費下載

半導體制造教程之工藝晶體的生長資料概述

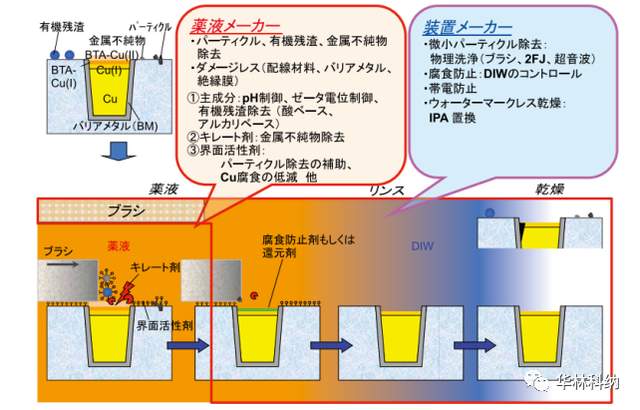

半導體制造CMP工藝后的清洗技術

一文詳解半導體制造工藝

一文詳解半導體制造工藝

評論