完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > 數(shù)字集成電路

數(shù)字集成電路是將元器件和連線集成于同一半導(dǎo)體芯片上而制成的數(shù)字邏輯電路或系統(tǒng)。根據(jù)數(shù)字集成電路中包含的門(mén)電路或元、器件數(shù)量,可將數(shù)字集成電路分為小規(guī)模集成(SSI)電路、中規(guī)模集成MSI電路、大規(guī)模集成(LSI)電路、超大規(guī)模集成VLSI電路和特大規(guī)模集成(ULSI)電路。

數(shù)字集成電路是將元器件和連線集成于同一半導(dǎo)體芯片上而制成的數(shù)字邏輯電路或系統(tǒng)。根據(jù)數(shù)字集成電路中包含的門(mén)電路或元、器件數(shù)量,可將數(shù)字集成電路分為小規(guī)模集成(SSI)電路、中規(guī)模集成MSI電路、大規(guī)模集成(LSI)電路、超大規(guī)模集成VLSI電路和特大規(guī)模集成(ULSI)電路。

數(shù)字集成電路是基于數(shù)字邏輯(布爾代數(shù))設(shè)計(jì)和運(yùn)行的,用于處理數(shù)字信號(hào)的集成電路。根據(jù)集成電路的定義,也可以將數(shù)字集成電路定義為:將元器件和連線集成于同一半導(dǎo)體芯片上而制成的數(shù)字邏輯電路或系統(tǒng)。根據(jù)數(shù)字集成電路中包含的門(mén)電路或元、器件數(shù)量,可將數(shù)字集成電路分為小規(guī)模集成(SSI)電路、中規(guī)模集成MSI電路、大規(guī)模集成(LSI)電路、超大規(guī)模集成VLSI電路、特大規(guī)模集成(ULSI)電路和巨大規(guī)模集成電路(GSI,Giga Scale Integration)。

小規(guī)模集成電路包含的門(mén)電路在10個(gè)以?xún)?nèi),或元器件數(shù)不超過(guò)10個(gè);中規(guī)模集成電路包含的門(mén)電路在10~100個(gè)之間,或元器件數(shù)在100~1000個(gè)之間;大規(guī)模集成電路包含的門(mén)電路在100個(gè)以上,或元器件數(shù)在1,000~10, 000個(gè)之間;超大規(guī)模集成電路包含的門(mén)電路在1萬(wàn)個(gè)以上,或元器件數(shù)在100,000~1,000,000之間;特大規(guī)模集成電路的門(mén)電路在10萬(wàn)個(gè)以上,或元器件數(shù)在1,000,000~10,000,000之間。隨著微電子工藝的進(jìn)步,集成電路的規(guī)模越來(lái)越大,簡(jiǎn)單地以集成元件數(shù)目來(lái)劃分類(lèi)型已經(jīng)沒(méi)有多大的意義了,目前暫時(shí)以“巨大規(guī)模集成電路”來(lái)統(tǒng)稱(chēng)集成規(guī)模超過(guò)1億個(gè)元器件的集成電路。

數(shù)字集成電路是將元器件和連線集成于同一半導(dǎo)體芯片上而制成的數(shù)字邏輯電路或系統(tǒng)。根據(jù)數(shù)字集成電路中包含的門(mén)電路或元、器件數(shù)量,可將數(shù)字集成電路分為小規(guī)模集成(SSI)電路、中規(guī)模集成MSI電路、大規(guī)模集成(LSI)電路、超大規(guī)模集成VLSI電路和特大規(guī)模集成(ULSI)電路。

數(shù)字集成電路是基于數(shù)字邏輯(布爾代數(shù))設(shè)計(jì)和運(yùn)行的,用于處理數(shù)字信號(hào)的集成電路。根據(jù)集成電路的定義,也可以將數(shù)字集成電路定義為:將元器件和連線集成于同一半導(dǎo)體芯片上而制成的數(shù)字邏輯電路或系統(tǒng)。根據(jù)數(shù)字集成電路中包含的門(mén)電路或元、器件數(shù)量,可將數(shù)字集成電路分為小規(guī)模集成(SSI)電路、中規(guī)模集成MSI電路、大規(guī)模集成(LSI)電路、超大規(guī)模集成VLSI電路、特大規(guī)模集成(ULSI)電路和巨大規(guī)模集成電路(GSI,Giga Scale Integration)。

小規(guī)模集成電路包含的門(mén)電路在10個(gè)以?xún)?nèi),或元器件數(shù)不超過(guò)10個(gè);中規(guī)模集成電路包含的門(mén)電路在10~100個(gè)之間,或元器件數(shù)在100~1000個(gè)之間;大規(guī)模集成電路包含的門(mén)電路在100個(gè)以上,或元器件數(shù)在1,000~10, 000個(gè)之間;超大規(guī)模集成電路包含的門(mén)電路在1萬(wàn)個(gè)以上,或元器件數(shù)在100,000~1,000,000之間;特大規(guī)模集成電路的門(mén)電路在10萬(wàn)個(gè)以上,或元器件數(shù)在1,000,000~10,000,000之間。隨著微電子工藝的進(jìn)步,集成電路的規(guī)模越來(lái)越大,簡(jiǎn)單地以集成元件數(shù)目來(lái)劃分類(lèi)型已經(jīng)沒(méi)有多大的意義了,目前暫時(shí)以“巨大規(guī)模集成電路”來(lái)統(tǒng)稱(chēng)集成規(guī)模超過(guò)1億個(gè)元器件的集成電路。

內(nèi)部設(shè)計(jì)

數(shù)字電路的組成:組合邏輯+寄存器(觸發(fā)器)。組合邏輯就是由基本門(mén)組成的函數(shù),其輸出只會(huì)跟當(dāng)前的輸入有關(guān),在上面的例子中,第一個(gè)圖就是組合邏輯,只完成邏輯運(yùn)算;而時(shí)序電路除了包含基本門(mén)之外,還包含存儲(chǔ)元件用例保存過(guò)去的信息,時(shí)序電路的穩(wěn)態(tài)輸出不僅取決于當(dāng)前的輸入,還與過(guò)去的輸入所形成狀態(tài)有關(guān)。第二個(gè)圖就是時(shí)序電路,在完成邏輯運(yùn)算的同時(shí),還可以把處理結(jié)果暫存起來(lái),用以下一次的運(yùn)算。

從功能上來(lái)看,數(shù)字集成電路內(nèi)部可以分為數(shù)據(jù)通路(Data-path,也稱(chēng)為數(shù)據(jù)路徑)和控制邏輯兩大部分。這兩大部分都是由大量的時(shí)序邏輯電路集成的,而且絕大部分都是同步的時(shí)序電路,因?yàn)闀r(shí)序電路被多個(gè)觸發(fā)器或寄存器分成若干節(jié)點(diǎn),而這些觸發(fā)器在時(shí)鐘的控制下會(huì)按同樣的節(jié)拍來(lái)工作,可以簡(jiǎn)化設(shè)計(jì)。在長(zhǎng)期的設(shè)計(jì)過(guò)程中,已經(jīng)積累了很多標(biāo)準(zhǔn)的通用單元,比如選擇器(也叫多路器,可以從多個(gè)輸入數(shù)據(jù)中選一個(gè)輸出)、比較器(用于比較兩個(gè)數(shù)的大小)、加法器、乘法器、移位寄存器等等,這些單元電路形狀規(guī)則,便于集成(這也是數(shù)字電路在集成電路中得到更好的發(fā)展的原因)。這些單元按設(shè)計(jì)要求連接在一起,形成數(shù)據(jù)通路,待處理的數(shù)據(jù)從輸入端經(jīng)過(guò)這條通路到輸出端,便得到處理后的結(jié)果。同時(shí),還需要由專(zhuān)門(mén)設(shè)計(jì)的控制邏輯,控制數(shù)據(jù)通路的各組成部件,按各自的功能要求和特定的時(shí)序關(guān)系和來(lái)配合工作。

數(shù)字集成電路必讀的幾本書(shū)

《數(shù)字集成電路——電路、系統(tǒng)與設(shè)計(jì)》

前端要學(xué)verilog和VHDL的教材

數(shù)字后端有《數(shù)字集成電路物理設(shè)計(jì)》

verilog一般用夏宇聞的教材,也有很多人說(shuō)他寫(xiě)的不好,但是硬件描述語(yǔ)言重在使用,死學(xué)無(wú)用,找本書(shū)作參考就好。用其它教材也一樣。

網(wǎng)上流傳的英文數(shù)字集成電路公開(kāi)課,有興趣和能力可以去試試。

數(shù)字芯片設(shè)計(jì)入門(mén)

數(shù)字芯片的設(shè)計(jì),可以這樣來(lái)分類(lèi)。

第一類(lèi)是Physical Design。我原先答案中所說(shuō)的第一層和第二層就是這塊的內(nèi)容。

這塊內(nèi)容的特點(diǎn)是什么呢?簡(jiǎn)而言之就是你要實(shí)際的去設(shè)計(jì)物理電路,直接面對(duì)silicon wafer這張畫(huà)布去布線走線,怎么走metal1 metal2 直至metal6甚至,如何在不同層間打via。擺放你的Transistor, 你的gate,乃至你的SRAM,ALU。

所以你要對(duì)從Transistor Level到Gate Level乃至更高層的知識(shí)很熟悉,物理上的特性要了解。從最基礎(chǔ)的Transistor的各種First Order Effect,Second Order Effect。到更高level的比如SRAM,DRAM怎么個(gè)構(gòu)造怎么個(gè)功能。

現(xiàn)代的數(shù)電技術(shù)必須要注重三個(gè)optimizing:area,delay,power consumption。一些工程上的經(jīng)驗(yàn),比如logical effort估算,就是怎么讓pathdelay最短。對(duì)各種leakage current的掌握才能做低能耗設(shè)計(jì)。

第二類(lèi)是 ASIC RTL design了。

簡(jiǎn)單的說(shuō)就是寫(xiě)Verilog或VHDL code,也有用SystemC的,然后用code來(lái)描述功能。這一步叫做RTL Design。

RTL改到功能對(duì)了后要用Tool來(lái)Synthesis,比如Synopsis的Design Compiler。Synthesis是什么呢,就是它會(huì)生成一個(gè)與你的code設(shè)計(jì)的電路等效的電路,但它的這個(gè)是優(yōu)化了的,你所有的冗余它會(huì)自動(dòng)幫你修掉,你重復(fù)的路徑它會(huì)幫你刪掉。Synthesis完你的實(shí)際電路就出來(lái)了,你可以用GUI的Design Vision里面的功能來(lái)看這個(gè)電路。但是Synthesis是要依據(jù)一系列的rules來(lái)的,這個(gè)rules就是你要用一個(gè)tcl文件用tcl的語(yǔ)法寫(xiě)出來(lái)給你的tool,你的tool在這些rules的限制下把你原先的電路optimize出來(lái),這時(shí)候往往會(huì)有一個(gè)slack violate。什么叫slack violate呢?就是比如你設(shè)計(jì)了一個(gè)DDR,按你的rules里面要求它一個(gè)周期應(yīng)該在1.5ns內(nèi),但你設(shè)計(jì)的不好,導(dǎo)致Design Compiler無(wú)論怎樣都沒(méi)法把最長(zhǎng)的path縮到1.5ns內(nèi),這時(shí)候你就violate了,就得改。直到改過(guò)為止。

Synthesis搞定后還有Post-syn,就是把Synthesis出來(lái)的等效優(yōu)化電路再重新跑一次,看看功能是不是仍然正確。否則改之。

最后再用軟件自動(dòng)布線生成layout。

第三類(lèi)是Verification,

Verification是在你的design最后流片前要做的驗(yàn)證。這個(gè)非常重要,有些startup就是因?yàn)閂erification沒(méi)搞好直接就破產(chǎn)了。要會(huì)這一類(lèi)知識(shí)你要先有很好的軟件基礎(chǔ),OOP比如C++,還有SystemVerilog,C 最好要會(huì)。然后去學(xué)Verification的知識(shí),所謂OVM UVM。

通常一個(gè)design做出來(lái)后(就是上面的第二類(lèi)全部完成后)會(huì)送去流片,但一個(gè)asic的流片往往要好幾周,甚至數(shù)月。對(duì)于公司的產(chǎn)品競(jìng)爭(zhēng)來(lái)說(shuō),及時(shí)的推向市場(chǎng)是很關(guān)鍵的。于是我們就會(huì)先拿FPGA來(lái)做prototyping,把電路先燒到FPGA里面,當(dāng)然有的時(shí)候還需要一些peripherals的配合,這些都是要學(xué)的。

第四類(lèi)叫Testing

Testing是板子出來(lái)后做的測(cè)試,里面又有validation等等。現(xiàn)在多用的DFT技術(shù),怎么生成test pattern,怎么ATPG都要去學(xué)。

第五類(lèi)可以稱(chēng)之為Architecture

什么是Architecture,比如:

Processor怎么設(shè)計(jì)?怎么從single cycle CPU變?yōu)?multcycle,最終進(jìn)化為pipeline,每一個(gè)stage怎么運(yùn)轉(zhuǎn)的。

Memory體系怎么設(shè)計(jì)?Cache coherence,以及各種protocol,怎么在不同level的cache之間保證數(shù)據(jù)的正確。

現(xiàn)在處理器常用的Out of Order Execution,各種Tomasulo algorithm實(shí)現(xiàn)。

Branch Prediction: 簡(jiǎn)言之就是處理器遇到IF了怎么判斷?各種Branch Predictor, 從簡(jiǎn)單的基于history到TWO-LEVEL PREDICTORS,到COMBINING PREDICTORS

Multiprocessor技術(shù)。

等等。

Architecture最尖端的技術(shù)一直在Intel在AMD最核心的實(shí)驗(yàn)室里。學(xué)校教的,哪怕是我們學(xué)校教的也不過(guò)是已經(jīng)廣為接受的設(shè)計(jì)。

草草地寫(xiě)在這里,排版什么的就見(jiàn)諒了。

又想起來(lái)一條不知能不能算作數(shù)電設(shè)計(jì),因?yàn)殛P(guān)系很密切就寫(xiě)在這里吧。

這一類(lèi)叫做fabrication。

臺(tái)灣的TSMC,IBM的foundry。TSMC的22nm(還是另外的?記不清了)的技術(shù)很頂尖。這些就是上面第二類(lèi)說(shuō)的,板子設(shè)計(jì)好了送去制作。

從最開(kāi)始怎么做wafer,怎用silicon,用GaAs等melt做引子生長(zhǎng)出來(lái)純度高的圓柱的單晶硅。以及怎么把你設(shè)計(jì)的layout圖里面的內(nèi)容一層層的蝕刻上去。等等。這里面其實(shí)又可以分很多類(lèi),涉及到很多NanoTechnology。

=================14年的答案====================

寫(xiě)在前面:因?yàn)轭}主問(wèn)的是“數(shù)字芯片設(shè)計(jì)“,所以我主要介紹VLSI方面的名錄。但實(shí)際上學(xué)VLSI的基本都會(huì)學(xué)一些compute architecture方面的東西(VLSI主要就是干這個(gè)的啊),所以以后什么時(shí)候有空再來(lái)補(bǔ)吧。

--------------------------------------------------------------------------------------------

入門(mén): MOS VLSI Circuit Design,教材:CMOS Digital Integrated Circuits, S. –M. Kang and Y. Leblebici, Mc Graw Hill, 3 rd edition, 2003.

貌似國(guó)內(nèi)某網(wǎng)站可搜到中文翻譯版,《CMOS數(shù)字集成電路:分析與設(shè)計(jì)(第3版)2》

這一步只需要最基礎(chǔ)的模電數(shù)電知識(shí)以及基本的電路理論,然后

1.學(xué)會(huì)分析和設(shè)計(jì)基本的digital IC,知道怎么分析計(jì)算最基本的area, delay and power minimization。

2.學(xué)習(xí)從device level到 register level的搭建

3.學(xué)習(xí)MOS devices, logic cells, and critical interconnect and cell characteristics that determine the performance of VLSI circuits.

當(dāng)然學(xué)digital IC非常重要的一點(diǎn)就是要用EDA做設(shè)計(jì)和仿真,比如用synopsis的軟件,比如Cadence Virtuoso,從schematic設(shè)計(jì)到layout設(shè)計(jì),再最后仿真分析。

第二層:VLSI System Design

這一步主要學(xué)的是

1.前面各種知識(shí)點(diǎn)前加advanced

2.各種optimization,包括area,power,delay三大方面,學(xué)習(xí)各種optimization的切入角度,實(shí)現(xiàn)方法。做到chip level design。

3.除此之外還要學(xué)習(xí)data path and memory design之類(lèi)的東西,

4.到這一層你要開(kāi)始學(xué)一門(mén)script language了,主流是perl。

CMOS VLSI Design A Circuits and Systems Perspective 4th Edition

搜了下貌似也有中文對(duì)應(yīng)的翻譯書(shū)《CMOS超大規(guī)模集成電路設(shè)計(jì)(第3版)》

音響集成電路(Audio Integrated Circuit,簡(jiǎn)稱(chēng)IC)是一種用于處理音頻信號(hào)的集成電路。它們可以是數(shù)字的,也可以是模擬的,具體取決于...

2024-09-24 標(biāo)簽:音響集成電路音頻信號(hào)數(shù)字集成電路 252 0

SoC(System on Chip,系統(tǒng)級(jí)芯片)是 數(shù)字芯片 的一種。SoC芯片是數(shù)字集成電路的一種,它通過(guò)將一個(gè)或多個(gè)數(shù)字電路模塊、內(nèi)存、CPU等幾...

2024-09-23 標(biāo)簽:soc數(shù)字集成電路模擬芯片 546 0

數(shù)字集成電路(Digital IC)具有集成度極高、體積很小、功耗超低、系統(tǒng)可靠性高及便于電子系統(tǒng)(如計(jì)算機(jī))處理等特點(diǎn)。數(shù)字集成電路(如 CPU 芯片...

2023-11-15 標(biāo)簽:存儲(chǔ)器計(jì)算機(jī)數(shù)字集成電路 1443 0

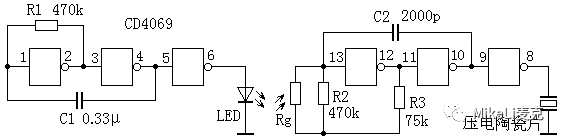

多諧振蕩器可以發(fā)出音頻信號(hào),驅(qū)動(dòng)喇叭發(fā)聲。但是這種頻率固定的信號(hào)時(shí)間長(zhǎng)了會(huì)使人厭倦。為此,各種調(diào)制音頻信號(hào)被廣泛使用。光敏電阻可以用來(lái)解決聲音頻率的變化問(wèn)題。

2023-10-11 標(biāo)簽:數(shù)字電路信號(hào)發(fā)生器光敏電阻 1673 0

數(shù)字集成電路的測(cè)試主要包括直流參數(shù)測(cè)試 (DC Test)、交流參數(shù)測(cè)試(AC Test)、功能測(cè)試(Function Test)、可測(cè)性設(shè)計(jì)(DFT)...

2023-05-26 標(biāo)簽:集成電路測(cè)試系統(tǒng)電源電壓 3857 0

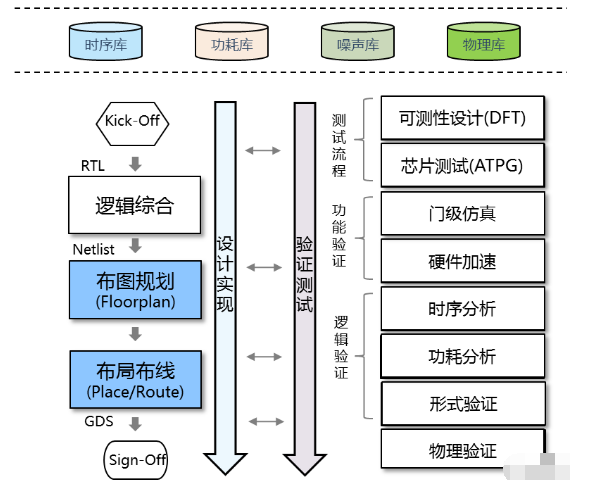

數(shù)字集成電路芯片的設(shè)計(jì)流程由一系列的設(shè)計(jì)實(shí)現(xiàn)和驗(yàn)證測(cè)試過(guò)程組成(圖1)。首先是功能定義,它描述了對(duì)芯片功能和性能參數(shù)的要求,我們使用系統(tǒng)設(shè)計(jì)工具設(shè)計(jì)出方...

2021-06-06 標(biāo)簽:集成電路數(shù)字集成電路 2.2萬(wàn) 0

通常可以將每一塊集成電路芯片(以下簡(jiǎn)稱(chēng)為“芯片”)看成是帶有電源端,輸入、輸出端,且具有一定功能的黑色方塊,對(duì)它的內(nèi)部電路結(jié)構(gòu)可以不去了解,只要判明它的...

2020-09-16 標(biāo)簽:集成電路數(shù)字集成電路 2994 0

基于邏輯門(mén)搭建的用于處理數(shù)字信號(hào)的集成電路

數(shù)字電路中的數(shù)字信號(hào)是指在時(shí)間上離散,在數(shù)值上也離散,且數(shù)值的大小和增減都是量化單位的整數(shù)倍的一類(lèi)信號(hào)。

FPGA 有一個(gè)響亮的別名——“萬(wàn)能芯片”,它是一種能夠通過(guò)軟件更改、配置器件內(nèi)部連接結(jié)構(gòu)和邏輯單元,完成既定設(shè)計(jì)功能的數(shù)字集成電路。雖然FPGA問(wèn)世的...

2018-07-13 標(biāo)簽:fpgaasic數(shù)字集成電路 1464 0

74VHC00FT CMOS數(shù)字集成電路硅單片英文手冊(cè)立即下載

類(lèi)別:IC datasheet pdf 2024-11-05 標(biāo)簽:CMOS數(shù)字集成電路

74VHCT125AFT,74VHCT126AFT CMOS數(shù)字集成電路硅單片規(guī)格書(shū)立即下載

類(lèi)別:IC datasheet pdf 2024-10-16 標(biāo)簽:CMOS數(shù)字集成電路

高速電路電源分配網(wǎng)絡(luò)的時(shí)域分析與設(shè)計(jì)立即下載

類(lèi)別:電子資料 2024-09-21 標(biāo)簽:去耦電容數(shù)字集成電路電源完整性

74VHCT125AFT,74VHCT126AFT CMOS數(shù)字集成電路硅單片英文手冊(cè)立即下載

類(lèi)別:IC datasheet pdf 2024-08-09 標(biāo)簽:CMOS數(shù)字集成電路

CMOS硅單片數(shù)字集成電路TC358743XBG數(shù)據(jù)手冊(cè)立即下載

類(lèi)別:IC中文資料 2022-08-04 標(biāo)簽:CMOS數(shù)字集成電路

數(shù)字集成電路設(shè)計(jì)透視資料下載立即下載

類(lèi)別:電子教材 2021-11-03 標(biāo)簽:數(shù)字集成電路

數(shù)字集成電路-設(shè)計(jì)透視圖(第2版)pdf立即下載

類(lèi)別:IC datasheet pdf 2021-09-28 標(biāo)簽:數(shù)字集成電路

數(shù)字集成電路分析與設(shè)計(jì):深亞微米工藝立即下載

類(lèi)別:電子資料 2021-05-12 標(biāo)簽:MOS數(shù)字集成電路深亞微米

自制數(shù)字集成電路實(shí)驗(yàn)板說(shuō)明書(shū)立即下載

類(lèi)別:電子資料 2021-04-15 標(biāo)簽:數(shù)字集成電路

數(shù)字集成電路設(shè)計(jì)與技術(shù)立即下載

類(lèi)別:電子資料 2021-04-12 標(biāo)簽:半導(dǎo)體數(shù)字集成電路

東芝TC7WZ74FK的特點(diǎn)與應(yīng)用探討

在工程師和開(kāi)發(fā)者不斷追求更高效、可靠且高性能組件的過(guò)程中,選擇合適的數(shù)字集成電路(IC)成為一個(gè)關(guān)鍵決策。東芝的TC7WZ74FK CMOS數(shù)字集成電路...

2024-11-15 標(biāo)簽:步進(jìn)電機(jī)數(shù)字集成電路 149 0

芯片是一種集成電路,由大量的晶體管構(gòu)成。不同的芯片有不同的集成規(guī)模,大到幾億;小到幾十、幾百個(gè)晶體管。 芯片的工作原理是將電路制造在半導(dǎo)體芯片表面上從而...

2021-12-10 標(biāo)簽:芯片數(shù)字集成電路 9.1萬(wàn) 0

國(guó)微思爾芯完成新一輪重磅級(jí)融資 引領(lǐng)EDA發(fā)展縱情向前

國(guó)微思爾芯創(chuàng)立于2003年,十多年來(lái)一直專(zhuān)注于EDA解決方案研發(fā),是上海市重點(diǎn) EDA 企業(yè)。國(guó)微思爾芯自主研發(fā)的EDA工具,是超大規(guī)模數(shù)字集成電路(V...

2020-09-01 標(biāo)簽:處理器芯片設(shè)計(jì)eda 954 0

搶占新機(jī)加入有前途和錢(qián)途的集成電路企業(yè)

2018-07-31 標(biāo)簽:數(shù)字集成電路半導(dǎo)體行業(yè)半導(dǎo)體企業(yè) 272 0

Tanner EDA:數(shù)字集成電路原理與設(shè)計(jì)課程教學(xué)的IC設(shè)計(jì)工具

“數(shù)字集成電路(Integrated Circuit,簡(jiǎn)稱(chēng)IC)原理與設(shè)計(jì)”是為高等學(xué)校電子、通信、機(jī)電等工科電子類(lèi)專(zhuān)業(yè)的高年級(jí)本科生和碩士生開(kāi)設(shè)的一門(mén)...

2018-04-28 標(biāo)簽:EDA數(shù)字集成電路 1.6萬(wàn) 0

美高森美選擇英特爾代工服務(wù)開(kāi)發(fā)數(shù)字集成電路

致力于提供幫助功率管理、安全、可靠與高性能半導(dǎo)體技術(shù)產(chǎn)品的領(lǐng)先供應(yīng)商美高森美公司(Microsemi Corporation,紐約納斯達(dá)克交易所代號(hào):M...

2013-05-09 標(biāo)簽:英特爾數(shù)字集成電路美高森美 848 0

數(shù)字集成電路實(shí)驗(yàn)板是一種學(xué)生用來(lái)進(jìn)行數(shù)字集成電路基本實(shí)驗(yàn)的學(xué)具。它借鑒面包板插接電路的特點(diǎn),并帶有基本數(shù)字部件,能簡(jiǎn)化實(shí)驗(yàn)步驟,突出實(shí)驗(yàn)主體,提高插接電...

2012-07-12 標(biāo)簽:數(shù)字集成電路 1.0萬(wàn) 0

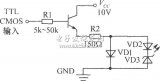

數(shù)字集成電路控制的兩只發(fā)光管交替閃爍發(fā)光

是由TTL或CMOS數(shù)字集成電路控制,通過(guò)三極管導(dǎo)通驅(qū)動(dòng)兩只發(fā)光管交替閃爍發(fā)光。

2011-09-28 標(biāo)簽:數(shù)字集成電路 1231 0

數(shù)字集成電路實(shí)現(xiàn)流水燈設(shè)計(jì)

采用數(shù)字集成電路的控制方法,結(jié)合十進(jìn)制計(jì)數(shù)器/譯碼電路設(shè)計(jì)了該 流水燈 控制系統(tǒng)。該系統(tǒng)由電源、時(shí)鐘電路、計(jì)數(shù)器和譯碼顯示電路4部分組成。能實(shí)現(xiàn)任意方式...

2011-09-27 標(biāo)簽:流水燈數(shù)字集成電路 3.4萬(wàn) 2

數(shù)字集成電路使用注意事項(xiàng) 數(shù)字集成電路在電子產(chǎn)晶中使用得十分廣泛,但因其功能及結(jié)構(gòu)的特殊性,如果使用不當(dāng),極易損壞。下

2010-07-28 標(biāo)簽:數(shù)字集成電路 2023 1

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語(yǔ)言教程專(zhuān)題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無(wú)刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺(jué) | 無(wú)人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹(shù)莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |