完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

標簽 > MPU

MPU有兩種意思,微處理器和內存保護單元。MPU是單一的一顆芯片,而芯片組則由一組芯片所構成,早期甚至多達7、8顆,但目前大多合并成2顆,一般稱作北橋(North Bridge)芯片和南橋(South Bridge)芯片。

MPU有兩種意思,微處理器和內存保護單元。MPU是單一的一顆芯片,而芯片組則由一組芯片所構成,早期甚至多達7、8顆,但目前大多合并成2顆,一般稱作北橋(North Bridge)芯片和南橋(South Bridge)芯片。MPU是計算機的計算、判斷或控制中心,有人稱它為”計算機的心臟”。

MPU[1] (Microprocessor Unit)微處理器微機中的中央處理器(CPU)稱為微處理器(MPU),是構成微機的核心部件,也可以說是微機的心臟。它起到控制整個微型計算機工作的作用,產生控制信號對相應的部件進行控制,并執行相應的操作。在微機中,CPU被集成在一片超大規模集成電路芯片上,稱為微處理器(MPU),微處理器插在主板的cpu插槽中。通常所說的16位機、32位機是指該計算機中微處理器內部數據總線的寬度,也就是CPU可同時操作的二進制數的位數。目前常用的CPU都是64位的,即一次可傳送64位二進制數。

MPU有兩種意思,微處理器和內存保護單元。MPU是單一的一顆芯片,而芯片組則由一組芯片所構成,早期甚至多達7、8顆,但目前大多合并成2顆,一般稱作北橋(North Bridge)芯片和南橋(South Bridge)芯片。MPU是計算機的計算、判斷或控制中心,有人稱它為”計算機的心臟”。

MPU[1] (Microprocessor Unit)微處理器微機中的中央處理器(CPU)稱為微處理器(MPU),是構成微機的核心部件,也可以說是微機的心臟。它起到控制整個微型計算機工作的作用,產生控制信號對相應的部件進行控制,并執行相應的操作。在微機中,CPU被集成在一片超大規模集成電路芯片上,稱為微處理器(MPU),微處理器插在主板的cpu插槽中。通常所說的16位機、32位機是指該計算機中微處理器內部數據總線的寬度,也就是CPU可同時操作的二進制數的位數。目前常用的CPU都是64位的,即一次可傳送64位二進制數。

功能構成

微處理器的功能結構主要包括:運算器、控制器、寄存器三部分:運算器的主要功能就是進行算術運算和邏輯運算。控制器是整個微機系統的指揮中心,其主要作用是控制程序的執行。包括對指令進行譯碼、寄存,并按指令要求完成所規定的操作,即指令控制、時序控制和操作控制。寄存器用來存放操作數、中間數據及結果數據。

主要技術參數

CPU質量的高低直接決定了一個計算機系統的檔次,而CPU的主要技術特性可以反映出CPU的基本性能。CPU的主要技術參數如下:⑴ CPU可以同時處理的二進制數據的位數,即字長;⑵ 時鐘頻率;⑶ 高速緩沖存儲器(Cache)的容量和速率;⑷ 地址總線和數據總線的寬度;⑸ 制造工藝。

內存保護

內存保護單元(ARM體系方面)(MPU,Memory Protection Unit),MPU中一個域就是一些屬性值及其對應的一片內存。這些屬性包括:起始地址、長度、讀寫權限以及緩存等。ARM940具有不同的域來控制指令內存和數據內存。內核可以定義8對區域,分別控制8個指令和數據內存區域。域和域可以重疊并且可以設置不同的優先級。域的啟始地址必須是其大小的整數倍。另外,域的大小可以4K到4G間任意一個2的指數,如4K,8K,16K.。。。。英漢計算機詞匯= Main Processing Unit,主處理機; = Memory Protection Unit, 存儲器保護設備; = MicroProcessing Unit, 微處理器[機]; = MicroProgrammed control Unit, 微程序控制器; = MicroProgramming Unit, 微程序設計部件; = Miniature Power Unit, 小型電源設備

MCU和MPU有什么區別

MPU有兩種意思,微處理器和內存保護單元。MPU是單一的一顆芯片,而芯片組則由一組芯片所構成,早期甚至多達7、8顆,但目前大多合并成2顆,一般稱作北橋(North Bridge)芯片和南橋(South Bridge)芯片。MPU是計算機的計算、判斷或控制中心,有人稱它為”計算機的心臟”。

中央處理器(CPU,英語:Central Processing Unit),是電子計算機的主要設備之一,電腦中的核心配件。其功能主要是解釋計算機指令以及處理計算機軟件中的數據。電腦中所有操作都由CPU負責讀取指令,對指令譯碼并執行指令的核心部件。

ARM存儲器之:存儲保護單元MPU

存儲保護單元MPU

一些嵌入式系統使用多任務的操作和控制。這些系統必須提供一種機制來保證正在運行的任務不破壞其他任務的操作。即要防止系統資源和其他一些任務不受非法訪問。要達到這一目的通常有軟件保護和硬件保護兩種途徑。這里軟件保護是指僅靠軟件來保護系統資源。系統中無保護硬件或硬件沒啟動。在多任務的系統中,通常要運行操作系統來達到任務間同步與通信。所以,這種軟件的資源保護通常由操作系統來完成。但這種通過軟件來協調任務運行,保護系統資源的做法有時會出現一些不可避免的問題。如當對一個通信用串口寄存器進行操作時,如果一個任務正在使用串口,則它沒有辦法來防止其他任務使用同一個串口。因此,若要成功使用該串口,則必須通過一個訪問該串口的系統調用來協調。使用這些調用任務的非授權訪問,很容易破壞經過該串口的通信。因此資源的不合理使用也許是不可避免的。

相反,受保護系統有專門的硬件來檢測和限制系統資源的訪問。它能保證資源的所有權,任務需要遵守一組由操作環境定義的、由硬件維護的規則,在硬件級上授予監視和控制資源程序的特殊權限。受保護系統主動防止一個任務使用其他任務的資源。因此使用硬件主動監視系統比協調加強的軟件歷程,提供了更好的保護。

ARM中配備的有效保護系統資源的硬件,有兩種:

· MPU(Memory Protection Unit);

· MMU(Memory Management Unit)。

MMU是比MPU提供了功能更強大的內存保護機制,MPU只提供了內存區域保護,而MMU是在此基礎上提供了虛擬地址映射技術,而且在操作上,MMU要比MPU負責。本節主要討論帶MPU的處理器內核,MMU將在下一節詳細介紹。

15.4.1 保護域(Protection Regions)

ARM處理器中的MPU使用“域(regions)”來對內存單元進行管理。域是與存儲空間相關聯的屬性,處理器核將這些數據保存在協處理器CP15的一些寄存器中。通常域的個數為8個,編號為從0~7。

域的大小和起始地址保存在CP15的寄存器c6中。大小可以是4KB~4GB的任何2的乘冪。域的起始地址必須是其大小的倍數。比如,一個定義為4KB的域其起始地址可以是0x12345000,而一個大小定義為8KB的域起始地址只能是0x2000的倍數。

另外,操作系統可以為這些域分配更多的屬性:訪問權限、cache和寫緩存。存儲器基于當時的處理器模式(管理模式或用戶模式)可以設定這些區域的訪問權限為讀/寫、只讀和不可訪問。

當處理器訪問主存的一個域時,MPU比較該域的訪問權限屬性和當時的處理器模式。如果請求符合域的訪問標準,則MPU允許內核讀/寫主存;如果存儲器請求不符號域的訪問標準,將產生一個異常信號。

異常信號被送到處理器核。處理器核執行一個異常向量,然后跳轉到異常處理程序,異常處理程序判斷異常類型為預取指或數據中止,然后根據異常類型,跳轉到相應的服務例程。

對于ARM處理器,存儲空間的某一部分可以被分配給一個以上的區域。也就是說域可以重疊。在重疊的域內,可以設置域的優先級。在分配訪問權限時重疊域比非重疊域有更大的靈活性。后面一節將會詳細介紹域的重疊。

內存訪問順序

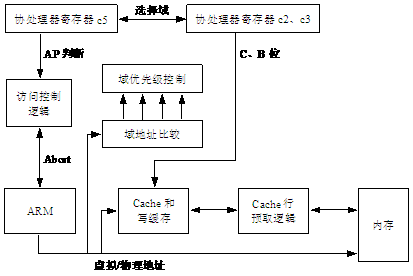

當ARM處理器產生一個內存訪問信號時,內存保護單位MPU將負責檢查要訪問的地址是否在被定義的域中。

① 如果地址不在任何域中,存儲器產生異常。如果內核預取指令則MPU產生預取中止異常;如果是存儲器數據請求,則產生數據中止異常。

② 如果地址在多個域內,由MPU判斷域的有效級來決定存儲區域的訪問屬性。訪問屬性可以在CP15的寄存器中設定,可設定的位為C(Cache)、B(Buffer)、AP(Access Permission)。這些屬性的具體定義為:

· C和B可以控制Cache和寫緩存屬性的Cache策略。例如,可以設置一個域使用回寫(write-back)策略訪問存儲器,而另一個域則以無Cache和無寫緩存方式訪問;

· AP(access permission)決定域是否可以被訪問。如果在當前處理器模式下,該域不能被訪問,MPU將產生一個存儲器訪問異常。

圖15.16顯示了一個存儲器訪問過程。

圖15.16 存儲器訪問過程

15.4.3 使能MPU

通過對協處理器CP15的寄存器c1中的bit[0]置1,可以使能存儲器保護單元MPU。在系統上電時,默認狀態是該位清零,所有保護域無效。

在使能MPU之前,至少一個域要被設定,而且該域的屬性和訪問權限要預先設定好。

![]() 注意在數據和指令域分離的系統中,如ARM940T,在指令和數據域中都要有一個有效域被預先設定好。

注意在數據和指令域分離的系統中,如ARM940T,在指令和數據域中都要有一個有效域被預先設定好。

另外,使能MPU的指令要設在有效的域中。如果在使能MPU之前,域的屬性和訪問權限沒有設定,那么系統的運行結果將不可預知。

當MPU無效(將協處理器CP15寄存器r1的bit[0]置0)時,整個內存區域都被處理器視為無Cache、無寫緩存、無存儲保護狀態。

15.4.4 重疊域

域的定義在MPU的作用下可以重疊。當重疊的域被訪問時,MPU會判斷域的優先權,決定使用那個域的屬性來操作重疊域。

域屬性優先級的排列順序為:域7的有效級最高,其次為域6,域0的優先級最低。

【例15.3】

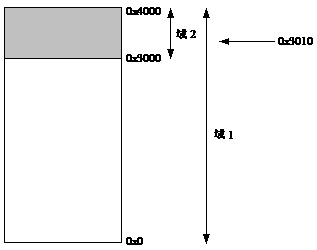

假設將一個從0x3000起始的4KB地址空間定義為域2,其訪問屬性AP定義為0b10(AP=0b10,特權模式讀/寫訪問,用戶模式只讀)。

將起始地址為0x0的16KB地址空間定義為域1,其訪問屬性AP定義為0b01(AP=0b01,特權模式只讀)。

系統域劃分如圖15.17所示。

圖15.17 重疊域的訪問

當處理器在用戶模式下執行Load指令,從0x3010地址取數據時,0x3010地址既在域1中也在域2中,因為域2的屬性優先級高于域1,所有MPU執行域2的訪問屬性從0x3010地址取數據。域2是用戶模式可讀,所以不會發生數據異常。

在分配訪問權限時重疊區域比非重疊區域有更大的靈活性,它可以使內存的某個特定聯系內存單位在程序中擔任背景的作用,用來給一塊大存儲空間分配相同的屬性的低優先級域。其他具有較高優先級域的區域與該背景域某些部分重疊,用來改變已定義的背景域的較小子集的屬性。這樣,具有較高優先級的域可以改變背景域屬性的子集。背景域可以用來保護一些睡眠狀態的存儲空間,使其不受非法訪問,而此時由另一個不同域控制下的背景域的其他部分可以處于活躍狀態。

15.4.5 與MPU相關的CP15寄存器

與MPU相關的協處理器寄存器主要是c2,c3,c5及c6。另外還有寄存器c1中的1到2位。

(1)c1中的MPU相關位

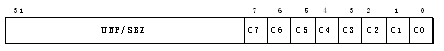

c1的編碼格式如圖15.18所示。

![]()

圖15.18 協處理器寄存器c1編碼格式

M(bit[0])控制控制MPU的使能。

· M=0:禁止MPU

· M=1:使能MPU

A(bit[1])選擇是否支持內存訪問地址對齊檢查。

· B=0:禁止地址對齊檢查

· B=1:使能地址對齊檢查

(2)c2中的MPU相關位

c2的編碼格式如圖15.19所示。

圖15.19 協處理器寄存器c2編碼格式

寄存器位0~7分別對應域0~7的Cache屬性。位8~31應該設置成0。

![]() 注意在數據和指令分離的系統中,通過MRC和MCR指令的第二個操作數《opcode2》來決定讀寫D-Cache和I-Cache屬性。

注意在數據和指令分離的系統中,通過MRC和MCR指令的第二個操作數《opcode2》來決定讀寫D-Cache和I-Cache屬性。

(3)c3中的MPU相關位

c3的編碼格式如圖15.20所示。

圖15.20 協處理器寄存器c3編碼格式

寄存器位0~7分別對應域0~7的寫緩存屬性。位8~31應該設置成0。

當用指令MCR/MRC對c3進行讀寫時,第二個操作數《opcode2》將被忽略,在指令要設置成0。

當配置數據域時,域的Cache位和寫緩存區位一起決定域的訪問策略。寫緩存位有兩個用途:使能/禁止域的寫緩存和設置域的Cache寫策略。域的Cache位控制寫緩存位的作用。具體位分配見表15.16。

表15.16 Cache位和寫緩存位的分配策略

Cache位寫緩存區位域 屬 性

C=0B=0禁止Cache、禁止寫緩存

C=0B=1禁止Cache、使能寫緩存

C=1B=0使能Cache,域使用回寫策略

C=10B=1使能Cache,域使用直寫策略

(4)訪問權限寄存器c5

協處理器CP15的寄存器c5設置內存域的訪問權限。

寄存器c5的編碼格式如圖15.21所示。

![]()

圖15.21 寄存器c5的編碼格式

讀寄存器c3的bits[15:0]存放域的AP(access permission,訪問權限),其中bits[2n+1:2n]對于域n的訪問權限。AP編碼與訪問權限的對應關系如表15.17所示。

表15.17 AP編碼與訪問權限的對應關系

AP編碼管 理 者用 戶

00不可訪問不可訪問

01讀/寫不可訪問

10讀/寫只讀

11讀/寫讀/寫

對于Arm940T、Arm940T兩個內核版本來說,使用MRC和MCR指令對其進行讀寫時,第二個協處理器寄存器《CRm》將被忽略,指令中以c0的形式出現。對于指令數據統一的域,第二操作數《opcode2》要設成0,而對于數據和指令分離的系統,如果opcode2=0,說明操作對數據域有效,如果opcode=1,說明操作對指令域有效。

![]() 注意對于Arm946E-S和Arm1026EJ-S兩個內核版本,它們的訪問權限機制更復雜,采用的是擴展AP,擴展組AP位域編碼支持兩個增強的權限域,對其進行操作的MRC和MCR指令形式更復雜,有關更詳細的內容,請參加Arm公司的用戶手冊。

注意對于Arm946E-S和Arm1026EJ-S兩個內核版本,它們的訪問權限機制更復雜,采用的是擴展AP,擴展組AP位域編碼支持兩個增強的權限域,對其進行操作的MRC和MCR指令形式更復雜,有關更詳細的內容,請參加Arm公司的用戶手冊。

(5)域大小控制寄存器c6

Arm系統中通過寫協處理器c6來定義域的大小,通過MCR指令中第二個操作寄存器賦不同的值來指示是對哪個具體域進行操作。第二個操作寄存器取值為c0~c7,分別對應域0~域7。

每個域的起始地址必須對齊到其大小的整數倍。比如,一個域的大小位64KB,其起始地址可以是0x10000的整數倍的任何數。域的大小可以是4KB~4GB的2的任意乘冪。

寄存器c6的編碼格式如圖15.22所示。

圖15.22 域大小控制寄存器c6編碼格式

編碼含義如表15.18所示

表15.18 寄存器c6編碼含義

位 名 稱對 應 位注 釋

起始地址[31:12]保護域的第一個字節起始地址,具體見表2.18

SBZ[11:6]必須設為0

Size[5:1]設Size=N,則域尺寸為2N+1,其中11≤N≤31

E[0]域使能,E=1使能,E=0禁止

關于c6中bits[31:12],因為域的起始要是域大小的整倍數,域最小為4KB,所有域起始地址的bits[11:0]通常為0,不用設置。具體c6中起始地址的設置和c6中Size(bits[5:1])的對應關系如表15.19所示。

表15.19 域尺寸編碼

Size(bits[5:1])域 尺 寸起始地址(bits[31:12])

0b00000~0b01010未定義-

0b010114KB無

0b011008KBbit[12]必須為0

0b0110116KBbits[13:12]必須為0

0b0111032KBbits[14:12]必須為0

0b0111164KBbits[15:12]必須為0

0b10000126KBbits[16:12]必須為0

0b10001256KBbits[17:12]必須為0

0b10010512KBbits[18:12]必須為0

0b100111MBbits[19:12]必須為0

0b101002MBbits[20:12]必須為0

0b101014MBbits[21:12]必須為0

0b101108MBbits[22:12]必須為0

0b1011116MBbits[23:12]必須為0

0b1100032MBbits[24:12]必須為0

0b1100164MBbits[25:12]必須為0

0b11010128MBbits[26:12]必須為0

0b11011256MBbits[27:12]必須為0

0b11100512MBbits[28:12]必須為0

0b111011GBbits[29:12]必須為0

續表

Size(bits[5:1])域 尺 寸起始地址(bits[31:12])

0b111102GBbits[30:12]必須為0

0b111114GBbits[31:12]必須為0

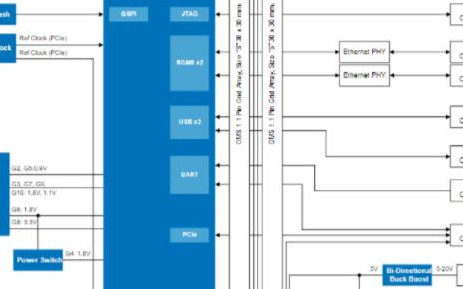

瑞薩電子基于Arm Cortex-A55和雙Cortex-M33 MPU的SOM方案 加速物聯網設計

隨著工業物聯網技術的不斷發展,數以億計的嵌入式設備實現了無縫互聯。在這宏大圖景中,網關作為連接設備與網絡的核心樞紐,重要性不言而喻。為滿足市場對高性能、...

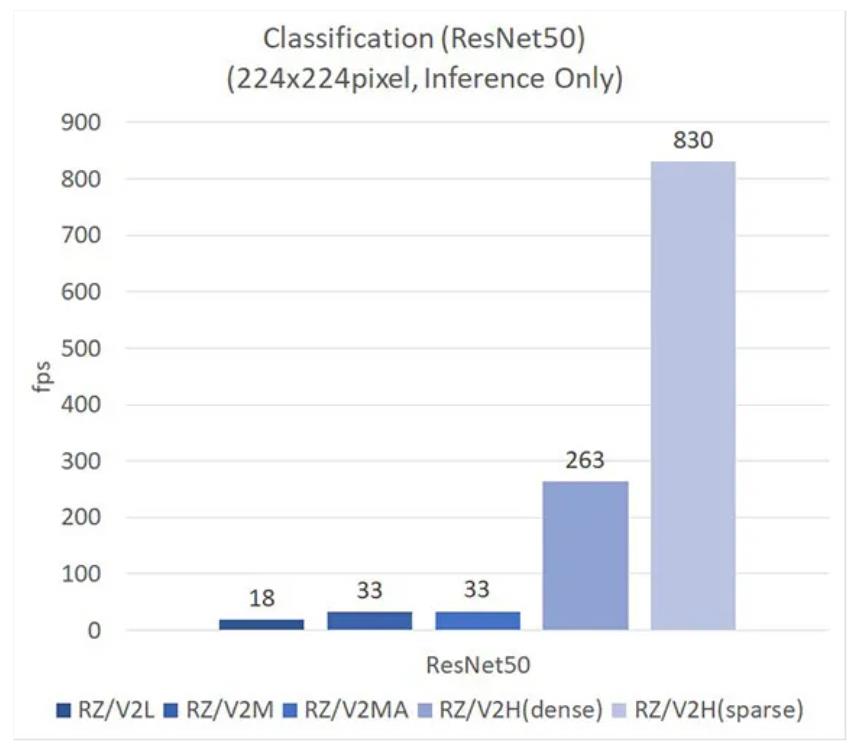

瑞薩電子RZ/V2H MPU提升機器人與自主應用中的AI性能和實時控制

除了這個AI加速器之外,高端RZ/V2H微處理器(MPU)——還配備了使用動態可配置處理器(DRP)的圖像處理加速器、運行頻率高達1.8 GHz的四核L...

類別:IC datasheet pdf 2023-11-30 標簽:MPU

類別:單片機 2023-10-09 標簽:微控制器MPUSTM32MP157

隨著全球工業自動化和智能制造的快速發展,微處理器(MPU)的核心作用日益突出,不僅作為智能控制系統的大腦,更在性能提升、能效優化、安全性增強和智能化等方...

RT-Thread 率先支持RZ/T2M高性能、多功能 MPU!

RZ/T2M是瑞薩電子發布的一款行業領先的高性能、多功能的MPU,具有最大頻率為800MHz的雙ArmCortex-R52內核。可實現AC伺服系統和工業...

MPU進入64位時代,Microchip推出PIC64系列產品

電子發燒友網報道(文/梁浩斌)隨著市場需求的持續提高,包括更多邊緣AI等應用的落地,嵌入式系統對于處理能力的要求日益提高。因此,我們看到過去MCU的發展...

專為工業4.0應用設計,STM32MP25x MPU到底有何不同?

電子發燒友網報道(文/吳子鵬)面對日益復雜和數據量龐大的應用場景,尤其是在高級邊緣計算場景里,MCU在計算能力上已經面臨瓶頸,具備更高計算能力和集成性的...

換一批

換一批

編輯推薦廠商產品技術軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯網 | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發電 | UPS | AR | 智能電網 | 國民技術 | Microchip |

| 開關電源 | 步進電機 | 無線充電 | LabVIEW | EMC | PLC | OLED | 單片機 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 藍牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太網 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 語音識別 | 萬用表 | CPLD | 耦合 | 電路仿真 | 電容濾波 | 保護電路 | 看門狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 閾值電壓 | UART | 機器學習 | TensorFlow |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |