完善資料讓更多小伙伴認(rèn)識你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > cadence

鏗騰電子科技有限公司(Cadence Design Systems, Inc; NASDAQ:CDNS)是一個專門從事電子設(shè)計(jì)自動化(EDA)的軟件公司,由SDA Systems和ECAD兩家公司于1988年兼并而成。是全球最大的電子設(shè)計(jì)技術(shù)(Electronic Design Technologies)、程序方案服務(wù)和設(shè)計(jì)服務(wù)供應(yīng)商。其解決方案旨在提升和監(jiān)控半導(dǎo)體、計(jì)算機(jī)系統(tǒng)、網(wǎng)絡(luò)工程和電信設(shè)備、消費(fèi)電子產(chǎn)品以及其它各類型電子產(chǎn)品的設(shè)計(jì)。

文章:575個 瀏覽:141862次 帖子:515個

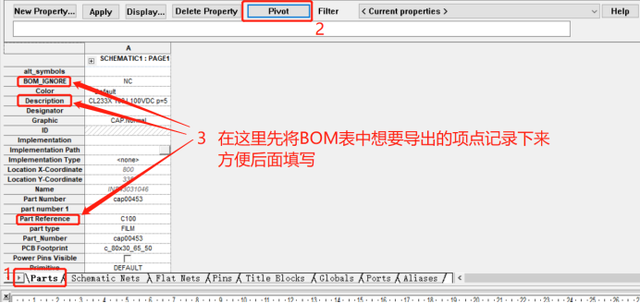

首先打開需要的Cadence 原理圖文件,在原理圖中任意選擇一個器件雙擊,在彈出的對話框中,將BOM表中想要導(dǎo)出的項(xiàng)點(diǎn)提前記錄下來(一般導(dǎo)出的BOM表中...

用Celsius熱求解器對3D-IC進(jìn)行熱分析和應(yīng)力分析

隨著電子產(chǎn)品尺寸的進(jìn)一步縮小和運(yùn)行速度的提高,熱管理環(huán)境的相關(guān)問題也愈發(fā)嚴(yán)峻且影響范圍很廣,芯片、電路板、封裝和整個系統(tǒng)都會受其制約。

Altium Designer原理圖PCB轉(zhuǎn)換到cadence的方法(二)

今天和繼續(xù)大家分享一個詳細(xì)的AD(altium designer21)軟件的原理圖和PCB轉(zhuǎn)化為cadence 17.4【orcad和allegro】的...

Altium Designer原理圖PCB轉(zhuǎn)換到cadence的方法(一)

今天和大家分享一個詳細(xì)的AD(altium designer21)軟件的原理圖和PCB轉(zhuǎn)化為cadence 17.4【orcad和allegro】的圖文...

Cadence Allegro通過Excel表格創(chuàng)建元器件需要幾個步驟?

在我們遇到引腳數(shù)量特別多的芯片時(shí),此前用的創(chuàng)建元件的方法會顯得特別的麻煩,且費(fèi)時(shí)費(fèi)力,也會容易出現(xiàn)錯誤。本文分享給大家6個步驟通過Capture導(dǎo)入Ex...

分享一個關(guān)于cadence【orcad】17.4繪制原理圖時(shí)的小技巧

但是如果只想看SD卡部分原理圖,那就需要放大,但是放大時(shí),用滾輪縮放,滾動一下,顯示區(qū)域過大

3D-IC設(shè)計(jì)之系統(tǒng)級版圖原理圖一致性檢查

隨著芯片工藝尺寸的縮小趨于飽和或停滯,設(shè)計(jì)師們現(xiàn)在專注于通過 3D-IC 異構(gòu)封裝,在芯片所在平面之外的三維空間中構(gòu)建系統(tǒng)。3D-IC 異構(gòu)封裝結(jié)構(gòu)可能...

Cadence Allegro Xnet的創(chuàng)建詳細(xì)教程

Xnet是指在無源器件的兩端,兩個不同的網(wǎng)絡(luò),但是本質(zhì)上其實(shí)是同一個網(wǎng)絡(luò)的這種情況。比如一個源端串聯(lián)電阻或者串容兩端的網(wǎng)絡(luò)。在實(shí)際設(shè)計(jì)情況中,我們需要對...

Cadence Allegro通過Excel表格創(chuàng)建元器件

在我們遇到引腳數(shù)量特別多的芯片時(shí),此前用的創(chuàng)建元件的方法會顯得特別的麻煩,且費(fèi)時(shí)費(fèi)力,也會容易出現(xiàn)錯誤,這時(shí)我們可以通過Capture導(dǎo)入Excel表格...

Cadence Allegro如何設(shè)置網(wǎng)格鋪銅

執(zhí)行菜單欄命令Shape--Global Dynamic Parameters命令,如下圖1所示。

隨著先進(jìn)工藝已經(jīng)進(jìn)入到3nm階段,EDA工具對Delay計(jì)算的準(zhǔn)確度變得十分具有挑戰(zhàn)性

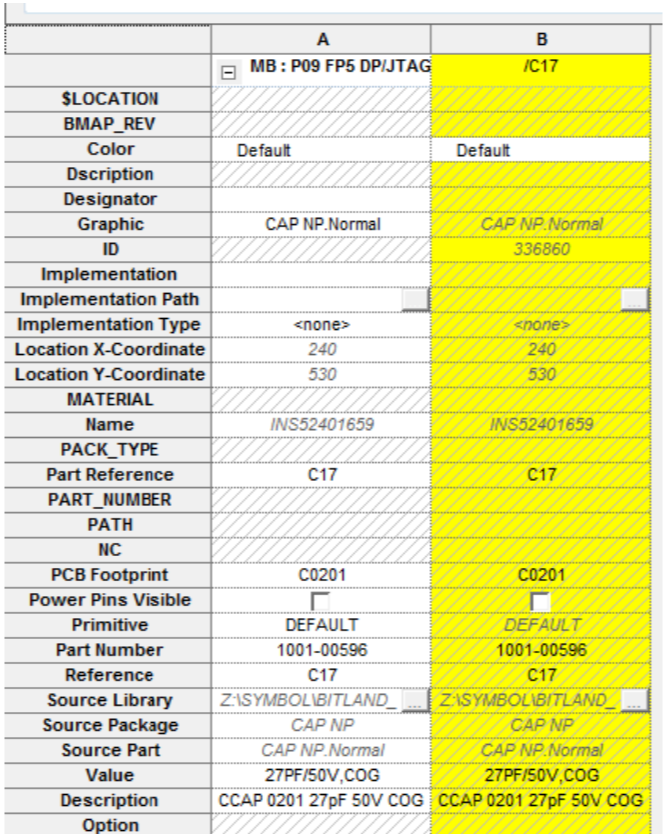

OrCAD Capture CIS instance和occurrences概念解析

Capture CIS 中兩個重要概念:instance 和 occurrences 用 OrCAD 設(shè)計(jì)原理圖必須理解兩個概念 instance 和 ...

先進(jìn)工藝制程使得設(shè)計(jì)工程師們一次又一次突破了芯片性能、功耗和面積的極限。為了可以繼續(xù)速度更快、功能更強(qiáng)、造價(jià)更省的追求,摩爾人依然在孜孜不倦地尋找新的方...

啟動之前安裝的License Manager管理器,如圖2-17所示,只有添加Cadence官方授權(quán)的License文件之后功能才會被激活使用,點(diǎn)擊Br...

對于大規(guī)模的芯片設(shè)計(jì),自上而下是三維集成電路的一種常見設(shè)計(jì)流程。在三維布局中,可以將原始二維布局中相距較遠(yuǎn)的模塊放到上下兩層芯片中,從而在垂直方向相連,...

2022-08-03 標(biāo)簽:集成電路Cadence芯片設(shè)計(jì) 1434 0

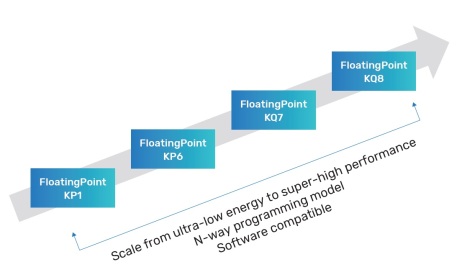

使用新型Cadence Tensilica DSP FPU實(shí)現(xiàn)最佳PPA

音頻和視頻處理、雷達(dá)、電信、驅(qū)動電機(jī)控制、虛擬現(xiàn)實(shí) (VR)、增強(qiáng)現(xiàn)實(shí) (AR) 以及最近的人工智能 (AI) 算法等應(yīng)用都強(qiáng)烈依賴于 DPS(數(shù)字信號...

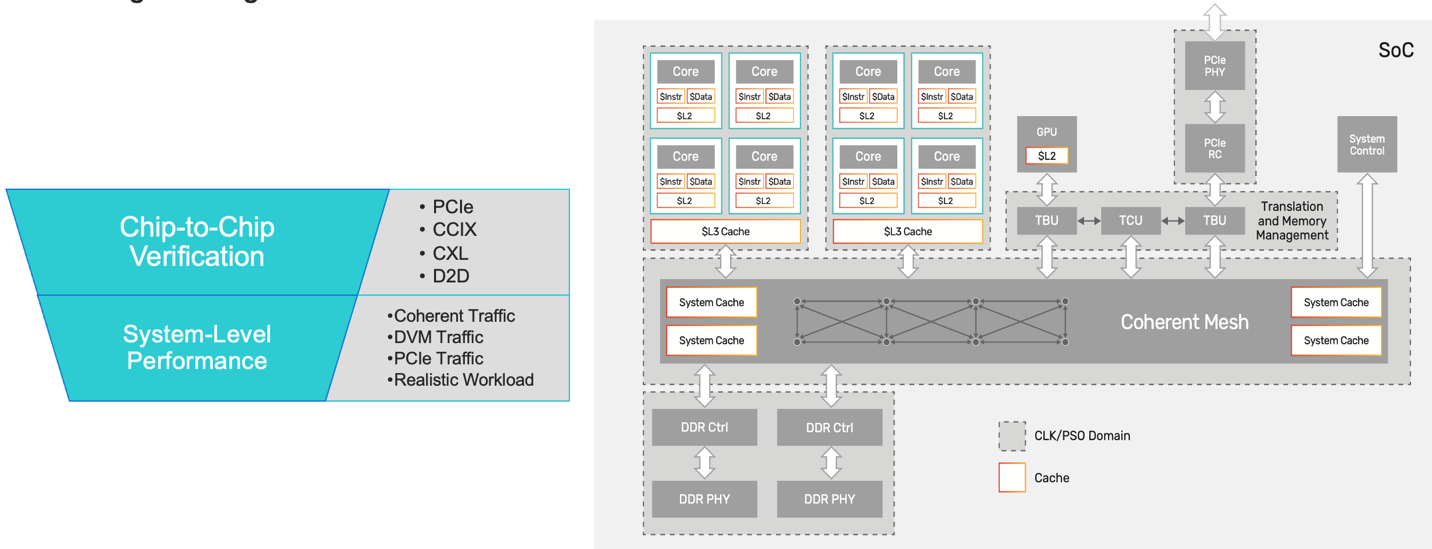

通過仿真加速基于服務(wù)器的系統(tǒng)架構(gòu)合規(guī)性測試

系統(tǒng)級驗(yàn)證目標(biāo)提出了一個問題,即驗(yàn)證可能只有在設(shè)計(jì)和驅(qū)動程序大部分完全組裝和調(diào)試后才可能進(jìn)行,但在檢查符合性之前等待設(shè)計(jì)完成也沒有什么幫助。 Paul ...

Cadence分析 3D IC設(shè)計(jì)如何實(shí)現(xiàn)高效的系統(tǒng)級規(guī)劃

Cadence Integrity 3D-IC 平臺是業(yè)界首個全面的整體 3D-IC 設(shè)計(jì)規(guī)劃、實(shí)現(xiàn)和分析平臺,以全系統(tǒng)的視角,對芯片的性能、功耗和面積...

2022-05-23 標(biāo)簽:集成電路IC設(shè)計(jì)封裝 4931 0

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |