完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

標簽 > DSP技術

數字信號處理(Digital Signal Processing,簡稱DSP)是一門涉及許多學科而又廣泛應用于許多領域的新興學科。20世紀60年代以來,隨著計算機和信息技術的飛速發展,數字信號處理技術應運而生并得到迅速的發展。

數字信號處理(Digital Signal Processing,簡稱DSP)是一門涉及許多學科而又廣泛應用于許多領域的新興學科。20世紀60年代以來,隨著計算機和信息技術的飛速發展,數字信號處理技術應運而生并得到迅速的發展。在過去的二十多年時間里,數字信號處理已經在通信等領域得到極為廣泛DSP技術圖解的應用。數字信號處理是利用計算機或專用處理設備,以數字形式對信號進行采集、變換、濾波、估值、增強、壓縮、識別等處理,以得到符合人們需要的信號形式。

數字信號處理是將信號以數字方式表示并處理的理論和技術。數字信號處理與模擬信號處理是信號處理的子集。

數字信號處理(Digital Signal Processing,簡稱DSP)是一門涉及許多學科而又廣泛應用于許多領域的新興學科。20世紀60年代以來,隨著計算機和信息技術的飛速發展,數字信號處理技術應運而生并得到迅速的發展。在過去的二十多年時間里,數字信號處理已經在通信等領域得到極為廣泛DSP技術圖解的應用。數字信號處理是利用計算機或專用處理設備,以數字形式對信號進行采集、變換、濾波、估值、增強、壓縮、識別等處理,以得到符合人們需要的信號形式。

數字信號處理是將信號以數字方式表示并處理的理論和技術。數字信號處理與模擬信號處理是信號處理的子集。

數字信號處理的目的是對真實世界的連續模擬信號進行測量或濾波。因此在進行數字信號處理之前需要將信號從模擬域轉換到數字域,這通常通過模數轉換器實現。而數字信號處理的輸出經常也要變換到模擬域,這是通過數模轉換器實現的。

數字信號處理的算法需要利用計算機或專用處理設備如數字信號處理器(DSP)和專用集成電路(ASIC)等。數字信號處理技術及設備具有靈活、精確、抗干擾強、設備尺寸小、造價低、速度快等突出優點,這些都是模擬信號處理技術與設備所無法比擬的。

實現方法

DSP的實現方法一般有以下幾種:

(1) 在通用的計算機(如PC機)上用軟件(如Fortran、C語言)實現;

(2) 在通用計算機系統中加上專用的加速處理機實現;

(3) 用通用的單片機(如MCS-51、96系列等)實現,這種方法可用于一些不太復雜的數字信號處理,如數字控制等;

(4) 用通用的可編程DSP實現。與單片機相比,DSP芯片具有更加適合于數字信號處理的軟件和硬件資源,可用于 復雜的數字信號處理算法;

(5) 用專用的DSP芯片實現。在一些特殊的場合,要求的信號處理速度極高,用通用DSP芯片很難實現,例如專用于FFT、數字濾波、卷積、相關等算法的DSP芯片,這種芯片將相應的信號處理算法在芯片內部用硬件實現,無需進行編程。

在上述幾種方法中,第1種方法的缺點是速度較慢,一般可用于DSP算法的模擬;第2種和第5種方法專用性強,應用受到很大的限制,第2種方法也不便于系統的獨立運行;第3種方法只適用于實現簡單的DSP算法;只有第4種方法才使數字信號處理的應用打開了新的局面。

特點

考慮一個數字信號處理的實例,比如有限沖擊響應濾波器(FIR)。用數學語言來說,FIR濾波器是做一系列的點積。取一個輸入量和一個序數向量,在系數和輸入樣本的滑動窗口間作乘法,然后將所有的乘積加起來,形成一個輸出樣本。類似的運算在數字信號處理過程中大量地重復發生,使得為此設計的器件必須提供專門的支持,促成了了DSP器件與通用處理器(GPP)的分流:

對密集的乘法運算的支持

GPP不是設計來做密集乘法任務的,即使是一些現代的GPP,也要求多個指令周期來做一次乘法。而DSP處理器使用專門的硬件來實現單周期乘法。DSP處理器還增加了累加器寄存器來處理多個乘積的和。累加器寄存器通常比其他寄存器寬,增加稱為結果bits的額外bits來避免溢出。同時,為了充分體現專門的乘法-累加硬件的好處,幾乎所有的DSP的指令集都包含有顯式的MAC指令。

存儲器結構

傳統上,GPP使用馮。諾依曼存儲器結構。這種結構中,只有一個存儲器空間通過一組總線(一個地址總線和一個數據總線)連接到處理器核。通常,做一次乘法會發生4次存儲器訪問,用掉至少四個指令周期。大多數DSP采用了哈佛結構,將存儲器空間劃分成兩個,分別存儲程序和數據。它們有兩組總線連接到處理器核,允許同時對它們進行訪問。這種安排將處理器存貯器的帶寬加倍,更重要的是同時為處理器核提供數據與指令。在這種布局下,DSP得以實現單周期的MAC指令。還有一個問題,即現在典型的高性能GPP實際上已包含兩個片內高速緩存,一個是數據,一個是指令,它們直接連接到處理器核,以加快運行時的訪問速度。從物理上說,這種片內的雙存儲器和總線的結構幾乎與哈佛結構的一樣了。然而從邏輯上說,兩者還是有重要的區別。GPP使用控制邏輯來決定哪些數據和指令字存儲在片內的高速緩存里,其程序員并不加以指定(也可能根本不知道)。與此相反,DSP使用多個片內存儲器和多組總線來保證每個指令周期內存儲器的多次訪問。在使用DSP時,程序員要明確地控制哪些數據和指令要存儲在片內存儲器中。程序員在寫程序時,必須保證處理器能夠有效地使用其雙總線。此外,DSP處理器幾乎都不具備數據高速緩存。這是因為DSP的典型數據是數據流。也就是說,DSP處理器對每個數據樣本做計算后,就丟棄了,幾乎不再重復使用。

零開銷循環

如果了解到DSP算法的一個共同的特點,即大多數的處理時間是花在執行較小的循環上,也就容易理解,為什么大多數的DSP都有專門的硬件,用于零開銷循環。所謂零開銷循環是指處理器在執行循環時,不用花時間去檢查循環計數器的值、條件轉移到循環的頂部、將循環計數器減1。與此相反,GPP的循環使用軟件來實現。某些高性能的GPP使用轉移預報硬件,幾乎達到與硬件支持的零開銷循環同樣的效果。

定點計算

大多數DSP使用定點計算,而不是使用浮點。雖然DSP的應用必須十分注意數字的精確,用浮點來做應該容易的多,但是對DSP來說,廉價也是非常重要的。定點機器比起相應的浮點機器來要便宜(而且更快)。為了不使用浮點機器而又保證數字的準確,DSP處理器在指令集和硬件方面都支持飽和計算、舍入和移位。

專門的尋址方式

DSP處理器往往都支持專門的尋址模式,它們對通常的信號處理操作和算法是很有用的。例如,模塊(循環)尋址(對實現數字濾波器延時線很有用)、位倒序尋址(對FFT很有用)。這些非常專門的尋址模式在GPP中是不常使用的,只有用軟件來實現。

執行時間的預測

大多數的DSP應用(如蜂窩電話和調制解調器)都是嚴格的實時應用,所有的處理必須在指定的時間內完成。這就要求程序員準確地確定每個樣本需要多少處理時間,或者,至少要知道,在最壞的情況下,需要多少時間。如果打算用低成本的GPP去完成實時信號處理的任務,執行時間的預測大概不會成為什么問題,應為低成本GPP具有相對直接的結構,比較容易預測執行時間。然而,大多數實時DSP應用所要求的處理能力是低成本GPP所不能提供的。這時候,DSP對高性能GPP的優勢在于,即便是使用了高速緩存的DSP,哪些指令會放進去也是由程序員(而不是處理器)來決定的,因此很容易判斷指令是從高速緩存還是從存儲器中讀取。DSP一般不使用動態特性,如轉移預測和推理執行等。因此,由一段給定的代碼來預測所要求的執行時間是完全直截了當的。從而使程序員得以確定芯片的性能限制。

定點DSP指令集

定點DSP指令集是按兩個目標來設計的:·使處理器能夠在每個指令周期內完成多個操作,從而提高每個指令周期的計算效率。·將存貯DSP程序的存儲器空間減到最小(由于存儲器對整個系統的成本影響甚大,該問題在對成本敏感的DSP應用中尤為重要)。為了實現這些目標,DSP處理器的指令集通常都允許程序員在一個指令內說明若干個并行的操作。例如,在一條指令包含了MAC操作,即同時的一個或兩個數據移動。在典型的例子里,一條指令就包含了計算FIR濾波器的一節所需要的所有操作。這種高效率付出的代價是,其指令集既不直觀,也不容易使用(與GPP的指令集相比)。GPP的程序通常并不在意處理器的指令集是否容易使用,因為他們一般使用象C或C++等高級語言。而對于DSP的程序員來說,不幸的是主要的DSP應用程序都是用匯編語言寫的(至少部分是匯編語言優化的)。這里有兩個理由:首先,大多數廣泛使用的高級語言,例如C,并不適合于描述典型的DSP算法。其次,DSP結構的復雜性,如多存儲器空間、多總線、不規則的指令集、高度專門化的硬件等,使得難于為其編寫高效率的編譯器。即便用編譯器將C源代碼編譯成為DSP的匯編代碼,優化的任務仍然很重。典型的DSP應用都具有大量計算的要求,并有嚴格的開銷限制,使得程序的優化必不可少(至少是對程序的最關鍵部分)。因此,考慮選用DSP的一個關鍵因素是,是否存在足夠的能夠較好地適應DSP處理器指令集的程序員。

開發工具的要求

因為DSP應用要求高度優化的代碼,大多數DSP廠商都提供一些開發工具,以幫助程序員完成其優化工作。例如,大多數廠商都提供處理器的仿真工具,以準確地仿真每個指令周期內處理器的活動。無論對于確保實時操作還是代碼的優化,這些都是很有用的工具。GPP廠商通常并不提供這樣的工具,主要是因為GPP程序員通常并不需要詳細到這一層的信息。GPP缺乏精確到指令周期的仿真工具,是DSP應用開發者所面臨的的大問題:由于幾乎不可能預測高性能GPP對于給定任務所需要的周期數,從而無法說明如何去改善代碼的性能。

應用

現代社會對數據通信需求正向多樣化、個人化方向發展。而無線數據通信作為向社會公眾迅速、準確、安全、靈活、高效地提供數據交流的有力手段,其市場需求也日益迫切。正是在這種情況下,3G、4G通信才會不斷地被推出,但是無論是3G還是4G,未來通信都將離不開DSP技術(數字信號處理器),DSP作為一種功能強大的特種微處理器,主要應用在數據、語音、視像信號的高速數學運算和實時處理方面,可以說DSP將在未來通信領域中起著舉足輕重的作用。

為了確保未來的通信能在各種環境下自由高效地工作,這就要求組成未來通信的DSP要具有非常高的處理信號的運算速度,才能實現各種繁雜的計算、解壓縮和編譯碼。而目前DSP按照功能的側重點不一樣,可以分為定點DSP和浮點DSP,定點DSP以成本低見長,浮點DSP以速度快見長。如果單一地使用一種類型的DSP,未來通信的潛能就不能得到最大程度的發揮。為了能將定點與浮點的優勢集于一身,突破DSP技術上的瓶頸,人們又推出了一種高級多重處理結構--VLIW結構,該結構可以在不提高時鐘速度的情況下,實現很強的數字信號處理能力,而且它能同時具備定點DSP和浮點DSP所有的優點。為了能推出一系列更高檔的新技術平臺,人們又開始注重DSP的內核技術的開發,因為DSP的內核就相當于計算機的CPU一樣,被譽為DSP的心臟,大量的算法和操作都得通過它來完成,因此該內核結構的質量如何,將會直接影響整個DSP芯片的性能、 功耗和成本。

考慮到未來無線訪問Internet因特網和開展多媒體業務的需要,現在美國的Sun公司又開始準備準將該公司的拳頭產品--PersonalJava語言嵌入到DSP中,以便能進一步提高DSP在處理信號方面的自動化程度和智能化程度。當然,在以前DSP中也潛入了其他軟件語言,例如高級C語言,但這種語言在處理網絡資源以及多媒體信息方面無能為力;而PersonalJava是一種適合個人網絡連接和應用的Java環境,基于該環境的個人通信系統可以從網絡和Internet網上下載數據和圖像。此外,人們還在研究開發符合MPEG-4無線解壓縮標準DSP,該壓縮標準將為未來通信傳輸各種多媒體信息提供了依據。

作為一個案例研究,我們來考慮數字領域里最通常的功能:濾波。簡單地說,濾波就是對信號進行處理,以改善其特性。例如,濾波可以從信號里清除噪聲或靜電干擾,從而改善其信噪比。為什么要用微處理器,而不是模擬器件來對信號做濾波呢?我們來看看其優越性:

模擬濾波器(或者更一般地說,模擬電路)的性能要取決于溫度等環境因素。而數字濾波器則基本上不受環境的影響。

數字濾波易于在非常小的寬容度內進行復制,因為其性能并不取決于性能已偏離正常值的器件的組合。

一個模擬濾波器一旦制造出來,其特性(例如通帶頻率范圍)是不容易改變的。使用微處理器來實現數字濾波器,就可以通過對其重新編程來改變濾波的特性。

初學DSP

一、為什么要用DSP?

3G通信技術的發展,要求處理器的速度越來越高,體積越來越小,MCU的速度較慢;CPU體積大、功耗高;嵌入CPU的成本較高。DSP的發展正好能滿足這一發展的要求,使其在許多速度要求較高、算法較復雜的場合取代MCU或其它處理器,而且綜合成本有可能更低。

二、DSP是什么、能干嘛?

想了解這些,就得一個概念講起,DSP首先是Digital Signal Processing(數字信號處理),然后才是Digital Singnal Processor(數字信號處理器)。具體關于DSP的介紹,請參考小弟的《三國殺之FPGA與ASIC、DSP全面大比拼!》,你能找到你想要的知識,也能找到學習DSP的動力。

三、DSP有沒有前途(“錢途”)?

很多人都覺得做技術就是苦逼,哪來的什么前途,一定要轉做技術管理或銷售。以前我也這般認為,但現在越來越多的事實證明,這就是一個謬論,DSP相當有錢途!舉兩個例子:其一,某位DSP的資深AE,可以算是中國區該領域的專家,年薪不菲(60萬以上),走遍世界,工作也很輕松;其二,某知名電信公司晉升年限一樣的技術專家比同級的經理薪酬要高,如Expert(專家級)與管理大概50個人的經理相比,前者的薪酬要更高。

肯定有人說哪這么多高端人士,大家都是正常人類。好吧,那來個正常的數據,京滬深的DSP工程師起薪基本上是10K/月,就是1萬現大洋,滿意了吧。

四、DSP好不好學?

不管你喜不喜歡,學習DSP就必須得面對她:算法。算法是DSP的精華,可以說擺平了算法就搞定了80%,如果你又懂單片機編程,那么恭喜你有成為DSP專家的潛力。肯定有童鞋問算法到底好不好學呢?算法,聽上去是很高深的東西,但其原理也不過就是一些加減乘而已,連除都很少。肯定有童鞋又問,加減乘不就是小學生的算術嘛?是的, DSP 的算法也許就比小學生的算術難一滴滴。聽完這些,你肯定樂呵呵:DSP挺好學的嘛。

五、DSP該怎么學?

這是個大問題,這里涉及到選開發板、看書、做實驗,下面咱們詳細講這幾個問題:

1、如何DSP開發板?

咱們在討論選開發板之前,得先解決要學哪種DSP。科普一下,DSP分為通用型DSP芯片和專用型DSP芯片,通用型DSP芯片適合普通的DSP應用,如TI,ADI等公司的DSP芯片屬于通用型DSP芯片;專用DSP芯片是為特定的DSP運算而設計的,更適合特殊的運算,如數字濾波、卷積和FFT,如如Motorola公司的DSP56200。學習DSP是當然為了找工作掙錢的,那自然是要學TI的通用型DSP,為什么呢,因為TI 占有最大的市場份額(世界市場45%的份額),咱總不能學一個沒有市場的DSP吧。

DSP是一門實踐性很強的專業,要想快速精通,就必須有自己的操作平臺。這樣既可以增強動手能力,也可以節約很多時間。所以,對于初學者來說,選擇一款性價比較高的開發板很重要。下面咱們就選開發板了,TI 公司現在主推四大系列DSP: 1)C2000 系列(定點、控制器):C20X,F20X,F24X,F24XX ,C28x,用于數字化控制領域;2)C5000 系列(定點、低功耗):C54X,C54XX,C55X,用于通信、便攜式應用領域;3)C6000 系列:C62XX,C67XX,C64X,用于寬帶網絡和數字影像領域;4)OMAP 系列:TI專門為支持2.5G和3G手機應用需求而設計的處理器體系結構(DSP+MCU+MTC內存和流量控制器)。雖然有這么多型號的DSP,但作為初學者,我們當然要選擇C2000 系列,而且要選擇F2810/F2812,這是業界最強大的控制專用DSP,還有一個升級版:28335。開發板的主控芯片選取了,至于具體選哪個品牌的開發板,價格從幾百到幾千不等,具體看個人預算。

開發板選擇有這么兩個原則:1)適當的外設。最小系統板雖然便宜但不利于咱們學習(最小系統是給高手DIY的),沒外設搞起來沒有成就感,沒幾天就煩了,所以得有適當的外設;功能堆疊型開發板雖然功能豐富,但是貴,也不適合咱們初學。初學嘛,沒創造什么效益,自然是以節約為主。有基本的外設就行了,最重要的是學習接口,比如SPI、SCI、CAN,不管你以后做什么項目都通過這些接口連接外圍電路。2)例程。光有代碼的例程不是好例程。例程一定要詳細、模塊化。

MediaTek Filogic 130A Wi-Fi 6 AIoT 邊緣運算語音辨識方案

聯發科技 MediaTek 全新無線連網系統單芯片 Filogic 130A ( MT7933 ),整合獨立音訊數位訊號處理器 ( DSP ) ,可便捷...

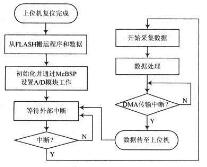

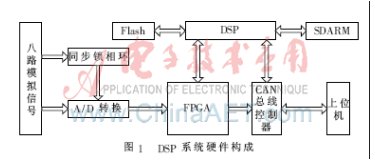

設計了一種基于DSP的風電場電能質量檢測裝置。采用TMS320F28335作為處理器,通過FPGA來完成整個系統的邏輯控制;采用了工業控制中通用的CAN...

2018-12-19 標簽:dspDSP技術TMS320F28335 1234 0

類別:DSP 2016-04-25 標簽:DSP技術算法TMS320C54x

類別:DSP 2016-04-25 標簽:DSP技術算法TMS320C54x

類別:DSP 2016-04-25 標簽:DSP技術算法TMS320C54x

【經典回顧】基于AD9361+ ZYNQ軟件無線電平臺的設計與實現

本文講解基于ADIAD9361模塊AD-FMCOMMS3-EBZ和創龍科技Zynq-7045/7100評估板搭建AD9361RF(RadioFreque...

3. 利用DSP運算功能,克服路經效應。在與相位有關的射頻識別檢測系統中,如一般用雙平衡混頻器解調電路的系統,由路程差產生的相位差會使接收靈敏度產生周期...

石油測井中DSP采集系統詳解 DSP:數字信號處理器是一種智能微處理器能夠搞高效進行各種數字信號處理。 在石油測井中DSP不是一般在常溫環境下的采集系統...

FPGA的并發可以在不同邏輯功能之間進行,而不局限于同時執行相同的功能。流水是通過將任務分段,段與段之間同時執行。

計算類芯片也稱邏輯電路,是一種離散信號的傳遞和處理,以二進制為原理、實現數字信號邏輯運算和操作的電路, 它們在計算機、數字控制、通信、自動化和儀表等方面...

dsp技術在手機方面的應用_vivo X9s Plus的DSP技術有多強

vivo在之前的MWC 2017上海站的時候發布了全新DSP芯片影像優化拍照技術,這也是vivo首次在手機上加入這項技術。

2018-01-03 標簽:dspdsp技術vivox9splus 6662 0

換一批

換一批

編輯推薦廠商產品技術軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯網 | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發電 | UPS | AR | 智能電網 | 國民技術 | Microchip |

| 開關電源 | 步進電機 | 無線充電 | LabVIEW | EMC | PLC | OLED | 單片機 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 藍牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太網 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 語音識別 | 萬用表 | CPLD | 耦合 | 電路仿真 | 電容濾波 | 保護電路 | 看門狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 閾值電壓 | UART | 機器學習 | TensorFlow |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |