完善資料讓更多小伙伴認(rèn)識你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > MPU

MPU有兩種意思,微處理器和內(nèi)存保護(hù)單元。MPU是單一的一顆芯片,而芯片組則由一組芯片所構(gòu)成,早期甚至多達(dá)7、8顆,但目前大多合并成2顆,一般稱作北橋(North Bridge)芯片和南橋(South Bridge)芯片。

MPU有兩種意思,微處理器和內(nèi)存保護(hù)單元。MPU是單一的一顆芯片,而芯片組則由一組芯片所構(gòu)成,早期甚至多達(dá)7、8顆,但目前大多合并成2顆,一般稱作北橋(North Bridge)芯片和南橋(South Bridge)芯片。MPU是計(jì)算機(jī)的計(jì)算、判斷或控制中心,有人稱它為”計(jì)算機(jī)的心臟”。

MPU[1] (Microprocessor Unit)微處理器微機(jī)中的中央處理器(CPU)稱為微處理器(MPU),是構(gòu)成微機(jī)的核心部件,也可以說是微機(jī)的心臟。它起到控制整個(gè)微型計(jì)算機(jī)工作的作用,產(chǎn)生控制信號對相應(yīng)的部件進(jìn)行控制,并執(zhí)行相應(yīng)的操作。在微機(jī)中,CPU被集成在一片超大規(guī)模集成電路芯片上,稱為微處理器(MPU),微處理器插在主板的cpu插槽中。通常所說的16位機(jī)、32位機(jī)是指該計(jì)算機(jī)中微處理器內(nèi)部數(shù)據(jù)總線的寬度,也就是CPU可同時(shí)操作的二進(jìn)制數(shù)的位數(shù)。目前常用的CPU都是64位的,即一次可傳送64位二進(jìn)制數(shù)。

MPU有兩種意思,微處理器和內(nèi)存保護(hù)單元。MPU是單一的一顆芯片,而芯片組則由一組芯片所構(gòu)成,早期甚至多達(dá)7、8顆,但目前大多合并成2顆,一般稱作北橋(North Bridge)芯片和南橋(South Bridge)芯片。MPU是計(jì)算機(jī)的計(jì)算、判斷或控制中心,有人稱它為”計(jì)算機(jī)的心臟”。

MPU[1] (Microprocessor Unit)微處理器微機(jī)中的中央處理器(CPU)稱為微處理器(MPU),是構(gòu)成微機(jī)的核心部件,也可以說是微機(jī)的心臟。它起到控制整個(gè)微型計(jì)算機(jī)工作的作用,產(chǎn)生控制信號對相應(yīng)的部件進(jìn)行控制,并執(zhí)行相應(yīng)的操作。在微機(jī)中,CPU被集成在一片超大規(guī)模集成電路芯片上,稱為微處理器(MPU),微處理器插在主板的cpu插槽中。通常所說的16位機(jī)、32位機(jī)是指該計(jì)算機(jī)中微處理器內(nèi)部數(shù)據(jù)總線的寬度,也就是CPU可同時(shí)操作的二進(jìn)制數(shù)的位數(shù)。目前常用的CPU都是64位的,即一次可傳送64位二進(jìn)制數(shù)。

功能構(gòu)成

微處理器的功能結(jié)構(gòu)主要包括:運(yùn)算器、控制器、寄存器三部分:運(yùn)算器的主要功能就是進(jìn)行算術(shù)運(yùn)算和邏輯運(yùn)算。控制器是整個(gè)微機(jī)系統(tǒng)的指揮中心,其主要作用是控制程序的執(zhí)行。包括對指令進(jìn)行譯碼、寄存,并按指令要求完成所規(guī)定的操作,即指令控制、時(shí)序控制和操作控制。寄存器用來存放操作數(shù)、中間數(shù)據(jù)及結(jié)果數(shù)據(jù)。

主要技術(shù)參數(shù)

CPU質(zhì)量的高低直接決定了一個(gè)計(jì)算機(jī)系統(tǒng)的檔次,而CPU的主要技術(shù)特性可以反映出CPU的基本性能。CPU的主要技術(shù)參數(shù)如下:⑴ CPU可以同時(shí)處理的二進(jìn)制數(shù)據(jù)的位數(shù),即字長;⑵ 時(shí)鐘頻率;⑶ 高速緩沖存儲器(Cache)的容量和速率;⑷ 地址總線和數(shù)據(jù)總線的寬度;⑸ 制造工藝。

內(nèi)存保護(hù)

內(nèi)存保護(hù)單元(ARM體系方面)(MPU,Memory Protection Unit),MPU中一個(gè)域就是一些屬性值及其對應(yīng)的一片內(nèi)存。這些屬性包括:起始地址、長度、讀寫權(quán)限以及緩存等。ARM940具有不同的域來控制指令內(nèi)存和數(shù)據(jù)內(nèi)存。內(nèi)核可以定義8對區(qū)域,分別控制8個(gè)指令和數(shù)據(jù)內(nèi)存區(qū)域。域和域可以重疊并且可以設(shè)置不同的優(yōu)先級。域的啟始地址必須是其大小的整數(shù)倍。另外,域的大小可以4K到4G間任意一個(gè)2的指數(shù),如4K,8K,16K.。。。。英漢計(jì)算機(jī)詞匯= Main Processing Unit,主處理機(jī); = Memory Protection Unit, 存儲器保護(hù)設(shè)備; = MicroProcessing Unit, 微處理器[機(jī)]; = MicroProgrammed control Unit, 微程序控制器; = MicroProgramming Unit, 微程序設(shè)計(jì)部件; = Miniature Power Unit, 小型電源設(shè)備

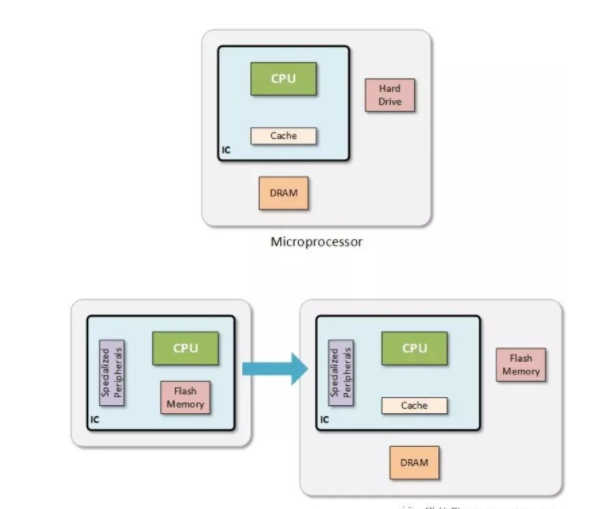

MCU和MPU有什么區(qū)別

MPU有兩種意思,微處理器和內(nèi)存保護(hù)單元。MPU是單一的一顆芯片,而芯片組則由一組芯片所構(gòu)成,早期甚至多達(dá)7、8顆,但目前大多合并成2顆,一般稱作北橋(North Bridge)芯片和南橋(South Bridge)芯片。MPU是計(jì)算機(jī)的計(jì)算、判斷或控制中心,有人稱它為”計(jì)算機(jī)的心臟”。

中央處理器(CPU,英語:Central Processing Unit),是電子計(jì)算機(jī)的主要設(shè)備之一,電腦中的核心配件。其功能主要是解釋計(jì)算機(jī)指令以及處理計(jì)算機(jī)軟件中的數(shù)據(jù)。電腦中所有操作都由CPU負(fù)責(zé)讀取指令,對指令譯碼并執(zhí)行指令的核心部件。

ARM存儲器之:存儲保護(hù)單元MPU

存儲保護(hù)單元MPU

一些嵌入式系統(tǒng)使用多任務(wù)的操作和控制。這些系統(tǒng)必須提供一種機(jī)制來保證正在運(yùn)行的任務(wù)不破壞其他任務(wù)的操作。即要防止系統(tǒng)資源和其他一些任務(wù)不受非法訪問。要達(dá)到這一目的通常有軟件保護(hù)和硬件保護(hù)兩種途徑。這里軟件保護(hù)是指僅靠軟件來保護(hù)系統(tǒng)資源。系統(tǒng)中無保護(hù)硬件或硬件沒啟動。在多任務(wù)的系統(tǒng)中,通常要運(yùn)行操作系統(tǒng)來達(dá)到任務(wù)間同步與通信。所以,這種軟件的資源保護(hù)通常由操作系統(tǒng)來完成。但這種通過軟件來協(xié)調(diào)任務(wù)運(yùn)行,保護(hù)系統(tǒng)資源的做法有時(shí)會出現(xiàn)一些不可避免的問題。如當(dāng)對一個(gè)通信用串口寄存器進(jìn)行操作時(shí),如果一個(gè)任務(wù)正在使用串口,則它沒有辦法來防止其他任務(wù)使用同一個(gè)串口。因此,若要成功使用該串口,則必須通過一個(gè)訪問該串口的系統(tǒng)調(diào)用來協(xié)調(diào)。使用這些調(diào)用任務(wù)的非授權(quán)訪問,很容易破壞經(jīng)過該串口的通信。因此資源的不合理使用也許是不可避免的。

相反,受保護(hù)系統(tǒng)有專門的硬件來檢測和限制系統(tǒng)資源的訪問。它能保證資源的所有權(quán),任務(wù)需要遵守一組由操作環(huán)境定義的、由硬件維護(hù)的規(guī)則,在硬件級上授予監(jiān)視和控制資源程序的特殊權(quán)限。受保護(hù)系統(tǒng)主動防止一個(gè)任務(wù)使用其他任務(wù)的資源。因此使用硬件主動監(jiān)視系統(tǒng)比協(xié)調(diào)加強(qiáng)的軟件歷程,提供了更好的保護(hù)。

ARM中配備的有效保護(hù)系統(tǒng)資源的硬件,有兩種:

· MPU(Memory Protection Unit);

· MMU(Memory Management Unit)。

MMU是比MPU提供了功能更強(qiáng)大的內(nèi)存保護(hù)機(jī)制,MPU只提供了內(nèi)存區(qū)域保護(hù),而MMU是在此基礎(chǔ)上提供了虛擬地址映射技術(shù),而且在操作上,MMU要比MPU負(fù)責(zé)。本節(jié)主要討論帶MPU的處理器內(nèi)核,MMU將在下一節(jié)詳細(xì)介紹。

15.4.1 保護(hù)域(Protection Regions)

ARM處理器中的MPU使用“域(regions)”來對內(nèi)存單元進(jìn)行管理。域是與存儲空間相關(guān)聯(lián)的屬性,處理器核將這些數(shù)據(jù)保存在協(xié)處理器CP15的一些寄存器中。通常域的個(gè)數(shù)為8個(gè),編號為從0~7。

域的大小和起始地址保存在CP15的寄存器c6中。大小可以是4KB~4GB的任何2的乘冪。域的起始地址必須是其大小的倍數(shù)。比如,一個(gè)定義為4KB的域其起始地址可以是0x12345000,而一個(gè)大小定義為8KB的域起始地址只能是0x2000的倍數(shù)。

另外,操作系統(tǒng)可以為這些域分配更多的屬性:訪問權(quán)限、cache和寫緩存。存儲器基于當(dāng)時(shí)的處理器模式(管理模式或用戶模式)可以設(shè)定這些區(qū)域的訪問權(quán)限為讀/寫、只讀和不可訪問。

當(dāng)處理器訪問主存的一個(gè)域時(shí),MPU比較該域的訪問權(quán)限屬性和當(dāng)時(shí)的處理器模式。如果請求符合域的訪問標(biāo)準(zhǔn),則MPU允許內(nèi)核讀/寫主存;如果存儲器請求不符號域的訪問標(biāo)準(zhǔn),將產(chǎn)生一個(gè)異常信號。

異常信號被送到處理器核。處理器核執(zhí)行一個(gè)異常向量,然后跳轉(zhuǎn)到異常處理程序,異常處理程序判斷異常類型為預(yù)取指或數(shù)據(jù)中止,然后根據(jù)異常類型,跳轉(zhuǎn)到相應(yīng)的服務(wù)例程。

對于ARM處理器,存儲空間的某一部分可以被分配給一個(gè)以上的區(qū)域。也就是說域可以重疊。在重疊的域內(nèi),可以設(shè)置域的優(yōu)先級。在分配訪問權(quán)限時(shí)重疊域比非重疊域有更大的靈活性。后面一節(jié)將會詳細(xì)介紹域的重疊。

內(nèi)存訪問順序

當(dāng)ARM處理器產(chǎn)生一個(gè)內(nèi)存訪問信號時(shí),內(nèi)存保護(hù)單位MPU將負(fù)責(zé)檢查要訪問的地址是否在被定義的域中。

① 如果地址不在任何域中,存儲器產(chǎn)生異常。如果內(nèi)核預(yù)取指令則MPU產(chǎn)生預(yù)取中止異常;如果是存儲器數(shù)據(jù)請求,則產(chǎn)生數(shù)據(jù)中止異常。

② 如果地址在多個(gè)域內(nèi),由MPU判斷域的有效級來決定存儲區(qū)域的訪問屬性。訪問屬性可以在CP15的寄存器中設(shè)定,可設(shè)定的位為C(Cache)、B(Buffer)、AP(Access Permission)。這些屬性的具體定義為:

· C和B可以控制Cache和寫緩存屬性的Cache策略。例如,可以設(shè)置一個(gè)域使用回寫(write-back)策略訪問存儲器,而另一個(gè)域則以無Cache和無寫緩存方式訪問;

· AP(access permission)決定域是否可以被訪問。如果在當(dāng)前處理器模式下,該域不能被訪問,MPU將產(chǎn)生一個(gè)存儲器訪問異常。

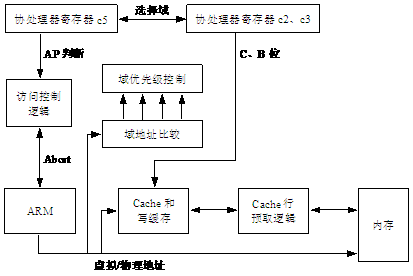

圖15.16顯示了一個(gè)存儲器訪問過程。

圖15.16 存儲器訪問過程

15.4.3 使能MPU

通過對協(xié)處理器CP15的寄存器c1中的bit[0]置1,可以使能存儲器保護(hù)單元MPU。在系統(tǒng)上電時(shí),默認(rèn)狀態(tài)是該位清零,所有保護(hù)域無效。

在使能MPU之前,至少一個(gè)域要被設(shè)定,而且該域的屬性和訪問權(quán)限要預(yù)先設(shè)定好。

![]() 注意在數(shù)據(jù)和指令域分離的系統(tǒng)中,如ARM940T,在指令和數(shù)據(jù)域中都要有一個(gè)有效域被預(yù)先設(shè)定好。

注意在數(shù)據(jù)和指令域分離的系統(tǒng)中,如ARM940T,在指令和數(shù)據(jù)域中都要有一個(gè)有效域被預(yù)先設(shè)定好。

另外,使能MPU的指令要設(shè)在有效的域中。如果在使能MPU之前,域的屬性和訪問權(quán)限沒有設(shè)定,那么系統(tǒng)的運(yùn)行結(jié)果將不可預(yù)知。

當(dāng)MPU無效(將協(xié)處理器CP15寄存器r1的bit[0]置0)時(shí),整個(gè)內(nèi)存區(qū)域都被處理器視為無Cache、無寫緩存、無存儲保護(hù)狀態(tài)。

15.4.4 重疊域

域的定義在MPU的作用下可以重疊。當(dāng)重疊的域被訪問時(shí),MPU會判斷域的優(yōu)先權(quán),決定使用那個(gè)域的屬性來操作重疊域。

域?qū)傩詢?yōu)先級的排列順序?yàn)椋河?的有效級最高,其次為域6,域0的優(yōu)先級最低。

【例15.3】

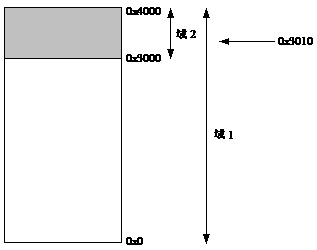

假設(shè)將一個(gè)從0x3000起始的4KB地址空間定義為域2,其訪問屬性AP定義為0b10(AP=0b10,特權(quán)模式讀/寫訪問,用戶模式只讀)。

將起始地址為0x0的16KB地址空間定義為域1,其訪問屬性AP定義為0b01(AP=0b01,特權(quán)模式只讀)。

系統(tǒng)域劃分如圖15.17所示。

圖15.17 重疊域的訪問

當(dāng)處理器在用戶模式下執(zhí)行Load指令,從0x3010地址取數(shù)據(jù)時(shí),0x3010地址既在域1中也在域2中,因?yàn)橛?的屬性優(yōu)先級高于域1,所有MPU執(zhí)行域2的訪問屬性從0x3010地址取數(shù)據(jù)。域2是用戶模式可讀,所以不會發(fā)生數(shù)據(jù)異常。

在分配訪問權(quán)限時(shí)重疊區(qū)域比非重疊區(qū)域有更大的靈活性,它可以使內(nèi)存的某個(gè)特定聯(lián)系內(nèi)存單位在程序中擔(dān)任背景的作用,用來給一塊大存儲空間分配相同的屬性的低優(yōu)先級域。其他具有較高優(yōu)先級域的區(qū)域與該背景域某些部分重疊,用來改變已定義的背景域的較小子集的屬性。這樣,具有較高優(yōu)先級的域可以改變背景域?qū)傩缘淖蛹1尘坝蚩梢杂脕肀Wo(hù)一些睡眠狀態(tài)的存儲空間,使其不受非法訪問,而此時(shí)由另一個(gè)不同域控制下的背景域的其他部分可以處于活躍狀態(tài)。

15.4.5 與MPU相關(guān)的CP15寄存器

與MPU相關(guān)的協(xié)處理器寄存器主要是c2,c3,c5及c6。另外還有寄存器c1中的1到2位。

(1)c1中的MPU相關(guān)位

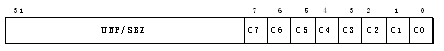

c1的編碼格式如圖15.18所示。

![]()

圖15.18 協(xié)處理器寄存器c1編碼格式

M(bit[0])控制控制MPU的使能。

· M=0:禁止MPU

· M=1:使能MPU

A(bit[1])選擇是否支持內(nèi)存訪問地址對齊檢查。

· B=0:禁止地址對齊檢查

· B=1:使能地址對齊檢查

(2)c2中的MPU相關(guān)位

c2的編碼格式如圖15.19所示。

圖15.19 協(xié)處理器寄存器c2編碼格式

寄存器位0~7分別對應(yīng)域0~7的Cache屬性。位8~31應(yīng)該設(shè)置成0。

![]() 注意在數(shù)據(jù)和指令分離的系統(tǒng)中,通過MRC和MCR指令的第二個(gè)操作數(shù)《opcode2》來決定讀寫D-Cache和I-Cache屬性。

注意在數(shù)據(jù)和指令分離的系統(tǒng)中,通過MRC和MCR指令的第二個(gè)操作數(shù)《opcode2》來決定讀寫D-Cache和I-Cache屬性。

(3)c3中的MPU相關(guān)位

c3的編碼格式如圖15.20所示。

圖15.20 協(xié)處理器寄存器c3編碼格式

寄存器位0~7分別對應(yīng)域0~7的寫緩存屬性。位8~31應(yīng)該設(shè)置成0。

當(dāng)用指令MCR/MRC對c3進(jìn)行讀寫時(shí),第二個(gè)操作數(shù)《opcode2》將被忽略,在指令要設(shè)置成0。

當(dāng)配置數(shù)據(jù)域時(shí),域的Cache位和寫緩存區(qū)位一起決定域的訪問策略。寫緩存位有兩個(gè)用途:使能/禁止域的寫緩存和設(shè)置域的Cache寫策略。域的Cache位控制寫緩存位的作用。具體位分配見表15.16。

表15.16 Cache位和寫緩存位的分配策略

Cache位寫緩存區(qū)位域 屬 性

C=0B=0禁止Cache、禁止寫緩存

C=0B=1禁止Cache、使能寫緩存

C=1B=0使能Cache,域使用回寫策略

C=10B=1使能Cache,域使用直寫策略

(4)訪問權(quán)限寄存器c5

協(xié)處理器CP15的寄存器c5設(shè)置內(nèi)存域的訪問權(quán)限。

寄存器c5的編碼格式如圖15.21所示。

![]()

圖15.21 寄存器c5的編碼格式

讀寄存器c3的bits[15:0]存放域的AP(access permission,訪問權(quán)限),其中bits[2n+1:2n]對于域n的訪問權(quán)限。AP編碼與訪問權(quán)限的對應(yīng)關(guān)系如表15.17所示。

表15.17 AP編碼與訪問權(quán)限的對應(yīng)關(guān)系

AP編碼管 理 者用 戶

00不可訪問不可訪問

01讀/寫不可訪問

10讀/寫只讀

11讀/寫讀/寫

對于Arm940T、Arm940T兩個(gè)內(nèi)核版本來說,使用MRC和MCR指令對其進(jìn)行讀寫時(shí),第二個(gè)協(xié)處理器寄存器《CRm》將被忽略,指令中以c0的形式出現(xiàn)。對于指令數(shù)據(jù)統(tǒng)一的域,第二操作數(shù)《opcode2》要設(shè)成0,而對于數(shù)據(jù)和指令分離的系統(tǒng),如果opcode2=0,說明操作對數(shù)據(jù)域有效,如果opcode=1,說明操作對指令域有效。

![]() 注意對于Arm946E-S和Arm1026EJ-S兩個(gè)內(nèi)核版本,它們的訪問權(quán)限機(jī)制更復(fù)雜,采用的是擴(kuò)展AP,擴(kuò)展組AP位域編碼支持兩個(gè)增強(qiáng)的權(quán)限域,對其進(jìn)行操作的MRC和MCR指令形式更復(fù)雜,有關(guān)更詳細(xì)的內(nèi)容,請參加Arm公司的用戶手冊。

注意對于Arm946E-S和Arm1026EJ-S兩個(gè)內(nèi)核版本,它們的訪問權(quán)限機(jī)制更復(fù)雜,采用的是擴(kuò)展AP,擴(kuò)展組AP位域編碼支持兩個(gè)增強(qiáng)的權(quán)限域,對其進(jìn)行操作的MRC和MCR指令形式更復(fù)雜,有關(guān)更詳細(xì)的內(nèi)容,請參加Arm公司的用戶手冊。

(5)域大小控制寄存器c6

Arm系統(tǒng)中通過寫協(xié)處理器c6來定義域的大小,通過MCR指令中第二個(gè)操作寄存器賦不同的值來指示是對哪個(gè)具體域進(jìn)行操作。第二個(gè)操作寄存器取值為c0~c7,分別對應(yīng)域0~域7。

每個(gè)域的起始地址必須對齊到其大小的整數(shù)倍。比如,一個(gè)域的大小位64KB,其起始地址可以是0x10000的整數(shù)倍的任何數(shù)。域的大小可以是4KB~4GB的2的任意乘冪。

寄存器c6的編碼格式如圖15.22所示。

圖15.22 域大小控制寄存器c6編碼格式

編碼含義如表15.18所示

表15.18 寄存器c6編碼含義

位 名 稱對 應(yīng) 位注 釋

起始地址[31:12]保護(hù)域的第一個(gè)字節(jié)起始地址,具體見表2.18

SBZ[11:6]必須設(shè)為0

Size[5:1]設(shè)Size=N,則域尺寸為2N+1,其中11≤N≤31

E[0]域使能,E=1使能,E=0禁止

關(guān)于c6中bits[31:12],因?yàn)橛虻钠鹗家怯虼笮〉恼稊?shù),域最小為4KB,所有域起始地址的bits[11:0]通常為0,不用設(shè)置。具體c6中起始地址的設(shè)置和c6中Size(bits[5:1])的對應(yīng)關(guān)系如表15.19所示。

表15.19 域尺寸編碼

Size(bits[5:1])域 尺 寸起始地址(bits[31:12])

0b00000~0b01010未定義-

0b010114KB無

0b011008KBbit[12]必須為0

0b0110116KBbits[13:12]必須為0

0b0111032KBbits[14:12]必須為0

0b0111164KBbits[15:12]必須為0

0b10000126KBbits[16:12]必須為0

0b10001256KBbits[17:12]必須為0

0b10010512KBbits[18:12]必須為0

0b100111MBbits[19:12]必須為0

0b101002MBbits[20:12]必須為0

0b101014MBbits[21:12]必須為0

0b101108MBbits[22:12]必須為0

0b1011116MBbits[23:12]必須為0

0b1100032MBbits[24:12]必須為0

0b1100164MBbits[25:12]必須為0

0b11010128MBbits[26:12]必須為0

0b11011256MBbits[27:12]必須為0

0b11100512MBbits[28:12]必須為0

0b111011GBbits[29:12]必須為0

續(xù)表

Size(bits[5:1])域 尺 寸起始地址(bits[31:12])

0b111102GBbits[30:12]必須為0

0b111114GBbits[31:12]必須為0

一文搞懂CPU、MPU、MCU、SOC的聯(lián)系與區(qū)別

1 CPU CPU(Central Processing Unit),是一臺計(jì)算機(jī)的運(yùn)算核心和控制核心。CPU由運(yùn)算器、控制器和寄存器及實(shí)現(xiàn)它們之間聯(lián)系...

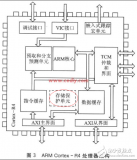

ST STM32MP157C高性能低功耗MPU開發(fā)方案

本文介紹了STM32MP157C主要特性,框圖,電源方案圖以及評估板STM32MP157C-EV1和STM32MP157A-EV1主要特性,硬件框圖和電...

FPGA基礎(chǔ)知識:什么是FPGA,為何需要FPGA?

最佳處理解決方案常常是由 RISC、CISC、圖形處理器與 FPGA 的組合提供,或由 FPGA 單獨(dú)提供,或以硬處理器內(nèi)核作為部分結(jié)構(gòu)的 FPGA 提...

一些嵌入式系統(tǒng)使用多任務(wù)的操作和控制。這些系統(tǒng)必須提供一種機(jī)制來保證正在運(yùn)行的任務(wù)不破壞其他任務(wù)的操作。即要防止系統(tǒng)資源和其他一些任務(wù)不受非法訪問。嵌入...

2017-11-03 標(biāo)簽:mpu內(nèi)存保護(hù)單元 1.3萬 0

網(wǎng)絡(luò)設(shè)備單板MPU、LPU、SFU的區(qū)別

網(wǎng)絡(luò)設(shè)備單板按功能可分為MPU、LPU、SFU。

CPU(Central Processing Unit),是一臺計(jì)算機(jī)的運(yùn)算核心和控制核心。CPU由運(yùn)算器、控制器和寄存器及實(shí)現(xiàn)它們之間聯(lián)系的數(shù)據(jù)、控制...

MPU是什么Cortex-M內(nèi)核的MPU內(nèi)存保護(hù)單元詳細(xì)講解

估計(jì)大家經(jīng)常看見MCU、MPU、MMU等這類縮寫詞,你們了解MPU嗎?

什么是MPU?MPU在哪些方面保護(hù)內(nèi)存安全?

內(nèi)存保護(hù)單元(MPU)是一種硬件機(jī)制,通過只允許代碼訪問需要的內(nèi)存和外設(shè)來提高嵌入式設(shè)備的安全性。

廣義的來說,F(xiàn)PGA的配置包括直接使用下載電纜對FPGA器件進(jìn)行編程、對外部EEPROM和FLASH進(jìn)行編程、使用MPU對FPGA器件進(jìn)行編程、外部EE...

類別:電子元器件應(yīng)用 2019-05-07 標(biāo)簽:DSP電子元器件MPU

當(dāng)為你的下一個(gè)設(shè)計(jì)方案選擇正確的核心處理器件時(shí),你應(yīng)該考慮哪些因素呢?本文將對MPU和MCU做些對比分析,并以此對器件的選擇給出一些指導(dǎo)性建議和意見。每...

淺談ALD在半導(dǎo)體先進(jìn)制程的應(yīng)用

說明:若有考慮不周,歡迎留言指正。 原子層沉積在半導(dǎo)體先進(jìn)制程的應(yīng)用 隨著集成電路工藝技術(shù)的不斷提高,晶體管的特征尺寸及刻蝕溝槽不斷減小,溝槽及其側(cè)壁的...

曾經(jīng)微控制器(MCU)與微處理器(MPU)是截然不同的兩種器件,微控制器完成“控制”相關(guān)的任務(wù),根據(jù)外界信號刺激產(chǎn)生反應(yīng),微處理器主要執(zhí)行處理功能,對數(shù)...

MPU(Memory Protection Unit)是一種硬件保護(hù)機(jī)制,用于保護(hù)嵌入式系統(tǒng)中的內(nèi)存安全。它是嵌入式處理器中的一種特殊模塊,通常與CPU...

2023-06-12 標(biāo)簽:內(nèi)存MPU保護(hù)機(jī)制 1.5萬 0

M1052跨界核心板普通MCU系統(tǒng)般簡便,卻擁有“不凡”性能

M1052跨界核心板板載Cortex-M7的RT1050處理器,既具備MPU的強(qiáng)勁處理性能,又兼顧MCU微控制器的簡單易用與實(shí)時(shí)性優(yōu)勢!M1052集成W...

所謂零開銷循環(huán)是指處理器在執(zhí)行循環(huán)時(shí),不用花時(shí)間去檢查循環(huán)計(jì)數(shù)器的值、條件轉(zhuǎn)移到循環(huán)的頂部、將循環(huán)計(jì)數(shù)器減1。與此相反,GPP的循環(huán)使用軟件來實(shí)現(xiàn):某些...

為什么要使用MPU?MPU如何實(shí)現(xiàn)內(nèi)存保護(hù)?

如果你開發(fā)的嵌入式項(xiàng)目,因內(nèi)存溢出,或者內(nèi)存故障等一些原因,造成了重大經(jīng)濟(jì)損失,或者造成了重大事故,你就能體會為什么要使用內(nèi)存保護(hù)單元(MPU)了。

現(xiàn)在的問題是,MCU開始不本分了(MPU或許也有了新想法)。隨著邊緣人工智能應(yīng)用(如語言控制設(shè)備)的興起,過去相對較笨的MCU顯得有些力不從心。但是,M...

意法半導(dǎo)體STM32MP157A MPU加持,米爾科技首款ST Linux開發(fā)板MYD-YA157C評測

ST公司去年推出了MPU系列芯片,MPU系列不同于以往產(chǎn)品,它既包含有ARM公司Cortex M 單片機(jī)核心,也包含有ARM公司Cortex A 應(yīng)用處...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |