完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

標簽 > SerDes

SERDES是(串行器)/(解串器)的簡稱。它是一種主流的時分多路復用(TDM)、點對點(P2P)的串行通信技術。

SERDES是英文SERializer(串行器)/DESerializer(解串器)的簡稱。它是一種主流的時分多路復用(TDM)、點對點(P2P)的串行通信技術。即在發送端多路低速并行信號被轉換成高速串行信號,經過傳輸媒體(光纜或銅線),最后在接收端高速串行信號重新轉換成低速并行信號。這種點對點的串行通信技術充分利用傳輸媒體的信道容量,減少所需的傳輸信道和器件引腳數目,提升信號的傳輸速度,從而大大降低通信成本。

SERDES是英文SERializer(串行器)/DESerializer(解串器)的簡稱。它是一種主流的時分多路復用(TDM)、點對點(P2P)的串行通信技術。即在發送端多路低速并行信號被轉換成高速串行信號,經過傳輸媒體(光纜或銅線),最后在接收端高速串行信號重新轉換成低速并行信號。這種點對點的串行通信技術充分利用傳輸媒體的信道容量,減少所需的傳輸信道和器件引腳數目,提升信號的傳輸速度,從而大大降低通信成本。

分類

SerDes 結構大致可以分為四類:并行時鐘SerDes:將并行寬總線串行化為多個差分信號對,傳送與數據并聯的時鐘。這些SerDes比較便宜,在需要同時使用多個SerDes 的應用中,可以通過電纜或背板有效地擴展寬總線;8B/10B 編碼SerDes:將每個數據字節映射到10bit代碼,然后將其串行化為單一信號對。10位代碼是這樣定義的:為接收器時鐘恢復提供足夠的轉換,并且保證直流平衡(即發送相等數量的‘1’和‘0’)。這些屬性使8B/10BSerDes 能夠在有損耗的互連和光纖傳輸中以較少的信號失真高速運行;嵌入式時鐘SerDes:將數據總線和時鐘串化為一個串行信號對。兩個時鐘位,一高一低,在每個時鐘循環中內嵌串行數據流,對每個串行化字的開始和結束成幀,因此這類SerDes也可稱為“開始-結束位SerDes”,并且在串行流中建立定期的上升邊沿。由于有效負載夾在嵌入式時鐘位之間,因此數據有效負載字寬度并不限定于字節的倍數;位交錯SerDes:將多個輸入串行流中的位匯聚為更快的串行信號對。SERDES技術最早應用于廣域網(WAN)通信。國際上存在兩種廣域網標準:一種是SONET,主要通行于北美;另一種是SDH,主要通行于歐洲。這兩種廣域網標準制訂了不同層次的傳輸速率。萬兆(OC-192)廣域網已在歐美開始實行,中國大陸已升級到2.5千兆(OC-48)水平。SERDES技術支持的廣域網構成了國際互聯網絡的骨干網。SERDES 并串行與串并行轉換器,串化器/并化器 A device that serializes output from, and deserializes input to, a business machine.一種(信號)轉換設備,對商業計算機的輸出(信號)進行并串行(串行化)轉換,而對其輸入(信號)進行串并行(解串)轉換。SERializer/DESerializer的縮 寫。系統的設計師們會采用串行器/解串器(SERDES)技術的高速串行接口來取代傳統的并行總線架構。基于SERDES的設計增加了帶寬,減少了信號數量,同時帶來了諸如減少布線沖突、降低開關噪聲、更低的功耗和封裝成本等許多好處。而SERDES技術的主要缺點是需要非常精確、超低抖動的元件來提供用于控制高數據速率串行信號所需的參考時鐘。即使嚴格控制元件布局,使用長度短的信號并遵循信號走線限制,這些接口的抖動余地仍然是非常小的。

理解SerDes

FPGA發展到今天,SerDes(Serializer-Deserializer)基本上是標配了。從PCI到PCI Express, 從ATA到SATA,從并行ADC接口到JESD204, 從RIO到Serial RIO,…等等,都是在借助SerDes來提高性能。SerDes是非常復雜的數模混合設計,用戶手冊的內容只是描述了森林里面的一棵小樹,并不能夠解釋SerDes是怎么工作的。SerDes怎么可以沒有傳輸時鐘信號?什么是加重和均衡?抖動和誤碼是什么關系?各種抖動之間有什么關系?本篇小文試著從一個SerDes用戶的角度來理解SerDes是怎么設計的, 由于水平有限,一定有不夠準確的地方,希望對剛開始接觸SerDes的工程師有所幫助。

Contents

1. SerDes的價值。。. 1

1.1并行總線接口。。. 1

1.2 SerDes接口。。. 3

1.3 中間類型。。. 4

2. SerDes結構(architecture) 4

2.1串行器解串器(Serializer/Deserializer) 6

2.2發送端均衡器( Tx Equalizer) 8

2.3接收端均衡器( Rx Equalizer) 9

2.4時鐘數據恢復(CDR) 13

2.5 公用鎖相環(PLL) 16

2.6 SerDes編解碼。。. 18

2.7 SerDes收發Driver及差分接口轉換。。. 19

2.8 SerDes環回和調試。。. 19

3.抖動和信號集成( Jitter, SI ) 19

3.1 時鐘的抖動(clock jitter) 19

3.2. 數據的抖動(data jitter) 20

4.信號集成(SI)及仿真。。. 23

4.1信道channel 23

4.2 芯片封裝Package. 24

4.3 SI仿真。。. 24

5. 結尾。。. 25

6.參考資料 了解更多的內容,可以閱讀以下內容。。。. 25

1. SerDes的價值

1.1并行總線接口

在SerDes流行之前,芯片之間的互聯通過系統同步或者源同步的并行接口傳輸數據,圖1.1演示了系統和源同步并行接口。

隨著接口頻率的提高,在系統同步接口方式中,有幾個因素限制了 有效數據窗口寬度 的繼續增加。

l 時鐘到達兩個芯片的傳播延時不相等(clock skew)

l 并行數據各個bit的傳播延時不相等(data skew)

l 時鐘的傳播延時和數據的傳播延時不一致(skew between data and clock)

雖然可以通過在目的芯片(chip #2)內用PLL補償時鐘延時差(clock skew),但是PVT變化時,時鐘延時的變化量和數據延時的變化量是不一樣的。這又進一步惡化了數據窗口。

源同步接口方式中,發送側Tx把時鐘伴隨數據一起發送出去, 限制了clock skew對有效數據窗口的危害。通常在發送側芯片內部,源同步接口把時鐘信號和數據信號作一樣的處理,也就是讓它和數據信號經過相同的路徑,保持相同的延時。這樣PVT變化時,時鐘和數據會朝著同一個方向增大或者減小相同的量,對skew最有利。

我們來做一些合理的典型假設,假設一個32bit數據的并行總線,

a)發送端的數據skew = 50 ps ---很高的要求

b)pcb走線引入的skew = 50ps ---很高的要求

c)時鐘的周期抖動jitter = +/-50 ps ---很高的要求

d)接收端觸發器采樣窗口 = 250 ps ---Xilinx V7高端器件的IO觸發器

可以大致估計出并行接口的最高時鐘 = 1/(50+50+100+250) = 2.2GHz (DDR)或者1.1GHz (SDR)。

利用源同步接口,數據的有效窗口可以提高很多。通常頻率都在1GHz以下。在實際應用中可以見到如SPI4.2接口的時鐘可以高達DDR 700MHz x 16bits位寬。DDR Memory接口也算一種源同步接口,如DDR3在FPGA中可以做到大約800MHz的時鐘。

要提高接口的傳輸帶寬有兩種方式,一種是提高時鐘頻率,一種是加大數據位寬。那么是不是可以無限制的增加數據的位寬呢?這就要牽涉到另外一個非常重要的問題-----同步切換噪聲(SSN)。

這里不討論SSN的原理,直接給出SSN的公式 SSN = L *N* di/dt。L是芯片封裝電感,N是數據寬度,di/dt是電流變化的斜率。隨著頻率的提高,數據位款的增加,SSN成為提高傳輸帶寬的主要瓶頸。圖1.2是一個DDR3串擾的例子。圖中低電平的理論值在0V,由于SSN的影響,低電平表現為震蕩,震蕩噪聲的最大值達610mV,因此噪聲余量只有1.5V/2-610mV=140mV。

Figure 1.2 DDR3串擾演示

因此也不可能靠無限的提高數據位寬來繼續增加帶寬。一種解決SSN的辦法是使用差分信號替代單端信號,使用差分信號可以很好的解決SSN問題,代價是使用更多的芯片引腳。使用差分信號仍然解決不了數據skew的問題,很大位寬的差分信號再加上嚴格的時序限制,給并行接口帶來了很大的挑戰。

1.2 SerDes接口

源同步接口的時鐘頻率已經遇到瓶頸,由于信道的非理想(channel)特性,再繼續提高頻率,信號會被嚴重損傷,就需要采用均衡和數據時鐘相位檢測等技術。這也就是SerDes所采用的技術。SerDes(Serializer-Deserializer)是串行器和解串器的簡稱。串行器(Serializer)也稱為SerDes發送端(Tx),(Deserializer)也稱為接收端Rx。Figure1.3是一個N對SerDes收發通道的互連演示,一般N小于4。

可以看到,SerDes不傳送時鐘信號,這也是SerDes最特別的地方,SerDes在接收端集成了CDR(Clock Data Recovery)電路,利用CDR從數據的邊沿信息中抽取時鐘,并找到最優的采樣位置。

SerDes采用差分方式傳送數據。一般會有多個通道的數據放在一個group中以共享PLL資源,每個通道仍然是相互獨立工作的。

SerDes需要參考時鐘(Reference Clock),一般也是差分的形式以降低噪聲。接收端Rx和發送端Tx的參考時鐘可以允許幾百個ppm的頻差(plesio-synchronous system),也可以是同頻的時鐘,但是對相位差沒有要求。

作個簡單的比較,一個SerDes通道(channel)使用4個引腳(Tx+/-,Rx+/-), 目前的FPGA可以做到高達28Gbps。而一個16bits的DDR3-1600的線速率為1.6Gbps*16 = 25Gbps,卻需要50個引腳。此對比可以看出SerDes在傳輸帶寬上的優勢。

相比源同步接口,SerDes的主要特點包括:

l SerDes在數據線中時鐘內嵌,不需要傳送時鐘信號。

l SerDes通過加重/均衡技術可以實現高速長距離傳輸,如背板。

l SerDes 使用了較少的芯片引腳

1.3 中間類型

也存在一些介于SerDes和并行接口之間的接口類型,相對源同步接口而言,這些中間類型的接口也使用串行器(Serializer)解串器(Deserializer),同時也傳送用于同步的時鐘信號。這類接口如視頻顯示接口7:1 LVDS等。

2. SerDes結構(architecture)

SerDes的主要構成可以分為三部分,PLL模塊,發送模塊Tx,接收模塊Rx。為了方便維護和測試,還會包括控制和狀態寄存器,環回測試,PRBS測試等功能。見圖2.1。

Figure 2.1 Basic Blocks of a typical SerDes

圖中藍色背景子模塊為PCS層,是標準的可綜合CMOS數字邏輯,可以硬邏輯實現,也可以使用FPGA軟邏輯實現,相對比較容易被理解。褐色背景的子模塊是PMA層,是數模混合CML/CMOS電路,是理解SerDes去別于并行接口的關鍵,也是本文要討論的內容。

發送方向(Tx)信號的流向: FPGA軟邏輯(fabric)送過來的并行信號,通過接口FIFO(Interface FIFO), 送給8B/10B編碼器(8B/10B encoder)或擾碼器(scambler),以避免數據含有過長連零或者連1。之后送給串行器(Serializer)進行 并-》串 轉換。串行數據經過均衡器(equalizer)調理,有驅動器(driver)發送出去。

接收方向(Rx)信號的流向, 外部串行信號由線性均衡器(Linear Equalizer)或DFE (Decision Feedback Equalizer)結構均衡器調理,去除一部分確定性抖動(Deterministic jitter)。CDR從數據中恢復出采樣時鐘,經解串器變為對齊的并行信號。8B/10B解碼器(8B/10B decoder)或解擾器(de-scambler)完成解碼或者解擾。如果是異步時鐘系統(plesio-synchronous system),在用戶FIFO之前還應該有彈性FIFO來補償頻差。

PLL負責產生SerDes各個模塊所需要的時鐘信號,并管理這些時鐘之間的相位關系。以圖中線速率10Gbps為例,參考時鐘頻率250MHz。Serializer/Deserializer至少需要5GHz 0相位時鐘和5GHz 90度相位時鐘,1GHz(10bit并行)/1.25GHz(8bit并行)時鐘等。

一個SerDes通常還要具調試能力。例如偽隨機碼流產生和比對,各種環回測試,控制狀態寄存器以及訪問接口,LOS檢測, 眼圖測試等。

2.1串行器解串器(Serializer/Deserializer)

串行器Serializer把并行信號轉化為串行信號。Deserializer把串行信號轉化為并行信號。一般地,并行信號為8 /10bit或者16/20bit寬度,串行信號為1bit寬度(也可以分階段串行化,如8bit-》4bit-》2bit-》equalizerà1bit以降低equalizer的工作頻率)。采用擾碼(scrambled)的協議如SDH/SONET, SMPTE SDI使用8/16bit的并行寬度,采用8B/10B編碼的協議如PCIExpress,GbE使用10bits/20bits寬度。

一個4:1的串行器如圖xxx所示。8:1或16:1的串行器采用類似的實現。實現時,為了降低均衡器的工作頻率,串行器會先把并行數據變為2bits,送給均衡器equalizer濾波,最后一步再作2:1串行化,本文后面部分都按1bit串行信號解釋。

一個1:4的解串器如圖2.3所示,8:1或16:1的解串器采用類似的實現。實現時,為了降低均衡器(DFE based Equalizer)的工作頻率,DFE工作在DDR模式下,解串器的輸入是2bit或者更寬,本文后面部分都按1bit串行信號解釋。

Serializer/Deserializer的實現采用雙沿(DDR)的工作方式,利用面積換速度的策略,降低了電路中高頻率電路的比例,從而降低了電路的噪聲。

接收方向除了Deserializer之外,一般帶有還有對齊功能邏輯(Aligner)。相對SerDes發送端,SerDes接收端起始工作的時刻是任意的,接收器正確接收的第一個 bit可能是發送并行數據的任意bit位置。因此需要對齊邏輯來判斷從什么bit位置開始,以組成正確的并行數據。對齊邏輯通過在串行數據流中搜索特征碼字(Alignment Code)來決定串并轉換的起始位置。比如8B/10B編碼的協議通常用K28.5(正碼10’b1110000011,負碼10’b0001111100)來作為對齊字。圖2.4為一個對齊邏輯的演示。通過滑窗,逐bit比對,以找到對齊碼(Align-Code)的位置,經過多次在相同的位置找到對齊碼之后,狀態機鎖定位置并選擇相應的位置輸出對齊數據。

2.2發送端均衡器( Tx Equalizer)

SerDes信號從發送芯片到達接收芯片所經過的路徑稱為信道(channel),包括芯片封裝,pcb走線,過孔,電纜,連接器等元件。從頻域看,信道可以簡化為一個低通濾波器(LPF)模型,如果SerDes的速率大于信道(channel)的截止頻率,就會一定程度上損傷(distort)信號。均衡器的作用就是補償信道對信號的損傷。

發送端的均衡器采用FFE(Feed forward equalizers)結構,發送端的equalizer也稱作加重器(emphasis)。加重(Emphasis)分為去加重(de-emphasis)和預加重(pre-emphasis)。De-emphasis降低差分信號的擺幅(swing)。Pre-emphasis增加差分信號的擺幅。FPGA大部分使用de-emphasis的方式,加重越強,信號的平均幅度會越小。

發送側均衡器設計為一個高通濾波器(HPF),大致為信道頻響H(f)的反函數H-1(f),FFE的目標是讓到達接收端的信號為一個干凈的信號。FFE的實現方式有很多,一個典型的例子如圖2.5所示。

調節濾波器的系數可以改變濾波器的頻響,以補償不同的信道特性,一般可以動態配置。以10Gbps線速率為例,圖2.5為DFE頻率響應演示。可以看到,對于C0=0,C1=1.0,C2=-0.25的配置,5GHz處高頻增益比低頻區域高出4dB,從而補償信道對高頻頻譜的衰減。

采樣時鐘的頻率限制了這種FFE最高只能補償到Fs/2(例子中Fs/2=5GHz)。根據采樣定理,串行數據里的信息都包含在5GHz以內,從這個角度看也就足夠了。如果要補償Fs/2以上的頻率,就要求FFE高于Fs的工作時鐘,或者連續時間域濾波器(Continuous Time FFE)。

圖2.7為DFE時域濾波效果的演示,以10Gbps線速率為例,一個UI=0.1 nS=100ps。演示的串行數據碼流為二進制[00000000100001111011110000]。

HDMI、Type-C、SerDes?、LVDS等協議及傳輸接口芯片解析

數據在兩個設備之間傳輸或者同設備內部連接傳輸音視頻等高速信號數據時,需要有規范的傳輸協議。

在高速串行通信系統中,差分阻抗的精確控制是實現信號完整性和降低電磁干擾的關鍵因素,對電子工程師來說,理想中的差分阻抗是100Ω,但由于實際布線原因,如接...

國科微斬獲“強芯中國創新IC”獎項,車載SerDes芯片漸入佳境

9月25日,2024中國集成電路設計創新大會暨第四屆?IC應用展(ICDIA-IC?Show)在江蘇無錫開幕。同期,首屆“強芯中國-2024創新IC”評...

電子發燒友網報道(文/梁浩斌)在車載網絡通信系統中,過去最為常見的是CAN總線、LIN總線等,多個分布式的ECU通過CAN、LIN等總線系統進行連接,而...

2024-09-30 標簽:SerDes 4066 0

電子發燒友網報道(文/梁浩斌)隨著自動駕駛攝像頭等傳感器的不斷升級,數據傳輸量呈指數級提升,近幾年高速SerDes在電動汽車上的需求開始受到關注,多家國...

聚焦MIPI 系列之三:汽車SerDes – 實現更好的ADAS攝像頭傳感器

作者:是德科技 Hwee Yng Yeo HDR 相機的世界不僅限于為您的手機或超高清電視屏幕提供令人驚艷的視覺效果。如今,高性能相機越來越多地應用于現...

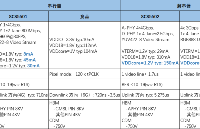

兼容MAX9295A/MAX96717,SCS5501/SCS5502車載攝像頭量產

新能源汽車的熱潮,大大增加了車載網絡和電子系統的復雜性,需要更多的傳感器和執行器來支持各種智能功能。Serdes(串行器/解串器)技術因其在高速數據傳輸...

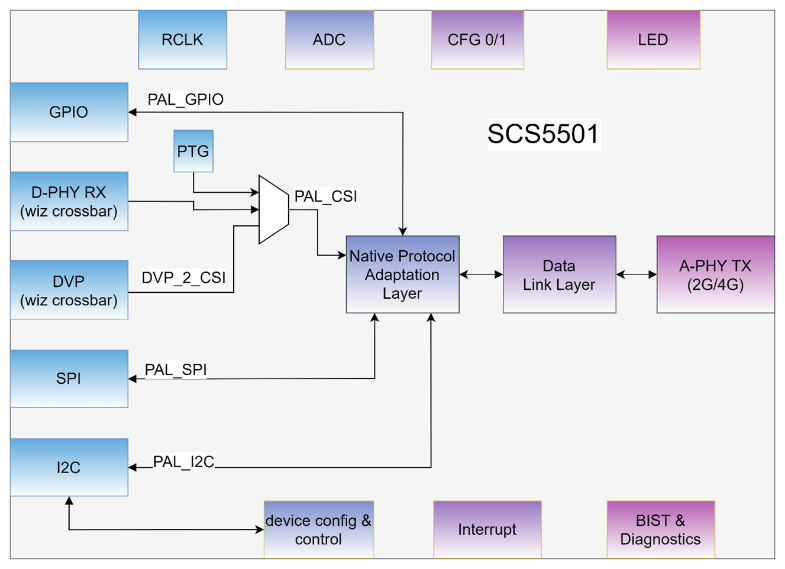

芯熾科技發布革新性MIPI A-PHY SerDes芯片組, 驅動車載與長距視頻傳輸技術邁入新紀元

在近日舉辦的2024慕尼黑上海電子展上,上海芯熾科技集團有限公司隆重推出了兩款專為汽車應用量身打造的新型串行解串器(SerDes)芯片:SCS5501與...

換一批

換一批

編輯推薦廠商產品技術軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯網 | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發電 | UPS | AR | 智能電網 | 國民技術 | Microchip |

| 開關電源 | 步進電機 | 無線充電 | LabVIEW | EMC | PLC | OLED | 單片機 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 藍牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太網 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 語音識別 | 萬用表 | CPLD | 耦合 | 電路仿真 | 電容濾波 | 保護電路 | 看門狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 閾值電壓 | UART | 機器學習 | TensorFlow |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |