完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > Vivado

Vivado設(shè)計(jì)套件,是FPGA廠商賽靈思公司2012年發(fā)布的集成設(shè)計(jì)環(huán)境。包括高度集成的設(shè)計(jì)環(huán)境和新一代從系統(tǒng)到IC級(jí)的工具,這些均建立在共享的可擴(kuò)展數(shù)據(jù)模型和通用調(diào)試環(huán)境基礎(chǔ)上。

文章:596個(gè) 視頻:169個(gè) 瀏覽:66347次 帖子:933個(gè)

無(wú)論此刻你是一個(gè)需要安裝Xilinx Vivado工具鏈的入門(mén)菜鳥(niǎo),還是已有l(wèi)icense過(guò)期的Vivado老鐵,今兒咱就借著這篇文章,把學(xué)習(xí)「Viva...

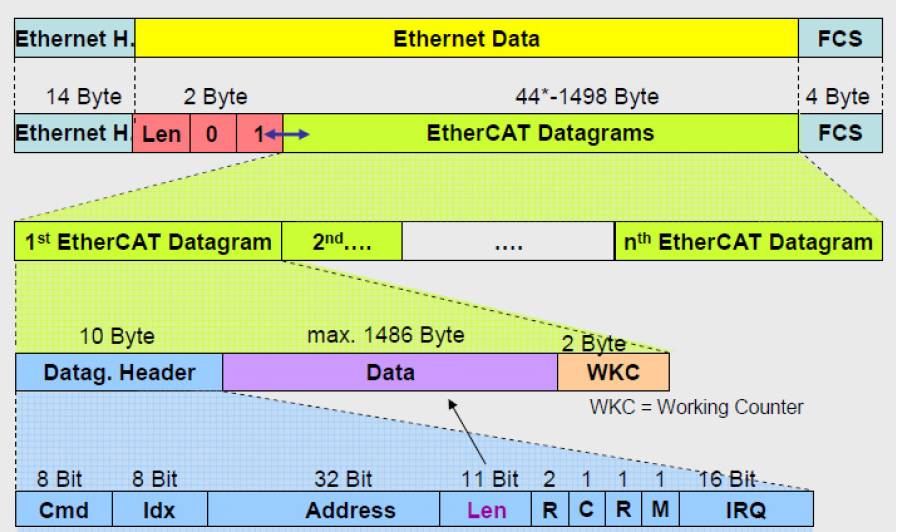

KPA EtherCAT主站在Zynq平臺(tái)的移植與測(cè)試

實(shí)驗(yàn)平臺(tái)包括三個(gè)組成部分:待測(cè)試的EtherCAT系統(tǒng)、實(shí)時(shí)數(shù)據(jù)獲取單元和離線的實(shí)驗(yàn)數(shù)據(jù)分析單元,如下圖所示。主站為構(gòu)建的嵌入式實(shí)時(shí)EtherCAT 主...

2019-07-30 標(biāo)簽:以太網(wǎng)通信設(shè)備Vivado 3.9萬(wàn) 0

在Vivado中新建IO Planning工程來(lái)初步引腳分配

在Vivado中新建IO Planning工程來(lái)初步引腳分配,這樣會(huì)大大提高開(kāi)發(fā)效率 在這里,你可以選擇最右側(cè)的開(kāi)發(fā)板型號(hào),也可以選擇Part,具體的...

本文通過(guò)一個(gè)簡(jiǎn)單的例子,介紹Vivado 下的仿真過(guò)程。主要參考了miz702的教程,同時(shí)也參考了Xilinx的ug937, xapp199.。

Vivado中綜合實(shí)現(xiàn)和出bit文件步驟教程

本文詳解綜合實(shí)現(xiàn)和出bit文件。各Block都搭建完成后,選中這個(gè)bd右鍵,Generate Output Products主要是把IP參數(shù)和連接信息u...

大家好,又到了每日學(xué)習(xí)的時(shí)間了,今天咱們來(lái)聊一聊vivado 調(diào)用IP核。 首先咱們來(lái)了解一下vivado的IP核,IP核(IP Core):Vivad...

Vivado FPGA設(shè)計(jì)基礎(chǔ)操作流程:Vivado的基本使用

選擇器件或者板卡。Parts表示器件,當(dāng)然如果是板卡就點(diǎn)擊Boards。器件可以根據(jù)系列去選,也可以直接在Search欄搜索器件型號(hào)。器件的選擇根據(jù)你的...

Vivado工程經(jīng)驗(yàn)與各種時(shí)序約束技巧分享

首先強(qiáng)烈推薦閱讀官方文檔UG903和UG949,這是最重要的參考資料,沒(méi)有之一。它提倡要在設(shè)計(jì)的早期階段就要排除問(wèn)題,越到后期時(shí)序的改善就越困難。其中H...

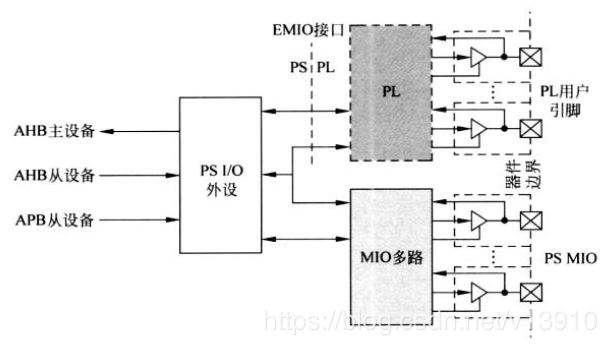

MIO與EMIO的關(guān)系解析 GPIO、MIO、EMIO的區(qū)別

芯片型號(hào):XC7Z010-1CLG400C Vivado版本:2016.1 點(diǎn)亮流水燈,共使用了三種方式: (1)PS通過(guò)MIO點(diǎn)亮PS端LED (2)...

Vivado綜合操作中的重定時(shí)(Retiming)

有兩種不同的重定時(shí)方法,向后重定時(shí)和向前重定時(shí)。向后重定時(shí)從門(mén)的輸出中刪除寄存器,并在同一邏輯門(mén)的輸入出創(chuàng)建新的寄存器。向前重定時(shí)的作用正好相反,它從邏...

5

0

Vivado中做MicroBlaze實(shí)驗(yàn) SDK報(bào)錯(cuò):Cannot stop MicroBlaze. Stalled on instruction fetch

標(biāo)簽:計(jì)數(shù)器Vivado 37926 5

電子系統(tǒng)設(shè)計(jì)實(shí)驗(yàn)指導(dǎo)書(shū)(FPGA基礎(chǔ)篇_Vivado版).PDF立即下載

類別:FPGA/ASIC 2016-07-25 標(biāo)簽:FPGA電子系統(tǒng)設(shè)計(jì)Vivado 2875 0

類別:嵌入式開(kāi)發(fā) 2014-11-03 標(biāo)簽:集成設(shè)計(jì)vivado 2404 3

類別:嵌入式開(kāi)發(fā) 2012-04-25 標(biāo)簽:IDEVivadovivado視頻 2176 2

Xilinx ISE Design Suite 14.2 安裝圖解

電子發(fā)燒友網(wǎng)核心提示 :Xilinx ISE 14.2安裝指南,包括Xilinx ISE 14.2軟件下載、Xilinx ISE 14.2軟件安裝、Xi...

Vivado HLS和Vitis HLS 兩者之間有什么區(qū)別

Vivado HLS 2020.1將是Vivado HLS的最后一個(gè)版本,取而代之的是VitisHLS。那么兩者之間有什么區(qū)別呢? Default Us...

Vivado中的靜態(tài)時(shí)序分析工具Timing Report的使用與規(guī)范

《XDC約束技巧》系列中討論了XDC約束的設(shè)置方法、約束思路和一些容易混淆的地方。我們提到過(guò)約束是為了設(shè)計(jì)服務(wù),寫(xiě)入Vivado中的XDC實(shí)際上就是用戶...

集成邏輯分析儀 (Integrated Logic Analyzer :ILA) 功能允許用戶在 FPGA 設(shè)備上執(zhí)行系統(tǒng)內(nèi)調(diào)試后實(shí)現(xiàn)的設(shè)計(jì)。當(dāng)設(shè)計(jì)中需...

2022-02-08 標(biāo)簽:Vivado 2.6萬(wàn) 0

關(guān)于Vivado三種常用IP核的調(diào)用詳細(xì)解析

vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如數(shù)學(xué)運(yùn)算(乘法器、除法器、浮點(diǎn)運(yùn)算器等)、信號(hào)處理(FFT、...

2021-04-27 標(biāo)簽:ROMIP核實(shí)時(shí)仿真 2.4萬(wàn) 0

VIVADO中時(shí)序報(bào)告中WNS、WHS、TNS、THS有什么含義

VIVADO中時(shí)序報(bào)告中WNS,WHS,TNS,THS含義運(yùn)行“report_timing”或“report_timing_summary”命令后,會(huì)注...

上面我們講的都是xdc文件的方式進(jìn)行時(shí)序約束,Vivado中還提供了兩種圖形界面的方式,幫我們進(jìn)行時(shí)序約束:時(shí)序約束編輯器(Edit Timing Co...

利用Vivado進(jìn)行MicroBlaze處理器應(yīng)用教程

1、在工作流導(dǎo)向面板中的IP Integrator中,點(diǎn)擊Create Block Design。(表示你要開(kāi)始構(gòu)建帶有IP核的框圖了) 2、Add ...

2017-11-17 標(biāo)簽:microblazevivado 1.9萬(wàn) 0

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語(yǔ)言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無(wú)刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺(jué) | 無(wú)人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹(shù)莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |