完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > 加法器

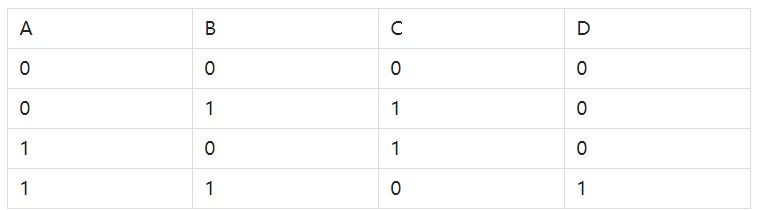

加法器是產(chǎn)生數(shù)的和的裝置。加數(shù)和被加數(shù)為輸入,和數(shù)與進(jìn)位為輸出的裝置為半加器。若加數(shù)、被加數(shù)與低位的進(jìn)位數(shù)為輸入,而和數(shù)與進(jìn)位為輸出則為全加器。常用作計(jì)算機(jī)算術(shù)邏輯部件,執(zhí)行邏輯操作、移位與指令調(diào)用。在電子學(xué)中,加法器是一種數(shù)位電路,其可進(jìn)行數(shù)字的加法計(jì)算。

文章:135個(gè) 視頻:43個(gè) 瀏覽:30093次 帖子:82個(gè)

加法運(yùn)放電路實(shí)驗(yàn)報(bào)告數(shù)據(jù)分析

加法運(yùn)放電路實(shí)驗(yàn)報(bào)告的數(shù)據(jù)分析主要包括對(duì)實(shí)驗(yàn)結(jié)果的觀察、與理論值的對(duì)比以及誤差原因的分析。以下是一個(gè)基于常見加法運(yùn)放電路實(shí)驗(yàn)的數(shù)據(jù)分析示例: 一、實(shí)驗(yàn)?zāi)?..

加法器不是時(shí)序邏輯電路 ,而是組合邏輯電路的一種。時(shí)序邏輯電路和組合邏輯電路的主要區(qū)別在于它們?nèi)绾翁幚磔敵鲂盘?hào)。 組合邏輯電路的輸出僅依賴于當(dāng)前的輸入信...

2024-08-28 標(biāo)簽:加法器時(shí)序邏輯電路輸出信號(hào) 435 0

增益為1的加法器指的是輸出信號(hào)的幅度與輸入信號(hào)幅度相等的加法器。這類加法器在模擬電路設(shè)計(jì)中非常重要,因?yàn)樗鼈冊(cè)趫?zhí)行加法運(yùn)算的同時(shí),不會(huì)改變信號(hào)的幅度。

2024-05-23 標(biāo)簽:模擬電路運(yùn)算放大器加法器 1023 0

串行加法器和并行加法器是兩種基本的數(shù)字電路設(shè)計(jì),用于執(zhí)行二進(jìn)制數(shù)的加法運(yùn)算。它們?cè)谠O(shè)計(jì)哲學(xué)、性能特點(diǎn)以及應(yīng)用場(chǎng)景上有著明顯的區(qū)別。

頻分復(fù)用(FDM)是一種經(jīng)典的多路通信技術(shù),它允許多個(gè)信號(hào)在同一傳輸媒介上同時(shí)傳輸,而互不干擾。

數(shù)據(jù)表示與編碼的奧秘:為什么8位數(shù)據(jù)范圍是-128到127?

ALU的核心是加法器,這是個(gè)隨參與計(jì)算的數(shù)值的二進(jìn)制位數(shù)指數(shù)增長(zhǎng)的數(shù)字電路。較早期的CPU里面絕大多數(shù)的邏輯門都被拿來做這個(gè)加法器了。

開關(guān)的斷開與閉合分別對(duì)應(yīng)著電路的斷開與連通。而小燈泡的不亮與亮,也分別對(duì)應(yīng)著電路的斷開與連通。那這兩者就可以統(tǒng)一,不再依賴于具體的實(shí)物表現(xiàn)了。

2024-03-19 標(biāo)簽:振蕩器計(jì)算機(jī)加法器 1728 0

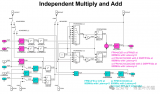

Versal FPGA中的浮點(diǎn)計(jì)算單元DSPFP32介紹

Versal FPGA中最新的DSP原語(yǔ)DSP58,它在最新的DSP48版本上已經(jīng)有了許多改進(jìn),主要是從27x18有符號(hào)乘法器和48位后加法器增加到了2...

集成運(yùn)算放大器構(gòu)成基本模擬信號(hào)運(yùn)算電路立即下載

類別:模擬數(shù)字 2023-06-16 標(biāo)簽:放大器加法器集成運(yùn)算放大器 302 0

類別:電子資料 2022-12-23 標(biāo)簽:連接器加法器dip開關(guān) 300 0

類別:電子資料 2022-10-20 標(biāo)簽:計(jì)數(shù)器加法器減法器 299 0

類別:C語(yǔ)言|源代碼 2021-05-31 標(biāo)簽:加法器全加器 938 0

加法器結(jié)構(gòu)和硬件乘法器的基礎(chǔ)使用工程文件免費(fèi)下載立即下載

類別:C語(yǔ)言|源代碼 2021-03-08 標(biāo)簽:控制電路加法器乘法器 773 0

使用Verilog/SystemVerilog硬件描述語(yǔ)言 (HDL) 練習(xí)數(shù)字硬件設(shè)計(jì)

給出了一個(gè)可以做16bit加法的模塊add16,實(shí)例化兩個(gè)add16以達(dá)到32bit加法的。

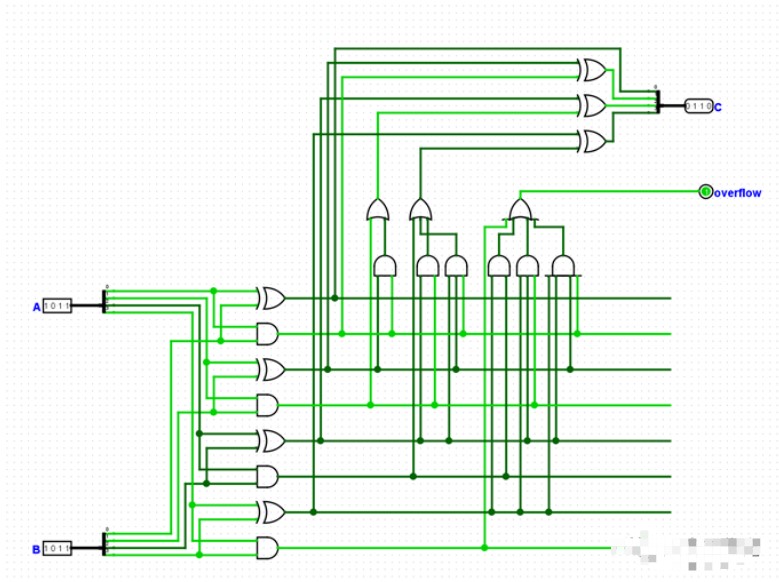

這是三位加法器,其中加數(shù)分別是101(5)和10(2),和是111(7)右下角粉紅圈中的是溢出信號(hào)(最高位的進(jìn)位信號(hào)),第一位數(shù)字沒有前一位的進(jìn)位信號(hào),...

模擬計(jì)算機(jī)相比數(shù)字計(jì)算機(jī)真的就一無是處了嗎

模擬計(jì)算機(jī)顧名思義,使用模擬量進(jìn)行計(jì)算。但由于容易受到外界環(huán)境干擾,難以得到精確解,并且隨著數(shù)字電路不斷地發(fā)揚(yáng)壯大,模擬計(jì)算機(jī)被拋棄在了歷史的長(zhǎng)河中。那...

在SpinalHDL中如何像軟件調(diào)用方法那樣優(yōu)雅地例化端口

習(xí)慣了寫Verilog的小伙伴們?cè)谧龃笮凸こ虝r(shí)是否有遇到過連續(xù)數(shù)天時(shí)間化身“連線工程師”去例化模塊、為端口賦值連接的場(chǎng)景(關(guān)鍵是這些工作量老板他也不認(rèn))...

關(guān)于二進(jìn)制表示和補(bǔ)碼計(jì)算的來龍去脈

一、前言 計(jì)算機(jī)最喜歡的數(shù)字就是 0 和 1,在 CPU 的世界中,它只認(rèn)識(shí)這兩個(gè)數(shù)字,即使是強(qiáng)大的操作系統(tǒng),也都是由 0 和 1 組成的。 作為一名軟...

2021-06-07 標(biāo)簽:cpu計(jì)算機(jī)加法器 2460 0

我們都知道,「通電」代表「真」,用邏輯1表示;「不通電」代表「假」,用邏輯0表示。「與門」電路是用晶體管搭建的,符號(hào)長(zhǎng)這樣: A與B的通斷,可以決定Y點(diǎn)...

2021-05-28 標(biāo)簽:數(shù)據(jù)加法器鎖存器 4502 0

如何搭建一個(gè)加法器的UVM驗(yàn)證平臺(tái)

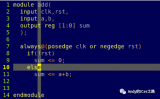

RTL就是一個(gè)帶時(shí)序的1bit加法器,然后驗(yàn)證是否功能正確。理論上的正確功能應(yīng)該是輸入數(shù)據(jù)a和數(shù)據(jù)b之后的下個(gè)周期輸出結(jié)果sum等于a+b。

從零開始學(xué)FPGA-Verilog語(yǔ)法基礎(chǔ)(中)

這個(gè)程序要找對(duì)一一對(duì)應(yīng)關(guān)系,例如脈沖模塊里的clock對(duì)應(yīng)posedge clock中的clock,程序行與行之間是有聯(lián)系的,不能隨便聲明。

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語(yǔ)言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |