完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

電子發燒友網技術文庫為您提供最新技術文章,最實用的電子技術文章,是您了解電子技術動態的最佳平臺。

智能科技已經無縫融入到每個人的生活中。使用智能音箱查詢天氣、播放歌曲、甚至進行會議提醒確實很方便,但如果黑客能夠訪問你所有的數據和交易信息,那會不會是一場災難呢?在萬物智能(Pervasive Intelligence)時代,人工智能(AI)和安全已經成為超越傳統芯片設計界限的關鍵因素。 半導體行業...

當前的電源設計正越來越多地轉向更高級別的架構,包括高效拓撲和數字電源。因此,工程師們現在希望通過人工智能進行更大量的數字仿真,以推動日益復雜的設計以及電源和射頻工作。...

DFT Design For Test,可測性設計。芯片內部往往都自帶測試電路,DFT的目的就是在設計的時候就考慮將來的測試。DFT的常見方法就是,在設計中插入掃描鏈,將非掃描單元(如寄存器)變為掃描單元。...

十多年來,EDA高層管理人員一直在尋求擴展到相鄰市場的機會但無果。實際上,直到2016年西門子以45億美元收購Mentor Graphics之前,該領域唯一重要的一步是朝相反的方向邁出的。自那時以來,有三件事發生了根本性的變化。...

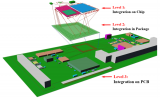

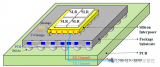

封裝內集成的基本單元是上一步完成的裸芯片或者小芯片Chiplet,我們稱之為功能單元 (Function Unit),這些功能單元在封裝內集成形成了SiP。...

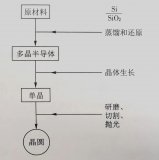

從液態的熔融硅中生長單晶硅的及基本技術稱為直拉法(Czochralski)。半導體工業中超過90%的單晶硅都是采用這種方法制備的。...

在當前高速設計中,主流的還是PAM4的設計,包括當前的56G,112G以及接下來的224G依然還是這樣。突破摩爾定律2.5D和3D芯片的設計又給高密度高速率芯片設計帶來了空間。...

EDA,是指電子設計自勱化( Electronic Design Automation)用于芯片設計時的重要工具,設計時工程師會用程式碼規劃芯片功能,再透過EDA 工具讓程式碼轉換成實際的電路設計圖。...

制程技術決定了芯片上晶體管的尺寸和密度。較小的晶體管尺寸意味著更高的集成度,可以提供更高的性能和更低的功耗。...

先進封裝中架構的豐富性和失敗的高成本鼓勵器件設計流程和封裝廠之間更密切的合作。EDA 公司和 OSAT 正在開發協作設計工具集,以提高封裝性能、降低成本并縮短集成封裝的上市時間。...

納米片晶體管并不能拯救摩爾定律,也不能解決代工廠在最先進工藝節點上面臨的所有挑戰。為了克服這些問題,代工廠正在尋求各種創新,例如背面供電(BSPD),以在節省功耗的同時從晶體管之間的互聯中獲得更多性能。...

機遇總是與挑戰并存,目前國內在高端EDA工具研發方面,面臨著如Synopsys、Cadence和Mentor等國際EDA供應商的巨大挑戰,即使是作為本土最大的EDA公司,華大九天目前也只能夠提供產業所需EDA解決方案的1/3左右。...

SOC ( System on Chip)是在同一塊芯片中集成了CPU、各種存儲器、總線系統、專用模塊以及多種l/O接口的系統級超大規模集成電路。 由于SOC芯片的規模比較大、內部模塊的類型以及來源多樣,因此SOC芯片的DFT面臨著諸多問題。...

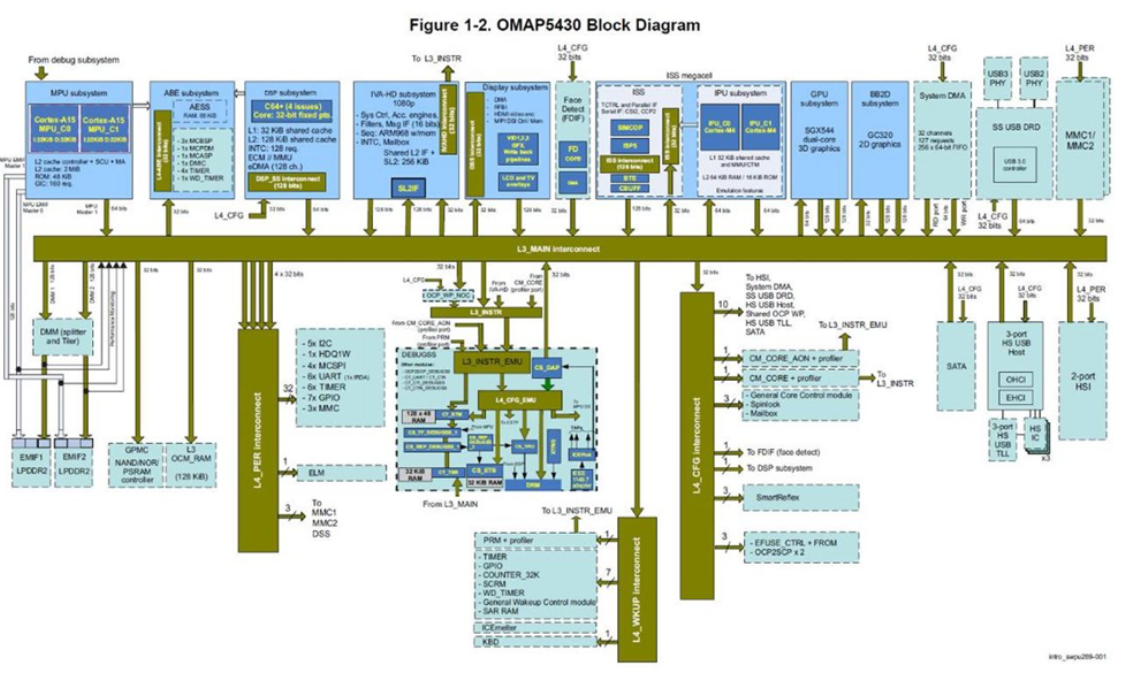

考慮當今使用的層次結構形式的最簡單方法是要求工程師從概念上設計一個系統。他們可能會開始繪制一個包含大塊的框圖,其中包含 CPU、編碼器、顯示子系統等標簽。這不是一個功能層次結構,盡管許多劃分的塊被認為是提供功能的。這也不是純粹的結構分解,因為在芯片中,一切都變成了晶體管的無定形海洋。...

DIP是很多中小規模集成電路喜歡采用的封裝形式,其引腳數一般不超過100個。采用DIP封裝的CPU芯片有兩排引腳,在使用時,需要插入到具有DIP結構的芯片插座上,也可以直接插在電路板上進行焊接,如傳統的8051單片機很多采用這種封裝形式。...

芯天成版圖集成工具EsseDBScope,是基于國微芯EDA統一數據底座研發的標志性工具,本次推出的更新版本,新增了IP merge、LVL、Signal tracing、PG Find short等功能。...