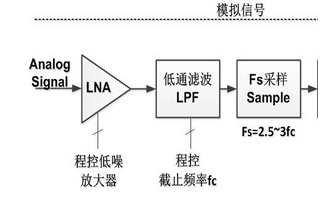

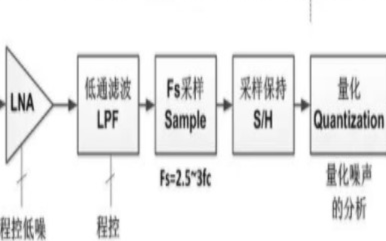

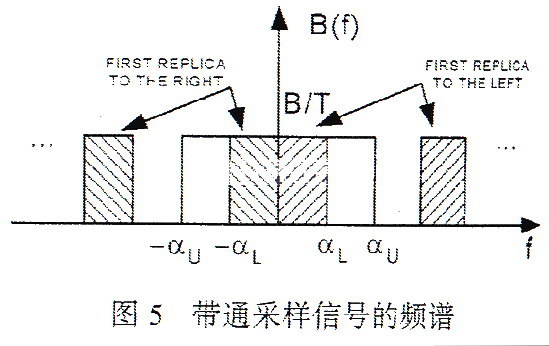

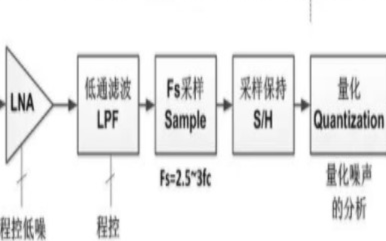

實際中,信號往往是無線帶寬的,如何保證帶寬有限?所以,我們在模擬信號輸入端要加一個低通濾波器,使信號變成帶寬有限,再使用2.5~3倍的最高信號頻率進行采樣。關于此我們下面將模擬數字轉換過程將會看到。

2018-02-26 09:13:00 22038

22038

RF采樣轉換器可捕獲高頻信號和大帶寬信號;但是,并非每種應用都能利用需要極高速采樣的信號。就帶寬或輸出頻率不過高的情況而言,利用RF采樣轉換器的高采樣速率能力仍存在一大優勢。 采樣定理規定,采樣速率

2018-05-15 09:12:14 8377

8377

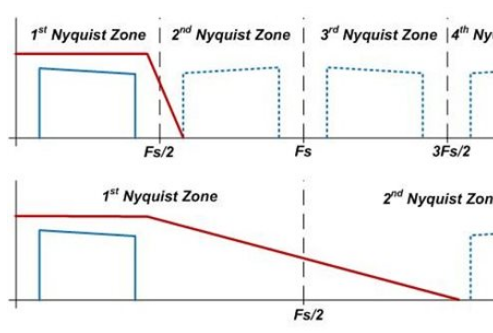

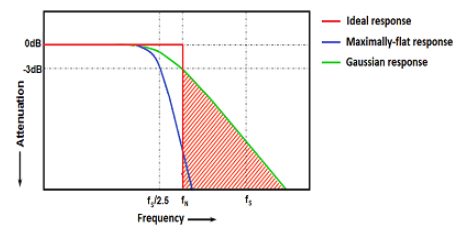

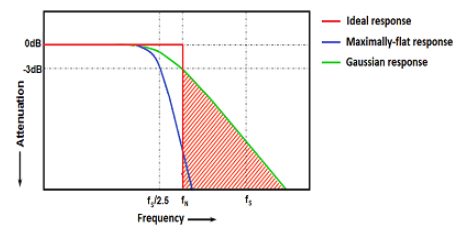

市面上的高帶寬功率分析儀往往采樣率并不高,只有帶寬的二分之一或更低。這真的合理嗎?能可靠采樣輸入信號嗎?這樣的采樣方法能支持高精度的電參數測量嗎?對比高采樣率采樣,這樣的采樣方法有什么好處?本文將解析這一現象背后的原理。

2015-08-27 10:25:42 2949

2949

實際中,信號往往是無線帶寬的,如何保證帶寬有限?所以,我們在模擬信號輸入端要加一個低通濾波器,使信號變成帶寬有限,再使用2.5~3倍的最高信號頻率進行采樣。關于此我們下面將模擬數字轉換過程將會看到。

2015-12-18 09:35:13 6374

6374

在信號鏈中運用采樣保持放大器(THA),可以從根本上擴展帶寬,使其遠遠超出 ADC 采樣帶寬,滿足苛刻高帶寬的應用的需求。本文將證明,針對 RF 市場開發的最新轉換器前增加一個 THA,便可實現超過

2018-03-01 04:44:00 10311

10311

帶寬有限(band-limited) 采樣頻率大于2倍信號最高頻率后可以無失真的恢復出原始信號。

2022-08-18 09:37:50 3521

3521 有大神知道12位ADC采樣保持器里面的電容量級是多少嗎?因為設計電路的時候要使用抗混疊濾波器,需要考慮采樣保持器電容與抗混疊濾波電容的大小關系

2023-11-02 06:27:44

信號的有效分析帶寬可以深入的解釋一下嗎

2013-11-04 20:27:00

做一個FIR數字低通濾波器,信號源是正弦信號加均勻白噪聲,顯示混疊信號和經過濾波后信號波形 以及頻譜分析,

2014-05-10 00:05:31

AD9684-500EBZ,AD9684評估板,雙通道,14位,500 MSPS ADC。該器件具有片上緩沖器和采樣保持電路,專為低功耗,小尺寸和易用性而設計。該產品設計用于采樣寬帶寬模擬信號

2020-03-05 06:46:33

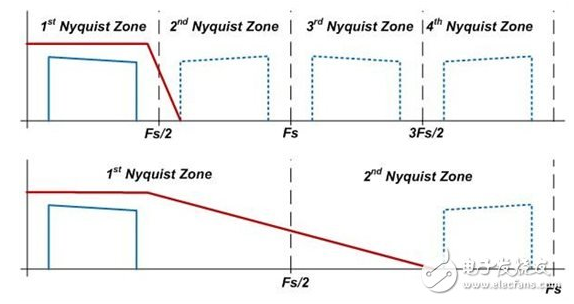

文章將會詳細地探討這個話題。)如果不滿足這個條件,那么子頻譜就會重疊,原始頻譜就會改變,即使再強的低通濾波也不能恢復原始信號。 混疊 子頻譜重疊是當我們使用低于奈奎斯特速率的采樣頻率時,信息被破壞而

2020-09-02 17:42:04

將突出為CTSD ADC的性能指標。主要亮點:過采樣提供內在的抗混疊能力,因為諧波落在CTSD帶寬之外。失真產物要混疊回通帶,其高頻分量必須遠超Fs/2。CTSD架構使用阻性輸入,其比開關電容輸入更

2018-10-31 10:48:38

閱讀手冊,AD7606內部有一個抗混疊濾波器,在-5~+5V范圍下的-3db帶寬為15khz,在-10~10V范圍內-3db帶寬是22KHZ,下降沿大約在10khz左右開始。

我的回波信號

2023-12-18 06:22:57

字域內復制原始信號,ADC必須至少以輸入信號最高頻率分量的兩倍對輸入信號進行采樣—否則的話,會產生混疊。所需的最小采樣率被稱為那奎斯特速率。或者反過來看,ADC能夠準確轉換的最高頻信號為采樣率的一半,這

2018-09-06 16:00:00

100dBFS(滿量程)的神奇屏障,用戶面臨的真正挑戰體現在為要數字化的信號設計模擬調理電路,以及相關抗混疊濾波器的設計兩個方面。在過去的二十年中,采樣速率和濾波技術已經有了很大的發展,現在我們可以結合

2021-08-04 07:00:00

性能, 采用三階巴特沃斯濾波器和低噪聲超寬帶寬差分放大器ADL5565 設計出用于高頻信號直接采樣系統中的抗混疊濾波器。

為了抵消三階巴特沃斯濾波器插入損耗, 需對流過濾波器信號放大。在本系統中使

2023-11-23 06:01:47

HiADS1675 ,內部有2種濾波器 ,delta-sigma (ΔΣ) 是用做抗混疊濾波器嗎?或者還用作其他? 有沒有相關的詳細文章介紹?

2019-05-22 06:17:18

喜 我有幾個問題。 1. Acc的順序抗混疊濾波器是什么? 2.陀螺的順序抗混疊濾波器是什么? 3.如果截止頻率高于nyquist頻率,DLPF1濾波器如何幫助我? 謝謝, 阿米爾

2018-09-11 16:41:19

DSP的ADC前端除了有抗混疊濾波器還有什么??

2012-10-14 21:02:50

我正在嘗試使用我的80GSa / s示波器(DSO-X 90164A)模擬5GSa / s數字化儀采樣率的混疊效應。我想知道示波器如何實現從16GHz到4GHz的模擬帶寬減少?我想知道在哪里可以找到

2018-10-24 11:28:42

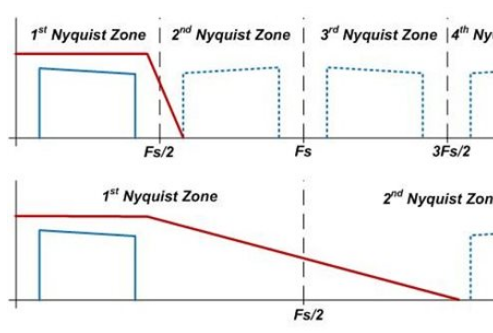

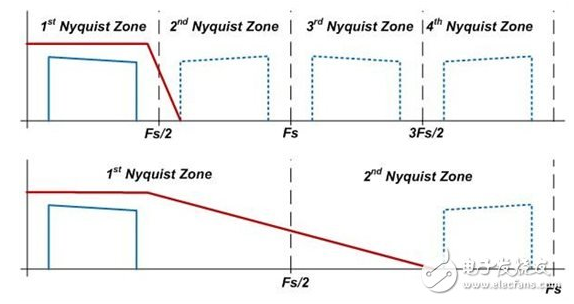

高的情況而言,利用RF采樣轉換器的高采樣速率能力仍存在一大優勢。 采樣定理規定,采樣速率必須至少是信號最大帶寬的兩倍。低于該速率的采樣被稱為欠采樣,會引起混疊現象;筆者的上一篇博客討論了這種方法的好處

2018-09-06 14:58:46

各位好!想請教如下問題:在資料中,看到說△-∑型ADC采用過采樣技術,因此大部分情況下可以用一個簡單地RC低通濾波器來進行抗混疊濾波。我想請教的是:用RC低通濾波的話,轉折頻率是可以滿足,但是RC

2019-05-17 13:30:09

,RSP1分析帶寬偏窄,因此在FFT頻譜中出現混疊。如果希望匹配,方法為:在IQ輸出到FFT采樣輸入之間增加低通濾波環節。但是不適合對風扇轉速的測量。方案考慮1. 提高FFT采樣速率,減少FFT分析

2016-03-17 12:33:15

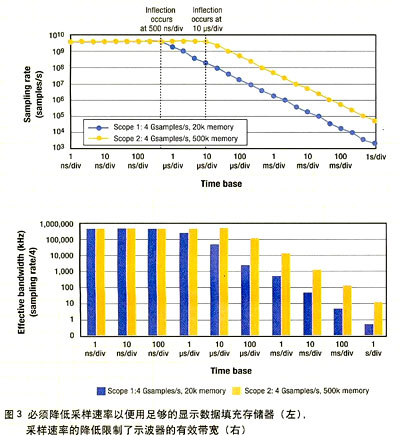

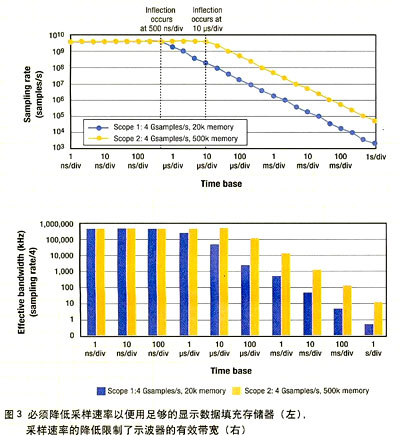

數字示波器(DSO)與模擬示波器相比有許多明顯的優勢。數字示波器可以采樣、數字化和存儲波形,幫助你測量、分析和存檔信號。但采樣過程隨之也會帶來諸多問題。混疊、同步采樣和插值器錯誤會讓你錯誤理解測量

2019-03-20 15:54:52

頻率時,可能在輸出端發生混疊。由于使用采樣系統,故這是所有斬波器和斬波穩定結構的固有限制。斬波器穩定的結構得益于具有前饋路徑,如圖2框圖的上信號路徑所示,這是一種將增益帶寬擴展到采樣頻率之外的高速信號

2020-01-08 07:00:00

你好!有沒有人知道什么會對UART發送的信號產生混疊效應?

2019-09-30 06:00:58

導致混疊現象。大多數應用都要求避免混疊,混疊問題的嚴重程度與這些混疊頻率分量的相對強度有關。 采樣頻率必須大于被采樣信號帶寬的兩倍,另外一種等同的說法是奈奎斯特定律必須大于被采樣信號的帶寬。如果信號

2019-12-19 15:44:20

一般在ADC前端都會加抗混疊濾波器。但是,如果不加抗混疊濾波器的話,ADC采集到的信號頻譜是不是由無限寬的頻譜疊加得到的?比如我拿一個50MHz的ADC采集空中信號,是不是3GHz的信號也會混疊到我采集到的信號中?希望有大神能解答一下,謝謝啦~

2016-11-17 15:22:15

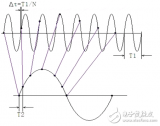

產生混疊的來源:這一點在奈奎斯特定理中給出了說明。奈奎斯特定理指出:時間連續信號轉換成離散信號時,需要在一個周期內的采樣次數多于2次。如果采樣次數不夠,將無法恢復丟失的信息。從圖1可以更清晰地看到

2019-01-02 19:03:43

專家您好:

? ? ? ?我使用的是DM368+TVP5158,采集4路D1,NTSC,分辨率720*576,(或720*480),采集到的靜態圖像正常,但是當畫面有移動物體時,換面產生錯誤和混疊,在編碼前的YUV422的數據幀就有此現象。

2018-05-31 07:58:34

LTC1569簡介LTC1569的引腳功能LTC1569的工作模式利用LTC1569實現抗混疊濾波應用LTC1569設計低通濾波器的注意事項

2021-04-07 06:33:38

如何利用奈奎斯特定理去分析頻率混疊現象?

2021-05-10 07:00:54

原來的信號。可見示波器采樣率高低對波形構建的真實性有直接的影響。采樣率低會對波形產生的影響如下:1.波形失真;2.波形混疊;3.波形漏失;通過以上圖示可以看出采樣率低會對測試結果影響非常大,那么如何選擇

2020-02-12 14:26:05

AFAIK IIS2DH 沒有模擬抗混疊濾波器。如果我使用低 ODR 設置并且輸入信號頻率高于 ODR/2,是否會出現混疊?因為在我們的測試中,我們經常在信號輸出信號中出現尖峰。如果是這種情況,我們只能提高采樣率嗎?

2022-12-16 06:38:27

我想用AD9467進行射頻信號的欠采樣處理,如何設計前端的調理電路來保證其抗混疊和阻抗匹配呢?前端射頻信號是500MHz±5MHz的信號,經過500±6MHz的帶通濾波器和射頻放大器對信號進行濾波

2023-12-11 06:14:17

在我的上一篇文章中,我討論了增量-累加模數轉換器 (ADC) 的2個重要特點。這2個特點簡化了抗混疊濾波器的設計:一個過采樣架構和一個補充數字抽取濾波器。這個過采樣架構將那奎斯特頻率放置在遠離信號

2018-09-05 14:52:59

成為帶寬限制。這是抗混疊濾波器的目的。通過在采樣之前使信號通過低通濾波器,我們可以衰減指定頻率以上的頻譜內容,從而創建一個上限頻率。 由于現實生活中的濾波器不會在截止頻率以上產生無限的衰減,因此信號將不

2020-09-18 10:12:55

中有兩種方法可以實現這一點。首先是減少采集存儲器的長度。第二種是使用稀疏或抽取函數來抽取數據。降低采樣率會增加數據混疊的可能性,尤其是在捕獲富含諧波的信號時。為了限制混疊的可能性,可以以高速率對數據進行

2019-02-23 13:41:27

中有兩種方法可以實現這一點。首先是減少采集存儲器的長度。第二種是使用稀疏或抽取函數來抽取數據。降低采樣率會增加數據混疊的可能性,尤其是在捕獲富含諧波的信號時。為了限制混疊的可能性,可以以高速率對數據進行

2019-03-09 11:53:43

摘要:在數據采樣系統中,高于二分之一采樣率的頻率成分“混疊”(搬移)到有用頻帶。大多數時間,混疊是有害的副作用,所以在模/數(AD)轉換級之前,將“欠采樣”的較高頻率簡單濾除。但有時候,特意設計利

2019-07-30 06:11:02

輸入85MHZ中頻,帶寬20MHZ(起始頻率:75MHZ;截止頻率:95MHZ)的中頻信號給AD9649;想設計一個無源抗混疊濾波器;請高手給予指點!

2015-04-23 15:19:28

本文對有源抗混疊濾波電路對驅動運放的要求,進行了分析,分別從高頻參數單位增益帶寬和高速參數建立時間,壓擺率以及運放的電流驅動能力,分析了系統對驅動放大器的要求。

2021-04-07 06:09:16

高性能模式下使用 3.3kHz ODR,模擬抗混疊濾波器帶寬設置為 1.5kHz,數字濾波器設置為 ODR/2。在生成的頻譜圖中,頻率掃描信號在多次穿過 ODR/2、ODR 和 1.5*ODR 后混疊

2022-12-15 08:14:24

這一點還是很難的)。[size=1.5em][size=1.5em]低通濾波器在Nyquist采樣定理中已經提過,要滿足采樣定理必須要求信號帶寬有限,使用大于2倍的最高信號頻率采樣才能保證信號的不混疊

2018-09-14 14:38:47

零漂移精密運算放大器:測量和消除混疊以實現更精確的電流檢測

2021-01-11 06:32:48

DN16- 用于抗混疊應用的開關電容低通濾波器

2019-07-08 09:21:14

的,那么在對信號進行采樣和量化時,如果采樣率是被測信號帶寬的2倍以上,就可以完全重建或恢復出信號中承載的信息而不會產生混疊。如下圖就是采樣率不足導致的信號混疊,可以看到采集到的信號和原始信號相比,頻率

2020-08-23 16:23:05

測信號的變化快很多。那么究竟要快多少呢?數字信號處理中的奈奎斯特(Nyquist)定律說, 如果被測信號帶寬是有限的,那么在對信號進行采樣和量化時,如果采樣率是被測信號帶寬的2倍以上,就可以完全重建或

2021-02-19 14:19:21

15kHz上對模擬信號進行采樣,此時的頻率分量高達20kHz—你將最終遇到“混疊”問題,或者將上部分量折疊進入輸入信號的工作頻段(請見圖1)。這些混疊信號將增加到原始信號上,并且將無法把已混疊頻率分量

2018-09-05 15:54:06

要求信號帶寬有限,使用大于2倍的最高信號頻率采樣才能保證信號的不混疊。低通濾波器的一個考慮就是使信號帶寬有限,以便于后期的信號采樣,這個低通濾波器是硬件實現的。另一方面,實際情況中我們也只會對某個頻頻

2015-11-26 16:22:01

數字示波器(DSO)與模擬示波器相比有許多明顯的優勢。數字示波器可以采樣、數字化和存儲波形,幫助你測量、分析和存檔信號。但采樣過程隨之也會帶來諸多問題。混疊、同步采樣和插值器錯誤會讓你錯誤理解測量

2017-08-11 14:30:58

時,可能在輸出端發生混疊。由于使用采樣系統,故這是所有斬波器和斬波穩定結構的固有限制。 斬波器穩定的結構得益于具有前饋路徑,如圖2框圖的上信號路徑所示,這是一種將增益帶寬擴展到采樣頻率之外的高速信號

2019-09-26 08:30:00

如何利用開關電容濾波器實現抗混疊濾波?

2021-04-23 06:12:02

再設計電路時,差分信號在介入差分ADC時,需要在AINN和AINP輸入引腳前加入一階抗混疊濾波器,濾除高頻干擾,請問專家應該如何設計,或則有什么參考資料,第一次設計抗混疊濾波器!謝謝

2018-11-14 11:07:35

大家好!我看一些電能電量分析采集的文獻中提到對信號進行FFT,所以要在ADC前端設計抗混疊濾波器,以避免產生延拓頻率的噪聲。一般采樣頻率為fs時,濾波器截止頻率為fs/2。如果我不對信號進行頻譜分析

2018-10-09 16:08:19

TI生產的pipeline型的ADC常常利用采樣過程中的混疊現象,用較低的采樣率來把中頻處的信號搬移到基帶在進行處理,這樣可以降低對高速ADC的速度要求,這時在采樣前需要對模擬信號進行帶通濾波,保證

2019-02-26 08:59:33

15kHz上對模擬信號進行采樣,此時的頻率分量高達20kHz—你將最終遇到“混疊”問題,或者將上部分量折疊進入輸入信號的工作頻段(請見圖1)。這些混疊信號將增加到原始信號上,并且將無法把已混疊頻率分量與原始

2022-11-18 07:48:54

原文地址:降采樣,過采樣,欠采樣,子采樣,下采樣作者:bluepig111111降采樣:2048HZ對信號來說是過采樣了,事實上只要信號不混疊就好(滿足尼奎斯特采樣定理),所以可以對過采樣的信號作

2021-08-09 08:14:52

降采樣:2048HZ對信號來說是過采樣了,事實上只要信號不混疊就好(滿足尼奎斯特采樣定理),所以可以對過采樣的信號作抽取,即是所謂的“降采樣”。“采樣頻率從2048HZ到32HZ每隔64個樣本

2021-08-17 06:10:37

高帶寬功率分析儀采樣率不高,能靠采樣輸入信號嗎?這樣的采樣方法能支持高精度的電參數測量嗎?對比高采樣率采樣,這樣的采樣方法有什么好處?

2021-04-29 06:18:29

高精度SAR模數轉換器的抗混疊濾波考慮因素

2021-01-11 07:53:43

采樣率對示波器帶寬的影響

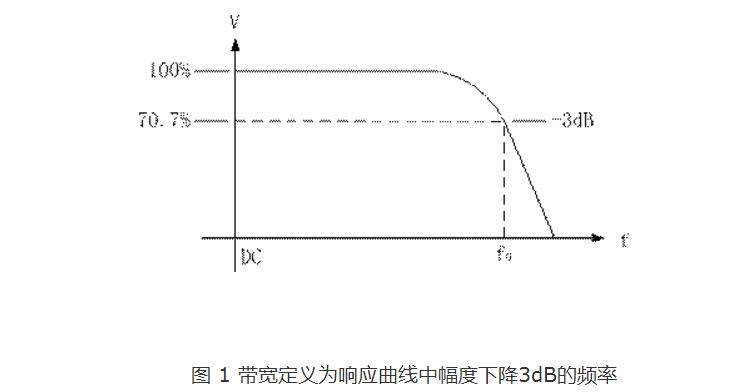

在針對某個測量需求而選擇示波器時,我們首先考慮的第一件事就是需要多大的帶寬才能精確地重建我們的信號。畢竟

2009-08-25 00:04:44 1925

1925

射頻采樣架構為傳統超級外差架構提供了替代方案。射頻采樣模數轉換器(ADC)以高采樣率工作,將射頻(RF)信號直接轉換為數字信號,由于高采樣率,射頻采樣架構支持很寬的信號帶寬。更高的信號帶寬可擴大

2017-05-03 16:15:45 23

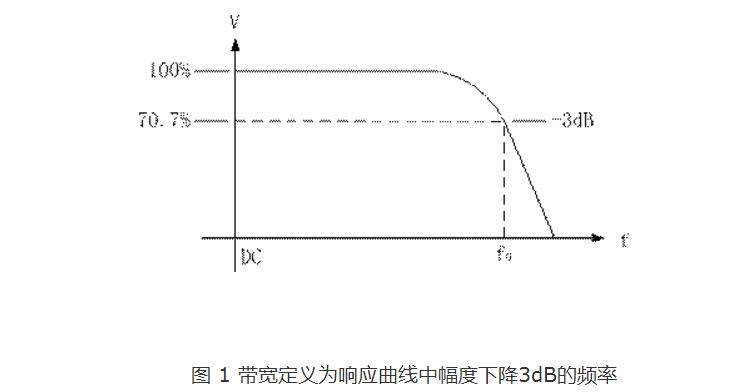

23 本文開始介紹了帶寬的定義以及示波器帶寬的含義,其次闡述了采樣率及采樣定理,最后闡述了示波器的帶寬與采樣率兩者之間的聯系。

2018-04-09 11:18:00 66858

66858

實際中,信號往往是無線帶寬的,如何保證帶寬有限?所以,我們在模擬信號輸入端要加一個低通濾波器,使信號變成帶寬有限,再使用2.5~3倍的最高信號頻率進行采樣。關于此我們下面將模擬數字轉換過程將會看到。

2019-10-23 15:54:11 1765

1765 實際中,信號往往是無線帶寬的,如何保證帶寬有限?所以,我們在模擬信號輸入端要加一個低通濾波器,使信號變成帶寬有限,再使用2.5~3倍的最高信號頻率進行采樣。關于此我們下面將模擬數字轉換過程將會看到。

2019-11-05 15:25:18 2496

2496 RF采樣轉換器可捕獲高頻信號和大帶寬信號;但是,并非每種應用都能利用需要極高速采樣的信號。

2019-12-18 16:39:47 726

726 RF采樣轉換器可捕獲高頻信號和大帶寬信號;但是,并非每種應用都能利用需要極高速采樣的信號。

2020-02-27 15:30:29 758

758

由于有限的輸入帶寬,除非您將采樣率設置得非常低,否則ADC的帶寬通常小于奈奎斯特頻率。

2021-01-14 14:35:45 19331

19331

若想分析5G NR和其他未來無線標準寬帶信號,高分析帶寬至關重要。為了能以有限的預算滿足這種測試需求,羅德與施瓦茨公司(Rohde & Schwarz)為中端信號和頻譜分析儀R&S FSVA3000新增優異的1 GHz內部分析帶寬。

2020-11-19 11:47:44 1914

1914 帶寬有限(band-limited) 采樣頻率大于2倍信號最高頻率后可以無失真的恢復出原始信號。

2022-02-11 14:08:07 2793

2793

射頻接收系統通常使用數字信號處理算法進行信號解調和分析,因此需要使用ADC對信號進行采樣。根據采樣頻率的不同,可以分為射頻直接采樣、中頻采樣、IQ采樣。射頻采樣和中頻采樣只需要一路ADC,采樣結果

2022-07-28 09:05:47 2628

2628 Nyquist采樣定理 盡管大家都知道,但還是提一提大牛奧本海姆的《信號與系統》,來捋一捋幾個點: 帶寬有限(band-limited) 采樣頻率大于2倍信號最高頻率后可以無失真的恢復出原始信號

2023-06-04 10:55:02 347

347

使用ADC時需要重點關注的參數。采樣率和帶寬之間的關系是非常重要的,下面將詳細分析采樣率和帶寬之間的關系。 一、 ADC采樣率和帶寬的定義 首先,我們需要了解ADC采樣率和帶寬的定義。采樣率是指ADC每秒鐘可以采集并轉換模擬信號的次數。例如,如果ADC的采樣率為10kHz,則每秒可以將模

2023-09-12 10:51:12 6012

6012

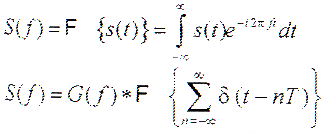

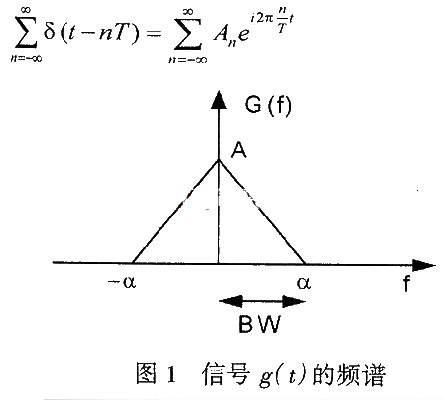

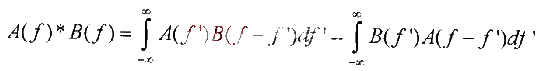

根據以上結果,再重新考慮被采樣的基頻信號,它的傅立葉變換為:

根據以上結果,再重新考慮被采樣的基頻信號,它的傅立葉變換為:

則S(f)可改寫為:

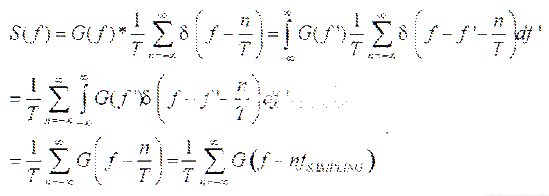

則S(f)可改寫為:  上式就是我們常說的采樣定律。它表明在時域里按周期T采樣得到的信號會以1/T 的頻率重復原始信號的頻譜,如圖2所示。

上式就是我們常說的采樣定律。它表明在時域里按周期T采樣得到的信號會以1/T 的頻率重復原始信號的頻譜,如圖2所示。  為保留所有原始信號的信息,必須保證每一個重復頻譜之間不發生混疊。否則,就不可能從采樣信號中恢復出原始信號。混疊意味著高頻段掩蓋了低頻段信號,如圖3所示。為避免混疊,必須滿足以下條件:1/T≥2α或1/T≥2BW。也可用采樣頻率表示為: fSAMPLING≥2BW 以上表明不會產生混疊的最小采樣頻率是2BW。這就是奈奎斯特采樣定律。

為保留所有原始信號的信息,必須保證每一個重復頻譜之間不發生混疊。否則,就不可能從采樣信號中恢復出原始信號。混疊意味著高頻段掩蓋了低頻段信號,如圖3所示。為避免混疊,必須滿足以下條件:1/T≥2α或1/T≥2BW。也可用采樣頻率表示為: fSAMPLING≥2BW 以上表明不會產生混疊的最小采樣頻率是2BW。這就是奈奎斯特采樣定律。

還要注意的是對有限帶寬信號的假設。從數學上分析,一個信號不可能是真正有限帶寬的。傅立葉變換定律告訴我們,如果一個信號在時域是有限的,則它的頻譜就會擴展到無窮大,如果它的帶寬是有限的,則它在時域上就是無限的。很顯然,我們找不到一個具有無窮大周期的時域信號,所以也不可能有真正的有限帶寬信號。不過絕大部分實際信號的頻譜能量都集中在有限帶寬中,因此前面的分析對這些信號仍然有效。采樣正弦信號可以非常簡單和方便地檢測出采樣頻率是否偏低,因為混疊現象是采樣頻率偏低所特有的現象。正弦信號的頻譜里的(沖激串函數)尖峰只在相應的頻率點出現,出現混疊時,尖峰會移到另一個頻率點,這一點對應著混疊信號。 以下測試結果是用Maxim公司最新推出的125Msps、12位ADC:MAX19541測試得出的。圖6是它的輸出信號頻譜,對應的輸入信號頻率fIN=11.5284MHz。很明顯,最高的尖峰恰好出現在該頻率點上。頻譜圖里還有其他一些較小的尖峰,它們是由ADC的非線性引起的諧波造成的,和本文的討論主題無關。由于采樣頻率fSAMPLE = 125MHz,遠遠大于奈奎斯特定律要求的輸入信號頻率的2倍,因此沒有混疊現象。如果將輸入頻率提高到fIN = 183.4856MHz,大于fSAMPLE/2,此時應該會有混疊出現。圖7是fIN>fSAMPLE/2時的輸出頻譜圖,主尖峰落在58.48MHz處,這就是混疊信號。也就是說,在58.48MHz出現了一個原始信號不包含的信號。在圖6和圖7中都只給出了奈奎斯特頻率以下的頻譜,因為頻譜是周期性的,圖中的顯示部分已經包含了所有必要信息。 圖6和圖7

還要注意的是對有限帶寬信號的假設。從數學上分析,一個信號不可能是真正有限帶寬的。傅立葉變換定律告訴我們,如果一個信號在時域是有限的,則它的頻譜就會擴展到無窮大,如果它的帶寬是有限的,則它在時域上就是無限的。很顯然,我們找不到一個具有無窮大周期的時域信號,所以也不可能有真正的有限帶寬信號。不過絕大部分實際信號的頻譜能量都集中在有限帶寬中,因此前面的分析對這些信號仍然有效。采樣正弦信號可以非常簡單和方便地檢測出采樣頻率是否偏低,因為混疊現象是采樣頻率偏低所特有的現象。正弦信號的頻譜里的(沖激串函數)尖峰只在相應的頻率點出現,出現混疊時,尖峰會移到另一個頻率點,這一點對應著混疊信號。 以下測試結果是用Maxim公司最新推出的125Msps、12位ADC:MAX19541測試得出的。圖6是它的輸出信號頻譜,對應的輸入信號頻率fIN=11.5284MHz。很明顯,最高的尖峰恰好出現在該頻率點上。頻譜圖里還有其他一些較小的尖峰,它們是由ADC的非線性引起的諧波造成的,和本文的討論主題無關。由于采樣頻率fSAMPLE = 125MHz,遠遠大于奈奎斯特定律要求的輸入信號頻率的2倍,因此沒有混疊現象。如果將輸入頻率提高到fIN = 183.4856MHz,大于fSAMPLE/2,此時應該會有混疊出現。圖7是fIN>fSAMPLE/2時的輸出頻譜圖,主尖峰落在58.48MHz處,這就是混疊信號。也就是說,在58.48MHz出現了一個原始信號不包含的信號。在圖6和圖7中都只給出了奈奎斯特頻率以下的頻譜,因為頻譜是周期性的,圖中的顯示部分已經包含了所有必要信息。 圖6和圖7 電子發燒友App

電子發燒友App

評論