1 概述

時分復用是當前同步通信系統中用以提高數據傳輸效率的常用方法。例如第2代移動通信GSM系統,光同步傳輸網SDH等都是使用時分復用的例子。在現代通信設備的研發中,常常會遇到高速背板通信、多協議接口、網絡管理信令通道等需要同時處理多個同步通信接口數據的情況。本文介紹了一種采用MPC8280處理器芯片內部的多通道通信控制單元,來處理多個同步通信接口數據的方法。

MPC8280是飛思卡爾公司PowerQUICC II產品線的較新成員。它采用0.13 μm工藝制造。內核、I/O的供電電壓分別為1.5 V、3.3 V。MPC8280相比該公司的MPC8260,制造工藝和工作頻率均有所提升,但因為核心電壓下降,功耗反而下降。而且,MPC8280片內的DPRAM(雙口靜態存儲器)容量增加了一倍,此外還增加了PCI和USB。

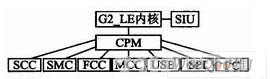

MPC8280芯片由主內核、SIU、CPM等3個主要功能模塊組成,如圖1所示。MPC8280的處理器主內核稱為G2_LE,它是一種PowerPC架構的多級流水線超標量處理器。MPC8280內核運行頻率為16*50 MHz。SIU模塊主要負責60x總線控制、PCI橋及時鐘產生。CPM模塊負責處理通信事務,即處理SCC、SMC、FCC、MCC、USB、SPI、I2C等通信控制單元收發數據。本文所述的多通道HDLC控制器即采用CPM下的MCC(多通道控制器)通信控制單元來實現。

?

MPC8280片內集成的靜態存儲器包括DPRAM、全局配置寄存器、SI RAM(串行接口路由表配置空間)。其中,第1塊32 KB的數據DPRAM空間被等分成16個bank(存儲空間塊)。CPM中的通信控制單元除了使用全局配置寄存器進行最基本的參數配置外,還須使用參數配置存儲區塊進一步配置。一般CPM中每個通信控制單元都有2個參數配置存儲區塊,參數配置存儲區塊均定位在DPRAM中的指定地址。SI RAM主要用于配置TSA(時隙分配器)的路由表。

2 SI(TSA)的設計

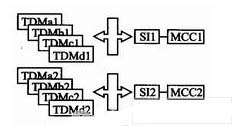

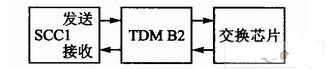

MCC總是和SI(串行接口)配合使用(因為MCC只是數據處理單元,不負責通信數據與MPC8280引腳的交互),因此,只有SI配置好,MCC單元才能正常工作。每個MCC僅與1個SI相關聯,而且,MCC1只允許連接到SI1,MCC2只允許連接到SI2。

MPC8280片內含2個SI,每個SI最多可控制4個TDM(時分復用)口。每個TDM口均擁有各自獨立的收發幀同步脈沖、收發時鐘引腳。時鐘的同步邊沿、時鐘倍頻(1×或2×時鐘模式)、幀同步信號的超前時鐘位數可編程控制。SI與MCC的關系如圖2所示。

?

圖2 SI與MCC的關系

TSA的主要工作是數據選路,即將CPM內各個通信控制單元的I/O數據以比特或字節為單位輸送到TDM口上。換句話說,TSA相當于MPC8280的CPM模塊中各通信控制單元(MCC、SCC、SMC、FCC等)進行TDMA(時分復用)的功能模塊,對TSA的編程與后端的通信控制單元無關。TSA根據由SI RAM構造的路由表執行選路。

SI自身沒有緩存,它直接與后端各通信控制單元的FIFO相連;SI在時鐘的驅動下,按照路由表的配置,將接收到的幀比特流分別送到各指定通信控制單元的FIFO中,以及將各指定通信控制單元的FIFO中的數據輸出到TDM口的引腳上,并與各通信控制單元的BD(緩沖區描述符)表和中斷交互,完成通信任務。

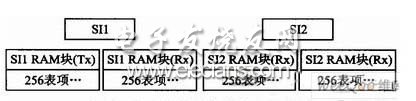

程序員通過對SI RAM塊編程來完成路由表的構建。每個SI包含2個SI RAM塊,分別用于設計發送和接收的路由表,這樣MPC8280內部的2個SI模塊總共包含4個SI RAM塊。每塊由SI RAM構造的路由表包括256條表項,每條表項長度是2字節,每條表項最多可控制8個字節串行流數據的分配,所以1個SI模塊支持的最長一幀的長度可達256×8×8=16 384比特。路由表表項的內容就是指定將TDM口上通過1~8個比特或字節的同步數據流分配給MCC、SCC、SMC、FCC等通信控制單元。最后一條表項必須激活路由表的結束標記,告訴TSA已處理完一幀,請等待下一個幀同步信號的到來。

如圖3所示,每塊SI RAM(內含256條表項)等分為4個bank,即每個TDM口均各有1個bank一一對應;每個bank可以被程序員指派為對應不同的TDM口(但不允許將兩個TDM口對應到同一個bank上)。這樣,TDM口的串行數據流在指定bank的SI RAM表項的控制下被分別送往指定的通信控制單元進行處理。一個bank的長度可由設計人員自由設定(路由表有首尾標志),這是因為不同的應用,每一幀的比特數目并不一定相同;路由表即精確地確定了每一個TDM口幀流的比特數目。顯然,一個幀流必須由多少條表項來處理也可以計算出來,即幀流總比特數/每表項處理的比特數。注意,路由表的表項數目必須是偶數,因此在編程時,如果的確是只有一條表項,那么就還必須再補上一條內容為空的表項。

?

圖3 SI RAM塊的組成與對應結構

此外,因為TDM口的接收、發送分別由2個SI RAM塊實施控制,所以TDM口發送和接收的比特流的分配可以任意設計,甚至允許將不連續的比特流都分配到一個通信控制單元,也允許一個通信控制單元從某一個TDM接收,而從另一個TDM發送。

3 MCC的標準通道設計

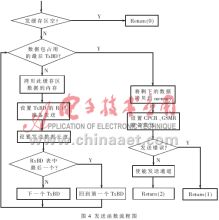

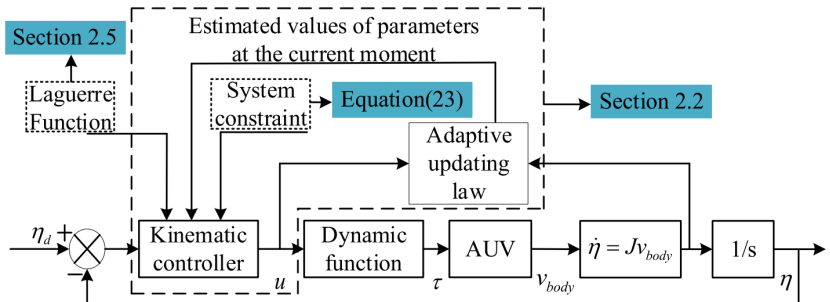

一個MCC的數據是在特定SI控制的4個TDM口上傳輸;每個MCC可以支持128條時分復用通道(見圖4),用來傳輸HDLC、透明通道,或7號信令通道數據。本文的設計是用MCC實現多通道HDLC通信協議。MCC的數據流可通過TSA的橋接直接送入MCC相應通道的FIFO處理。每個MCC可分解成4個子模塊,每個子模塊(包含32條通道)對應到1個TDM口上,即處理不同的物理TDM口的數據。MCC中的每個通道的工作模式均可獨立設置,收發關系也可以獨立映射;支持全局環回和基于單個通道的獨立環回。

?

圖4 TDM口與MCC通道的對應關系

每個MCC中包含128個功能完全相同的通道,每個通道都有一套配置寄存器,這些寄存器功能相同,并依靠通道號進行索引尋址,進而初始化。

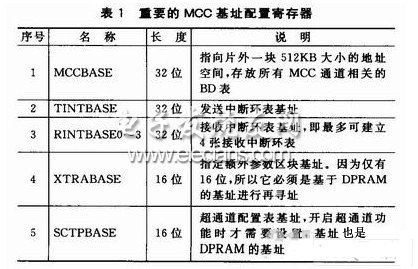

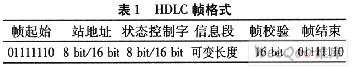

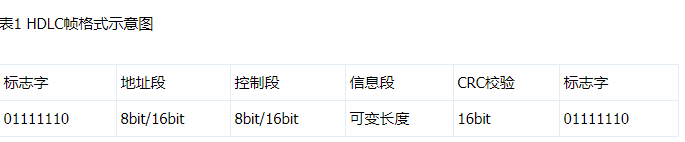

MCC的初始化遵循先全局、后通道的順序。MCC的全局參數寄存器定位在DPRAM(bank 9)中,占用128字節,該寄存器組相對DPRAM基地址的偏移量為0x8800。在全局參數設置里比較重要的、將影響各通道配置寄存器空間尋址的地址索引寄存器如表1所列。

每個通道都有64字節的專用參數寄存器。采用“DPRAM基址+64×通道號”的方式計算出指定通道的專用參數寄存器組的基址。

每個通道還有8字節的額外參數寄存器,采用“DPRAM基址+8×通道號”的方式計算出指定通道的額外參數寄存器組的基址。該區塊的主要內容包括:TBASE(16位,發送BD表首地址計算元素);RBASE(16位,接收BD表首地址計算元素)。

BD表通常放在片外內存中。1個MCC包含128條通道,每條通道都有自己的BD表,所有128條通道的BD表集中連續地存放在一個512 KB的段中。在這個空間內尋址某個通道對應的BD表的基地址的計算方法是:MCCBASE+8×RBASE(接收),MCCBASE+8×TBASE(發送)。接收和發送BD表都是一個環形隊形,接收BD表至少須含2條表項,發送BD表至少須含1條表項。編程時,構造結構數組,可以把TBASE、RBASE設計成和通道號對應的數組索引。

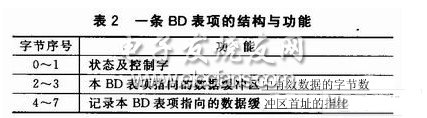

每條BD表項有8個字節,如表2所列。

環形隊列結構的中斷表也是放在片外內存中。發送中斷對應一張表,基地址為TINTBASE;接收中斷對應1~4張表,基地址分別為RINT-BASE0~RINTBASE3。中斷表的長度完全由用戶確定,但最少至少包括2條表項。每條中斷表項長度為4字節,記錄了中斷表項是否有效、中斷標志以及觸發中斷的通道號。

4 MCC的超通道模式設計

工作于超通道模式下的MCC要求SI必須以字節為選路單位。通過“超通道”這個技術將原來分屬于幾個通道的FIFO聚合成1個更大的FIF-O,傳輸大容量的同步數據流。聚合的方法是在SI RAM中指定某幾個MCCchannel的通道號屬于一個超通道,也就是說,為使MCC工作在超通道模式下,必須完成SI RAM和超通道表的初始化。

超通道表用于表示哪幾個通道的FIFO共享指定通道的控制參數。例如:160、161、162等3個標準通道組成1個超通道,且由160號通道的控制寄存器來控制該超通道的行為,那么就在超通道表表項中填入“160”。

超通道表僅用于發送控制,而接收不需要構造超通道表。接收的編程比較簡單,既不需要設超通道,也比較直接,需要由某個通道處理的數據,直接在SI RAM里打開相應的通道接收即可。

5 中斷模型

MCC的中斷響應采用兩級中斷模型:第一級為全局中斷狀態標志寄存器MCCE,第二級為中斷環表。MPC8280*有5個中斷環表為MCC通道中斷提供中斷標志服務:1個用于發送,4個用于接收。中斷環表是所有通道共用的。每個通道初始化時必須指定它使用哪個接收中斷表來上報接收中斷,利用這個特性可以設計出帶優先級的中斷響應機制。

注意:因為是環表,所以環表內最后一條表項的Wrap位必須置1,環表內的其他表項必須全部置成O。

每當有MCC通道觸發中斷,MPC8280的CPM模塊將會向中斷環表中當前空表項位置寫入一條表項,并將該表項的“V”有效標志位置1,表示已經收到一次中斷,等待用戶響應和處理。并且給表項指針加1以指向下一條空表項(當指針到達環表的最后一條時,則CPM模塊自動將中斷環表的基地址的值重新裝入表項指針寄存器,使CPM下一次寫入的位置重新定位到中斷環表的頂部)。

注意:如果中斷屏蔽寄存器INTMSK中設置了一些屏蔽事件,則當這些事件發生時,CPM不會向中斷環表寫入表項,自然也不會觸發全局中斷狀態標志寄存器MCCE。

用戶ISR代碼響應MCC中斷,訪問中斷環表表項時,應首先清除“V”標志,然后再處理具體中斷請求,并在退出中斷服務程序前清除MCCE寄存器的中斷標志。程序員應該根據系統的實際情況決定是在進入MCC中斷服務程序后將所有中斷環表中的中斷事件處理完才退出,還是僅處理中斷環表一項中斷請求后即退出中斷服務程序,這需要程序員基于中斷響應時間以及不影響其他程序代碼運行作綜合考慮。

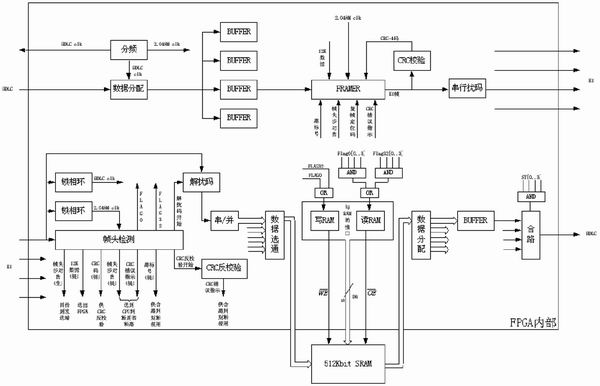

6 實際調試

環回測試是測試通信硬件本身是否正常的重要手段。MPC8280各通信處理單元自身都有環回控制位,例如,SCCHDLC的環回控制在GSMR_L寄存器中設置;MCC的單個通道的環回控制在SI RAM里設置。單個TDM口也可以自環,在SIxMR寄存器里設置。因此,可以通過對MCC的單個通道的自環,以及單個TDM口的自環來測試驅動程序寫得是否正確。在這個測試中,MPC8280的TDM口由片外時鐘和幀同步脈沖驅動。注意:測試前必須先用示波器確認TDM口引腳上的時鐘的頻率、波形符合硬件設計要求。另外應當仔細選擇MPC8280和外部交換芯片的時鐘邊緣關系,以免時鐘同步異常導致數據判決出錯。

初始化代碼完成以后,應利用shell工具或其他觀察手段檢查初始化代碼對相關寄存器的寫入符合設計目標。不要因為粗心大意寫錯了寄存器值而無法獲得正確結果。因為MCC的工作必須在SI模塊的配合下完成,可以將SI模塊和MCC分開調試。假如有已經調試完成的SCC(SMC也可以)通信單元的驅動程序,就可以將SCC的數據流從I/O腳定向到SI模塊上,如圖5所示。測試SCC經過SI模塊進行環回是否正常,可以測試SI模塊的驅動程序是否正確。測試好SI模塊的驅動程序后,再將SCC的驅動程序替換成MCC的驅動程序,即可比較容易地采用相同的模型對MCC驅動程序進行測試了。注意MCC工作在標準模式和超通道模式下時對SI RAM的路由表初始化稍有不同。

?

圖5 SCC1經過SI模塊進行環回測試

7 小結

MPC8280是一種功耗低、通信處理能力強的處理器,利用MPC8280內部的多通道控制器的大通信容量通信能力,可以比較容易地設計出信令通道、數據通道、協議轉換器等應用。本文介紹了MPC8280內部的多通道控制器的通信原理及調試方法,希望對有相關應用需求的科研人員有所幫助。

電子發燒友App

電子發燒友App

評論