VIRTEX-5 - DC and Switching Characteristics - Xilinx, Inc

2022-11-04 17:22:44

嗨, 我使用LUT在Virtex-5 FPGA中編寫用于環(huán)形振蕩器的代碼(不涉及順序邏輯)。我將環(huán)形振蕩器輸出直接連接到FPGA輸出LED引腳,觀察振蕩器上LED的波形。我觀察到環(huán)形振蕩器的波形是純

2019-04-02 13:21:08

Virtex-5 OpenSPARK快速入門手冊下載區(qū)http://www.winanycom.com/html/support/download.shtml[此貼子已經(jīng)被作者于2010-2-24 9:54:38編輯過]

2010-02-24 09:50:47

Virtex-5 SXT系列中正常工作?我還仔細檢查了我的引腳,結果發(fā)現(xiàn)我沒有將Bank0 RSVD線連接到GND。這會導致問題嗎?

2020-06-03 12:00:54

嗨,我一直在Virtex-5上使用系統(tǒng)監(jiān)視器一段時間,我只是想知道系統(tǒng)監(jiān)視器本身的功耗是多少?我試圖將它與一些基于RO的功率測量方法進行比較,所以如果有人知道實際的統(tǒng)計數(shù)據(jù)將是一個很大的幫助。謝謝,HX

2020-07-08 07:36:41

大家好,我正在研究包括3個不同時鐘域的設計。我已經(jīng)閱讀了這個帖子,我發(fā)現(xiàn)與virtex-II和virtex-4相比,virtex-5在MTBF中是最差的。對于較低和實用的MTBF,我沒有在同步器鏈

2020-06-12 09:27:03

Virtex5無法正確讀取XCF32P。 Impact可以編程到PROM和VIRTEX5,但是當Virtex5上電時,看起來PROM只在D0上輸出串行數(shù)據(jù),D1..D7為高電平(3.3V

2020-05-27 13:35:05

如題,求virtex-5 XF5VLX330的電源配置解決方案

2013-01-06 17:04:00

喜 我正在使用xcv5sx95t,我正在使用一個時鐘速度為150mhz的qdr ram作為我的記憶,這個界面我想從外部給一個150 mhz的時鐘到virtex-5,以便與其他設備正確同步(而不是

2020-06-03 14:24:38

嗨,我剛剛開始學習VHDL,我正在一個在FPGA上實現(xiàn)TDC的項目。我有很多問題,我在這里寫了一些。virtex-5能支持NIM信號還是TTL?我在數(shù)據(jù)表中看到我可以使用LVTTL,但我可以使用TTL嗎?提前致謝。begar。

2020-06-19 08:55:56

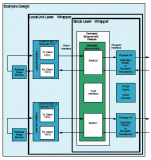

Stratix III FPGA與Xilinx Virtex-5的體系結構對比Stratix III FPGA與Xilinx Virtex-5的性能對比

2021-05-07 07:00:14

嗨,出于移植和維護的原因,我需要安裝Xilinx ISE 10.1 Foundation,完全支持所有FPGA,尤其是Virtex-5 XC5VFX70T。我有這個版本的有效許可證(即注冊ID)但我

2018-11-15 11:30:24

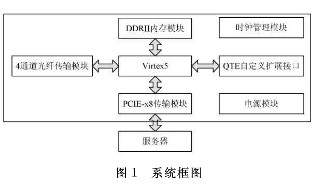

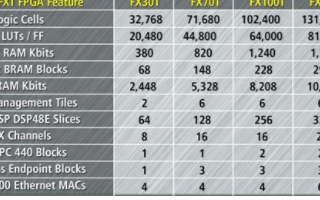

關于Virtex-5 FXT平臺的知識點看完你就懂了

2021-05-06 06:48:57

各位前輩好!我在用Xilinx Virtex5 FPGA做通過千兆網(wǎng)和上位機通信,有幾個問題想請教:1、tri-mode ethernet mac 和 virtex-5 embedded

2016-05-31 22:41:53

嗨,我可以在Virtex-5的任何片中實現(xiàn)CFGLUT5原語,還是僅限于SLICE_M中的LUT?謝謝,Hooman

2020-05-28 06:32:38

使用xilinx xps-edk 12.4和virtex-5板(xupv5-lx110t).................!感謝致敬....................以上來自于谷歌翻譯以下為原文

2019-02-28 13:38:14

我有兩張標有“Vivado Design Suite 2013.2”和“ISE Design Suite 14.6”的光盤,我之前在Virtex-5設計上使用過Win7。最近將操作系統(tǒng)

2018-12-29 13:53:01

沒有使用啟動mig,任何人都可以給我一個關于virtex-5中ddr2的mpmc約束的例子嗎?

2019-11-07 09:50:13

在VIRTEX-5 fpga中使用LVDCI端接時,添加50歐姆電阻(VRN和VRP)的目的是什么?如果沒有連接特定的電阻會有什么影響?

2020-06-11 08:49:19

嗨,我正在開發(fā)一個項目,我們正在使用Virtex-5 FPGA從ADC捕獲信號,樣本存儲在128K x 256 SRAM上,數(shù)據(jù)樣本由PC采集。我相信Virtex-5為BRAM提供了一個選項,雖然我

2020-06-17 11:31:47

PCIe是什么?有什么核心優(yōu)勢?Xilinx的PCIe端點模塊的顯著優(yōu)勢包括哪些?基于Virtex-5 LXT FPGA的PCIe端點該怎樣去設計?

2021-05-26 06:39:11

。與星形系統(tǒng)示例類似,利用Virtex-5LXT解決方案,可以提高集成度、縮短上市時間、優(yōu)化系統(tǒng)特性、降低功耗和成本等。本文結論如今,串行背板技術已成為主流技術。隨著帶寬要求的與日俱增,將有越來越多

2019-04-12 07:00:11

/測試系統(tǒng)等。 設計“頑癥” 盡管串行技術的應用已日益普遍,但許多設計挑戰(zhàn)依然橫亙在設計人員面前。背板子系統(tǒng)是整個系統(tǒng)的“心臟”,它必須能夠在板卡間提供可靠的信號傳輸。因此,在背板設計中,確保很高

2019-04-16 07:00:07

的10GbE回程卡之間實現(xiàn)完全連接。每片板卡都利用1個Virtex-5LXT器件和4個嵌入式串行收發(fā)器來實現(xiàn)4個獨立的網(wǎng)狀結構物理層通道。這4個鏈路層基于Aurora協(xié)議,以3Gbps左右的速率傳輸

2019-04-16 07:00:05

與 ISERDES 模塊中的系統(tǒng)時鐘 (CLK0) 保持同步。讀數(shù)據(jù)通路包括兩個階段:讀數(shù)據(jù)采集和讀數(shù)據(jù)重新采集。兩個階段均在各個 Virtex-5 I/O 的內(nèi)置 ISERDES 中實現(xiàn)。途經(jīng)

2019-04-22 07:00:07

(Kintex-7),雙沿數(shù)據(jù)傳輸;1路LVDS數(shù)據(jù)的傳輸速率為1Gbps(Virtex-5)或1.2Gbps(Virtex-6)或1.4Gbps(Kintex-7),16路LVDS數(shù)據(jù)的傳輸速率為16Gbps

2014-03-01 18:47:47

嗨....我正在使用Virtex-5板來學習。我想編程到SPI Flash M25P80型號。板上有一個SPI程序頭模塊,該模塊有七個引腳:INIT,TMS,TCK,TDI,TDO,GND,VCC。我的問題是什么意思是INIT Pin?以及如何連接INIT引腳?謝謝.....

2020-06-19 07:57:21

我使用了Virtex 5系列芯片XC5VSX95T。我使用了GTP模塊,實現(xiàn)了快速IO通信,3.125Gbps。然后,出現(xiàn)了問題.FPGA可以通過Rapid IO與FPGA進行通信,通信速率高達

2020-06-19 08:53:14

大家好,我正在使用DMC為LX50T Virtex-5內(nèi)的觸發(fā)器生成時鐘。我在CLKIN和CLKO之間有一個很大的延遲,即DCM內(nèi)的Feddback延遲元件無法調整。這個器件的兩個時鐘(CLKIN

2020-06-16 14:04:42

嗨, 我使用的是Virtex-5 FPGA,DDR2 MIG,我的ISE版本是13.2。 我的phy_init_done信號沒有被斷言。我發(fā)現(xiàn)校準序列卡在階段2.階段3從未到達。請?zhí)峁┯嘘P上述原因的信息?

2020-06-15 11:52:03

如何利用Virtex-5系統(tǒng)監(jiān)控器加強系統(tǒng)管理和診斷?

2021-04-29 06:28:56

如何利用Virtex-5器件去實現(xiàn)QDR II SRAM接口?

2021-04-30 06:02:32

。依托于國家“863”計劃Gbps 無線傳輸關鍵技術與試驗系統(tǒng)研究開發(fā)項目,我們究竟該如何利用Virtex-5 FPGA設計Gbps無線通信基站?

2019-08-07 07:05:49

根據(jù)Virtex-5用戶指南:擴展LVDS提供更高的驅動能力和電壓擺幅(350-750),但如何實現(xiàn)擴展LVDS而不是通用LVDS。非常感謝。

2020-05-27 11:38:18

嗨......任何人都可以指導我如何將Virtex-5 I / O引腳用于差分對輸入???在這種情況下如何終止發(fā)射器和接收器????我必須使用Verilod HDL編寫代碼。等待回應..以上

2019-02-14 13:05:41

嗨,關于Virtex-5與具有LVDS DDR信令的并行高速ADC接口的任何應用說明。我擔心數(shù)據(jù)偏斜,因此需要靜態(tài)和動態(tài)相位對齊。最接近的appnote是xapp860,但它不使用并行源,更像

2020-06-19 06:48:36

嗨,大家好,我是Xilinx的新手,我有兼容性問題,我已經(jīng)安裝了完整許可證的ISE系統(tǒng)構建器,但我在設備列表中找不到Virtex-5。我的問題是,如果我能夠將此軟件與舊設備一起使用,如果是,那么我如何將Virtex-5板添加到設備列表中。謝謝。薩利姆。

2020-03-16 06:56:52

您好,我想將SPANSION S29GLxxxPflash連接到VIRTEX-5,以便在BPI模式下加載比特流。有沒有像xapp973,forSPANSION S29GL-P這樣的指南?或者有人有示意圖?

2020-06-01 06:27:48

我有Xilinx XUPV5-LX110T評估平臺。現(xiàn)在我需要Virtex-5 XC5VLX110T(FF1136 / FFG1136)引腳排列,但在打開此地址后:http

2019-10-25 09:17:18

大家好,我使用帶有virtex-5 xc5vsx95t的sundance板。當我嘗試構建我的設計時出現(xiàn)以下錯誤。地址:543 - 由于放置限制,無法放置以下5個組件。組件的相對偏移顯示在組件名稱旁邊

2020-05-27 16:58:18

本文在對Virtex-5 RocketIOTM GTP進行了解的基礎上,針對串行高速接口開發(fā)中位寬不匹配的問題,提出了一種位寬轉換方法,以解決Virtex-5 RocketI0TM GTP無法直接應用于某些串行高速接口開發(fā)的問題,并就SATA2.0接口開發(fā)中該問題的解決方案進行詳細闡述。

2021-05-28 06:21:43

怎樣去設計一種3.125Gbps串行傳輸系統(tǒng)?如何對3.125Gbps串行傳輸系統(tǒng)進行測試驗證?

2021-05-20 06:29:52

嗨我正在尋找兩個應用筆記-Virtex-5 SEU關鍵位信息:擴展Virtex-5 SEU控制器和新一代Virtex-5SEUController的能力,但我找不到它們。有沒有人見過他們?請幫助

2020-06-15 09:47:18

數(shù)據(jù)表中未給出virtex-5 FPGA的輸出負載電容。任何人都可以讓我知道在哪里找到它?

2020-06-19 07:02:26

親愛的專家我想知道有必要使用microblaze來使用Virtex-5以太網(wǎng)mac包裝器核心嗎?Furthr我無法獲得什么是以太網(wǎng)mac配置寄存器?等待回復!

2020-06-10 16:03:34

the sample program AN65974 on Virtex-5 board in Stream in Mode. unfortunately, it does not work

2018-11-29 11:54:09

親愛的朋友們,我正在研發(fā)Virtex-5 ML510主板。對于我的項目,我需要應用差分時鐘,這在ML510板上是不可用的。所以任何人都可以建議我使用哪個時鐘發(fā)生器,我應該買正確的工作。感謝致敬,桑杰庫馬爾

2020-06-11 15:55:35

對于XQR5VFX130空間級virtex-5 fpga,可以使用2個XQF32P完成配置。但它似乎已經(jīng)過時了。有沒有相應的?或者配置的替代方法是什么?

2020-06-19 13:58:13

Virtex-5 - 通過DRP動態(tài)重新配置DCM的地址和值是什么?我有PLL的電子表格,但沒有DCM的電子表格。

2020-06-16 16:25:11

在UG191(Virtex-5配置用戶指南,第135頁)中,它顯示“幀從左到右編號,從0開始。對于每個塊,除時鐘列外,編號為0到25的幀訪問該列的互連這是否意味著編號為26到35的幀是SRL或

2020-06-16 16:36:58

有人可以請我參考可以與ML505板上的Virtex-5一起使用的散熱器/風扇嗎? (部件號/供應商/數(shù)據(jù)表)這些是提到可以使用的“煎餅扇”的一些文件,但沒有給出部件號。ML505 / 506 SGMII設計創(chuàng)作ML505 / 506/507概述和設置

2019-08-16 10:08:54

UG190 Virtex-5 用戶指南

2008-07-28 15:46:50 65

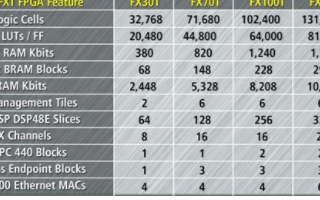

65 Xilinx公司的Virtex-5 FXT FPGA器件在業(yè)界率先集成了嵌入式PowerPC 440處理器模塊、高速RocketIO GTX收發(fā)器和專用XtremeDSP 處理能力。作為65nm Virtex-5系列的第四款平臺,Virtex-5 FXT提供了極高的

2009-11-24 11:17:22 32

32 Virtex-5, Spartan-DSP FPGAs Application Note

This application note demonstrates how efficient

2010-03-08 09:47:48 71

71 Virtex-5 Embedded Tri-Mode Ethernet Core應用手冊

This application note describes a system using

2010-05-13 13:51:18 44

44 Opal Kelly推出基于Virtex-5的USB集成模塊

?總部位于俄勒岡州波特蘭的 Opal Kelly 公司專門從事基于 FPGA 的 USB 模塊開發(fā),現(xiàn)推出了基于賽靈思 Virtex?-5 FPGA 的 USB 集成模

2010-02-08 10:11:13 1056

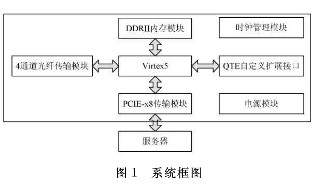

1056 引言

本文探討在Virtex-5 FPGA中實現(xiàn)設計的一些難題,然后用一個項目作為示范來詳解充分利用其功能集的

2010-11-12 09:44:40 827

827

摘要:數(shù)字融合在當今信息時代是對數(shù)字信號處理的渴求,因而需要提高數(shù)字信號處理的性能。本文介紹了數(shù)字信號處理的Virtex-5 SXT解決方案,并對三個示例進行分析。 關鍵詞:數(shù)字信號處理,數(shù)字融合,Virtex-5 SXT

2011-02-27 14:24:13 37

37 隨著帶寬要求與日俱增,串行背板技術的應用越來越多。本文介紹了利用 Xilinx Virtex-5 LXT FPGA 實現(xiàn)串行背板技術的解決方案。

2011-05-20 15:15:14 35

35 Virtex-5 FPGAs are available in -3, -2, -1 speed grades,with -3 having the highest

2011-08-04 14:32:51 30

30 Xilinx Virtex-5 SXT FPGA 平臺提供了獨特的單芯片解決方案,充分利用大規(guī)模并行計算達到超高性能,同時將功耗降到最低。

2011-08-20 15:22:35 994

994

為了解決下一代無線通信基站中多天線(MIMO)信號處理所帶來的巨大數(shù)據(jù)吞吐量要求,本文基于Virtex-5 FPGA的GTP單元給出了一種在高級電信計算架構(ATCA)機箱內(nèi)實現(xiàn)單對差分線進行3.125Gbps串

2011-08-25 10:37:12 1001

1001

由于Virtex-5 器件的基礎架構與以往的FPGA 器件不同,因此,要為特定設計選擇合適的Virtex-5 器件并非易事。大多數(shù)情況下,設計應采用類似的陣列大小(器件數(shù)量)并且比以前的目標器

2012-01-17 17:36:22 33

33 Virtex-5 器件包括基于第二代高級硅片組合模塊 (ASMBL) 列架構的多平臺 FPGA 系列。集成了為獲得最佳性能、更高集成度和更低功耗設計的若干新型架構元件,Virtex-5 器件達到了比以往更高

2012-02-17 14:39:56 51

51 xilinx virtex-5 技術參數(shù) 供芯片選型之用

2015-11-30 17:44:45 1

1 (GbE)),為設計面向計算機和數(shù)據(jù)處理市場的低成本、高性能產(chǎn)品創(chuàng)造了可能性。Xinlinx Virtex-5 現(xiàn)場可編程門陣列 (FPGA) 系列,為設計具備更強功能和更低功耗的片上系統(tǒng) (SoC) 解決方案奠定了基礎。 Virtex-5 架構具有一系列關鍵特性,能夠大大簡化 TCP 和

2017-11-06 11:17:53 2

2 提出了基于Xilinx公司Virtex-5系列FPGA中RocketIO GTP收發(fā)器設計的一個高速串行傳輸實現(xiàn)方案,詳細闡述了硬件設計要點和軟件實現(xiàn)概要,系統(tǒng)實測表明,該方案能在某信號處理系統(tǒng)兩個板卡之間穩(wěn)定地進行1.6 Gb/s的數(shù)據(jù)傳輸,誤碼率優(yōu)于10e-12,傳輸距離大于1米。

2017-11-21 10:16:00 7689

7689 本文探討在Virtex-5 FPGA中實現(xiàn)設計的一些難題,然后用一個項目作為示范來詳解充分利用其功能集的技法。設計過程包括幾個步驟,從針對應用選擇適合的Virtex-5開始。為便于本文敘述,我們假定IP模塊已經(jīng)過匯編,并且已經(jīng)就緒備用或已經(jīng)用CORE Generator生成。

2017-11-24 20:40:51 1126

1126

以太網(wǎng)是一個占據(jù)絕對優(yōu)勢的固線連接標準。Xilinx? Virtex?-5以太網(wǎng)媒體接入控制器(以太網(wǎng)MAC)模塊提供了專用的以太網(wǎng)功能,它和Virtex-5 RocketIO? GTP收發(fā)器以及

2018-07-22 09:28:00 2384

2384

該電源被設計成為Xilinx、Virtex-5、LXT和FXT平臺中的收發(fā)器提供電源。

2018-05-18 16:30:10 11

11 該電源被設計成為Xilinx、Virtex-5、LXT和FXT平臺中的收發(fā)器提供電源。

2018-05-18 16:33:58 13

13 精準的數(shù)據(jù)收發(fā)信息,更好的為工程項目服務。傳統(tǒng)的并行傳輸方式由于走線多、信號間串擾大等缺陷,無法突破自身的速度瓶頸。而串行傳輸擁有更高的傳輸速率但只需要少量的信號線,降低了板開發(fā)成本和復雜度,滿足高頻率遠距離的數(shù)據(jù)通信需求,被廣泛應用到各種高速數(shù)據(jù)通信系統(tǒng)設計中。

2019-07-12 08:04:00 1954

1954

選擇。每個平臺包含不同比例的功能,以滿足各種高級邏輯設計的需要。除了最先進、高性能的邏輯結構外,Virtex-5 FPGas還包含許多硬IP系統(tǒng)級塊,包括功能強大的36kbit塊RAM/FIFOS、第二代

2019-10-21 08:00:00 26

26 Genesys Virtex-5 FPGA開發(fā)板集成了功能強大的Xilinx Virtex?-5 FPGA,為廣大用戶帶來了一個功能強大、方便實用的設計平臺。板上還有千兆以太網(wǎng),高速內(nèi)存,高分辨率

2019-11-14 17:01:37 3832

3832

上市時間、降低風險、適應不斷演化的標準以及降低系統(tǒng)成本。 Virtex-5平臺建立在這些豐富價值的基礎上,再加上高速串行連接功能和嵌入式處理能力,從而構成了終極系統(tǒng)集成平臺。

2020-07-24 15:25:00 1172

1172

雙向各3.125Gbps的串行通信鏈路。為了驗證該系統(tǒng)的遠距離傳輸能力,將兩塊板放置在14槽ATCA機箱的物理槽位1和物理槽位14,此時總的傳輸距離大約為40英寸。

2021-05-05 16:49:00 4742

4742

Virtex-5 RocketIOTM GTP收發(fā)器的串行高速系統(tǒng)接口開發(fā)過程中位寬轉換的幾個技術問題提出了解決方案,并以SATA2.0開發(fā)為例,通過Xilinx Virtex-5 XC5VLX50T FPGA驗證方案進行了可行性驗證。

2021-06-24 16:10:42 2510

2510

基于直流和開關特性的Virtex-5 FPGA產(chǎn)品介紹

2021-07-12 14:11:09 18

18

電子發(fā)燒友App

電子發(fā)燒友App

評論