楷登電子今日正式發布Cadence? Virtuoso?定制 IC設計平臺的技術升級和擴展,進一步提高電子系統和 IC設計的生產力。新技術涉及Virtuoso 系列幾乎所有產品,旨在為系統工程師提供更穩健的設計環境和生態系統,助其實現并分析復雜芯片、封裝、電路板和系統。

2018-04-11 16:40:16 9290

9290 Cadence與MathWorks的無縫集成可以簡化數據交換過程,增強分析能力,縮短PCB設計周期。

2018-05-24 10:45:43 8187

8187 Cadence Integrity 3D-IC 平臺是業界首個全面的整體 3D-IC 設計規劃、實現和分析平臺,以全系統的視角,對芯片的性能、功耗和面積 (PPA) 進行系統驅動的優化,并對 3D-IC 應用的中介層、封裝和印刷電路板進行協同設計。

2022-05-23 17:13:53 4218

4218 這是一個業界用于打造差異化定制芯片的領先平臺,可借助生成式 AI 技術顯著提升設計生產力; Virtuoso Studio 與 Cadence 最前沿的技術和最新的底層架構集成,助力設計工

2023-04-20 15:52:13 508

508

各位大佬好,我正在學習IC設計,對于Cadence Virtuoso這個軟件有一些入門級的小問題:我從AnaglogLib拷貝NMOS管和PMOS管到自己的library下面,打開他們的CDF參數看

2017-10-16 00:26:33

Cadence設計系統公司發布了Cadence Allegro系統互連設計平臺針對印刷電路板(PCB)設計進行的全新產品和技術增強。改進后的平臺為約束驅動設計提供了重要的新功能,向IC、封裝和板

2018-11-23 17:02:55

Cadence 宣布推出其最新版Cadence? Allegro? 與 OrCAD?印刷電路(PCB) 軟件,它擁有的全新功能與特性能夠提高PCB工程師的績效與效率。Allegro與OrCAD

2018-09-10 16:37:20

本帖最后由 michael_2009 于 2011-8-5 22:27 編輯

求:Cadence SPB15.7 Allegro中文版電路板.brdConstraint詳細的設置說明?哪位高人

2011-08-03 10:47:35

Integrity 3D-IC 平臺實現更高的生產力,而不是孤立的單晶片實施方法。該平***特地提供了系統規劃、集成的電熱、靜態時序分析 (STA) 和物理驗證流程,從而實現更快、高質量的 3D 設計閉合。它還

2021-10-14 11:19:57

可以與Cadence主要的設計平臺無縫整合:可以與Encounter整合實現裸片抽象協同設計,與CadenceVirtuoso整合實現RF模塊設計,并與CadenceAllegro整合實現封裝與電路板

2008-06-27 10:24:12

Cadence設計系統公司發布Cadence?Allegro?系統互連設計平臺針對印刷電路板(PCB)設計進行的全新產品和技術增強.改進后的平臺為約束驅動設計提供了重要的新功能,向IC、封裝和板

2018-08-28 15:28:45

Cadence設計系統公司發布Cadence?Allegro?系統互連設計平臺針對印刷電路板(PCB)設計進行的全新產品和技術增強.改進后的平臺為約束驅動設計提供了重要的新功能,向IC、封裝和板

2008-06-19 09:36:24

Cadence高速電路板設計與仿真第3版,分享資料給大家.

2017-02-28 10:45:34

)。實際 Theta JC 數據會根據使用 JEDEC 印制電路板 (PCB) 測試的封裝生成。圖 3 Theta-JC 解釋 天啊,誰有這么多時間和耐性做完所有這種分析和測試——當然 JEDEC 除外

2018-09-14 16:36:06

集成電路生產流程見下圖:[img][/img]整個流程分為六個部分:單晶硅片制造,IC設計,光罩制作,IC制造,IC測試和封裝。1.IC生產流程 [單晶硅片制造] 單晶硅片是用來制造IC的,單晶硅

2019-01-02 16:28:35

cadence virtuoso教程? 1990-2006 Cadence Design Systems, Inc. All rights reserved.Printed

2012-08-10 18:37:59

/>相比Cadence 的綜合工具略為遜色然而Cadence 在仿真電路圖設計<br/>自動布局布線版圖設計及驗證等方面卻有著絕對的優勢Cadence

2008-07-12 23:11:21

關于電路板IC類封裝尺寸的匯總——電路板設計檢驗或者維修檢查參考可用

2019-02-13 10:35:28

的焊點。 電路板OSP 1、工藝流程:除油→水洗→微蝕→水洗→酸洗→純水洗→OSP→純水洗→烘干。 2、原理:在電路板銅表面上形成一層有機膜,牢固地保護著新鮮銅表面,并在高溫下也能防氧化和污染

2018-09-19 16:27:48

在PCB設計中,一般采用雙面板或多面板,每一層的功能區分都很明確。在多層結構中零件的封裝有兩種情況,一種是針式封裝,即焊點的導孔是貫穿整個電路板的;另一種是STM封裝,其焊點只限于表面層;元器件

2018-08-29 10:28:18

`請問電路板上面的ic是什么?`

2019-10-30 16:31:59

往往比單一維修一塊壞電路板還要便捷和容易。電路板檢修的一般順序 (1)首先,仔細觀察故障電路板的表面有無明顯的故障痕跡。如:有無燒焦燒裂的集成IC或其它元件,線路板是否有斷線開裂的痕跡。(2)、了解

2019-08-12 22:50:15

功能予以解決。黃金工具組合及設計流程 現在有許多EDA廠商均可以提供高速系統PCB設計的EDA工具,幫助用戶在這一領域中有效的提高設計質量,縮短設計周期。在應用電氣規則驅動方法的EDA系統板級工具中最

2018-08-24 16:48:10

《集成電路芯片封裝技術》是一本通用的集成電路芯片封裝技術通用教材,全書共分13章,內容包括:集成電路芯片封裝概述、封裝工藝流程、厚膜與薄膜技術、焊接材料、印制電路板、元件與電路板的連接、封膠材料

2012-01-13 13:59:52

`請問集成電路板上的線是什么?`

2019-10-31 16:59:25

我是一個清潔設備(洗地機、掃地機)的經銷商,這些年發現設備故障率居高不下,幾乎都是出在集成電路板上,一旦電路板出現問題,嚴重影響客戶的使用,廠家也不愿意對集成電路板進行改進,我就在想:設備控制能否

2017-05-09 11:39:43

Allegro技術建立于一種獨特的芯片-封裝-電路板協同設計方法,與來自Cadence Encounter數字實現系統和Virtuoso定制模擬產品線的流程直接雙向綜合,包括低功耗、混合信號、千兆

2020-07-06 17:50:50

Altium Designer 14電路設計與仿真從入門到精通為了讓用戶對電路設計過程有一個整體的認識和理解,下面我們介紹一下“PCB”電路板設計的總體設計流程。

2019-08-06 06:04:27

進行檢查和修正。 3、布置各零件封裝的位置 可利用系統的自動布局功能,但自動布局功能并不太完善,需要進行手工調整各零件封裝的位置。 4、進行電路板布線 電路板自動布線的前提是設置安全

2019-04-15 07:35:02

`` 本帖最后由 lzr858585 于 2021-4-1 14:31 編輯

Allegro PCB高速電路的完整設計流程,手把手教會你Cadence高速電路板設計。``

2021-04-01 14:13:00

集成電路(IC)包裝在瓷片內,瓷片的底部是排列成方形的插針,這些插針就可以插入獲焊接到電路板上對應的插座中,非常適合于需要頻繁插波的應用場合。對于同樣管腳的芯片,PGA封裝通常要比過去常見的雙列直插封裝

2019-04-13 08:00:00

內層材料層壓→孔加工→孔金屬化→指外層圖形→鍍耐腐蝕可焊金屬→去除感→光膠腐蝕→插頭鍍金→外形加工→熱熔→涂助焊劑→成品。印制電路板的功能印制電路板在電子設備中具有如下功能:提供集成電路等各種電子

2019-10-18 00:08:27

`請問印制電路板屬于集成電路產業嗎?`

2019-08-30 17:50:07

一般就是指芯片的集成,像電腦主板上的芯片,CPU內部結構,全是叫集成電路,而印刷電路板就是指大家通常見到的線路板等,也有在電路板上包裝印刷焊接芯片。集成電路(IC)是焊接在PCB板上的;PCB板

2023-06-27 14:38:24

基于Cadence virtuoso與Mentor Calibre的CMOS模擬集成電路版圖該如何去設計?怎樣去驗證一種基于Cadence virtuoso與Mentor Calibre的CMOS模擬集成電路版圖?

2021-06-22 06:12:49

的設計平臺。在綜合比較后,本文選定了CadenceVirtuoso全定制IC設計工具。VirtUOSO是Cadence公司推出的用于模擬/數字混合電路仿真和射頻電路仿真的專業軟件。基于此平臺

2018-11-26 10:56:11

之間的電氣連接通常是通過電路板橫斷面上的鍍通孔實現的。多層線路板的優缺點優點: 裝配密度高、體積小、質量輕由于裝配密度高,各組件(包括元器件)間的連線減少,因此提高了可靠性;可以增加布線層數,從而

2019-06-15 06:30:00

??在多層電路板設計中,一般內電層會有電源層、地層兩種。為了有效實現電磁屏蔽,一般令電源層面積比地層小(電源層比地層內縮)。并在內縮區域打上一圈回流地過孔。??在allegro中操作如下

2021-12-29 06:35:51

互聯汽車帶來更智能的駕駛體驗自主駕駛的互聯汽車實現無縫駕駛的智能系統

2021-03-09 06:20:45

對未知電路板的測繪所使用的常用辦法有哪幾種?未知電路板原理圖測繪系統的設計與實現

2021-04-22 06:18:37

圖布局結構,最后根據芯片內各個信號的關系來進行電路布線的操作。以上的操作都可以在Cadence的IC 5.1集成設計環境下的Virtuoso中完成,當完成布局布線后全定制Asic的版圖基本就確定了,然后

2013-01-07 17:10:35

rt,用cadence畫了完整的電路板,但是不會仿真,有賞求指導。QQ:1145275787.

2017-03-20 22:34:05

線路板、電路板、PCB抄板流程與技巧是什么

2021-04-26 06:49:33

請問 cadence中的創建電路板的向導中,有一步是要確定每一層的定義,有個地方需要打鉤,“generate negative layers for power planes”請問這個是什么意思,翻譯說為電源平面產生負層?啥叫負層啊?請高手指點。

2013-03-03 15:53:10

`請問阻抗電路板可以幫助解決哪些問題?`

2020-04-03 17:43:25

。 FDMS96xx系列的引腳輸出經仔細設計,可在PCB布局中輕易地直接連接至PWM控制器,這種創新封裝概念縮短了設計時間,并減少了電路板布局跡線的寄生電感,有助于提高總體系統效率。 FDMS96xx系列

2018-11-22 15:48:58

我司定制生產各種柔性FPC電路板,硬性PCB電路板,單層電路板,多層電路板,雙層電路板,剛柔一體電路板等。 打樣周期7天左右,批量生產周期15天內。 主要應用于手機,便攜計算機

2022-09-20 18:11:35

業務流程集成是協同管理平臺的核心技術之一。本文提出采用基于BPEL 的集成方式實現協同管理平臺與應用系統之間的業務流程集成,并設計了協同管理平臺的業務流程集成方案

2009-06-19 09:26:42 9

9 、實現方式以及其在輕便、高效與安全方面的優勢。一、設計理念FH8A150掛脖小風扇電路板的設計,始終圍繞著輕便、高效與安全這三個核心理念。在輕便方面,電路板采用了高

2024-03-11 22:40:55

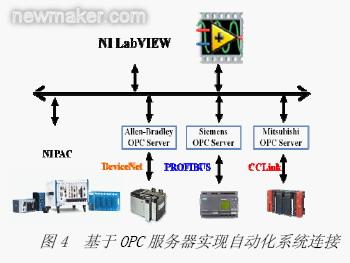

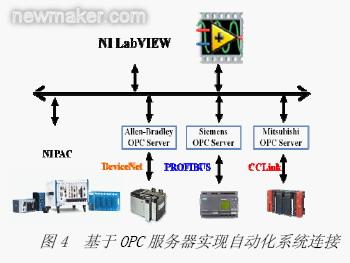

NI LabVIEW及PAC平臺與傳統自動化系統的無縫集成

現今,流程型和離散型工業生產企業正面臨全球化市場競爭下不斷增長的壓力:最大

2009-06-13 16:07:16 1625

1625

Cadence Allegro SiP and IC Packaging 16.3版推出

Cadence設計系統公司宣布,利用最新的系統封裝(SiP)和IC封裝軟件,封裝設計者將在芯片封裝協同設計過程中和整個半導體設計鏈中

2009-11-04 08:52:51 1826

1826 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ: CDNS),宣布Giantec Semiconductor Corp.已采用Cadence? Virtuoso?統一定制/模擬(IC6.1)以及Encounter?統一數字流程生產其混合信號芯片。

2011-09-27 11:06:26 1483

1483 Cadence 設計系統公司日前宣布,汽車零部件生產商Denso公司在改用了Cadence定制/模擬與數字流程之后,在低功耗混合信號IC設計方面實現了質量與效率的大幅提升。將Cadence Encounter RTL-to-G

2012-09-04 09:31:59 811

811 Cadence教程:基于Cadence的IC設計

2013-04-07 15:46:14 0

0 為專注于解決先進節點設計的日益復雜性,全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS) 今天宣布,臺積電已與Cadence在Virtuoso定制和模擬設計平臺擴大合作以設計和驗證其尖端IP。

2013-07-10 13:07:23 842

842 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS) 今天宣布推出用于實現電學感知設計的Virtuoso?版圖套件,它是一種開創性的定制設計方法,能提高設計團隊的設計生產力和定制IC的電路性能。

2013-07-15 17:13:14 2080

2080 全球電子創新設計Cadence公司與上海華力微電子,15日共同宣布了華力微電子基于Cadence Encounter數字技術交付55納米平臺的參考設計流程。華力微電子首次在其已建立55納米工藝上實現了從RTL到GDSII的完整流程。

2013-08-16 11:08:11 1384

1384 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS)與上海華力微電子有限公司,今天共同宣布華力微電子基于Cadence ? Encounter? 數字技術交付出55納米平臺的參考設計流程。

2013-08-16 12:02:40 1446

1446 基于Wide I/O接口的3D堆疊,在邏輯搭載存儲器設計上進行了驗證 ,可實現多塊模的整合。它將臺積電的3D堆疊技術和Cadence?3D-IC解決方案相結合,包括了集成的設計工具、靈活的實現平臺,以及最終的時序物理簽收和電流/熱分析。

2013-09-26 09:49:20 1346

1346 Mentor Graphics 公司(納斯達克代碼:MENT)今天宣布推出最新 Xpedition? Package Integrator 流程,這是業內用于集成電路 (IC)、封裝和印刷電路板 (PCB) 協同設計與優化的最廣泛的解決方案。

2015-03-24 12:03:16 1684

1684 IC design 集成電路的設計流程以及cadence的簡介,使用方法和入門須知。

2016-03-14 14:11:33 25

25 2017年4月18日,中國上海 – 楷登電子(美國Cadence公司,NASDAQ: CDNS)今日正式發布針對7nm工藝的全新Virtuoso? 先進工藝節點平臺。通過與采用7nm FinFET

2017-04-18 11:09:49 1165

1165 、對基帶低頻大信號有高線性度要求的模塊、發射端大電流的PA 模塊、鎖相環頻率綜合器中的數字塊,以及非線性特性的VCO等各具特點的電路。眾多的電路單元及其豐富的特點必然要求在這種系統的設計過程中有一個功能豐富且強大的設計平臺。在綜合比較后,本文選定了Cadence Virtuoso 全定制IC 設計工具。

2018-06-06 09:37:00 10797

10797

采用Virtuoso電路原理圖編輯器與Virtuoso版圖套件將總周轉時間縮短30-50%:Virtuoso電路原理圖編輯器內置種類齊全的的,用于各種仿真的,定義明確的元件庫,可以加快模擬電路

2018-08-08 18:11:11 1324

1324 該流程無縫集成在Cadence Virtuoso平臺中,并使用Xpeedic加速矩量法引擎和人工神經網絡(ANN)技術,既提供在設計階段快速準確的無源器件建模和電路綜合功能,又能在Sign-Off

2018-11-09 11:53:09 3716

3716 區別于altium的一庫走天下,cadence的PCB套件流程中,PCB封裝的制作需要單獨制作pad,然后繪制封裝。這兩步的工具分別為Padstack和PCB Editor

2019-11-02 09:32:55 9632

9632

中;在設計階段中實現快速無源器件建模和合成;在簽核sign-off 階段實現精確驗證,同時能把封裝的影響考慮進來。在本文中,演示了IRIS-HFSS整合流程,它無縫地集成在Cadence Virtuoso平臺中(如圖1所示)。在設計階段,IRIS和 iModeler采用加速矩量法(

2020-10-20 10:42:00 2

2 cadence 公司 IC5141 工具主要包括集成平臺 design frame work II、原理圖編輯工具 virtuoso schematic editor、仿真工具、版圖編輯工具

2020-07-21 08:00:00 3

3 Cadence 3D-IC Integrity 平臺在統一的環境中提供 3D 芯片和封裝規劃、實現和系統分析。

2021-10-28 14:53:35 2114

2114 Integrity 3D-IC 是 Cadence 新一代多芯片設計解決方案,它將硅和封裝的規劃和實現,與系統分析和簽核結合起來,以實現系統級驅動的 PPA 優化。 原生 3D 分區流程可自動智能

2021-11-19 11:02:24 3347

3347 Cadence Integrity 3D-IC 平臺是業界首個全面的整體 3D-IC 設計規劃、實現和分析平臺,以全系統的視角,對芯片的性能、功耗和面積 (PPA) 進行系統驅動的優化,并對 3D-IC 應用的中介層、封裝和印刷電路板進行協同設計。

2022-05-23 16:52:50 1594

1594

楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,Cadence? 射頻集成電路解決方案支持 TSMC 的 N6RF 設計參考流程和制程設計套件(PDK),加速推進移動、5G 及無線應用創新。

2022-06-22 16:34:01 1774

1774 。8nm 射頻集成電路設計參考流程中支持的 Cadence 產品包括:Virtuoso ADE Product SuiteSpectre? RF SimulatorQuantus? Extraction

2022-10-18 14:16:56 1342

1342 聯華電子(NYSE:UMC;TWSE:2303)與楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日共同宣布,采用 Integrity 3D-IC 平臺的 Cadence 3D-IC 參考工作流程已通過聯電的芯片堆棧技術認證,將進一步縮短產品上市時間。

2023-02-03 11:02:23 1418

1418 ,包括最新的 N3E 和 N2 工藝技術。這一新的生成式設計遷移流程由 Cadence 和臺積電共同開發,旨在實現定制和模擬 IC 設計在臺積電工藝技術之間的自動遷移。與人工遷移相比,已使用該流程的客戶成功地將遷移時間縮短了 2.5 倍。

2023-05-06 15:02:15 801

801 3Dblox 標準適用于在復雜系統中實現 3D 前端設計分區。通過此次最新合作,Cadence 流程優化了所有 TSMC 最新 3DFabric 供需目錄上的產品,包括集成扇出(InFO)、基板

2023-05-09 09:42:09 615

615 設計過程。該平臺實現了跨學科的工作流程無縫協作、集成了Cadence一流的簽核級仿真分析工具,并提供了更強大的layout性能。

2023-05-22 15:40:10 1796

1796

了新一代定制設計平臺 Cadence Virtuoso Studio ,該平臺采用全新的底層架構,以獨特的方法來管理設計流程,可將當今大型設計的設計同步吞吐量提升 3 倍,是面臨大型復雜項目和有短時間

2023-06-13 12:15:02 557

557

與 Pegasus Verification System 和 Voltus-XFi Solution 集成,為 Samsung PDK 用戶提高了生產力,幫助他們更快地將高質量設計推向市場 中國上海

2023-06-30 10:08:30 681

681 內容提要 1 輕松實現節點到節點的設計和 layout 遷移 2 將定制/模擬設計遷移速度提升 2 倍 3 Cadence Virtuoso Studio 針對所有 Samsung Foundry

2023-07-04 10:10:01 471

471 已經過 SF2 和 SF3 流程認證 ●? Cadence 數字全流程針對先進節點實現了最佳 PPA 結果 ● Cadence 定制/模擬工具,包括基于 AI 的 Virtuoso Studio

2023-07-05 10:10:01 322

322 已經過 SF2 和 SF3 流程認證 ●?Cadence 數字全流程針對先進節點實現了最佳 PPA 結果 ●Cadence 定制/模擬工具,包括基于 AI 的 Virtuoso Studio,已針對

2023-07-05 10:12:14 381

381 ?? 雙方利用 Cadence 的 Integrity 3D-IC 平臺,優化多晶粒規劃和實現,該平臺是業界唯一一個整合了系統規劃、封裝和系統級分析的平臺。 ?? Integrity 3D-IC

2023-07-06 10:05:04 329

329 了新一代定制設計平臺 Cadence Virtuoso Studio ,該平臺采用全新的底層架構,以獨特的方法來管理設計流程,可將當今大型設計的設計同步吞吐量提升 3 倍,是面臨大型復雜項目和有短時間

2023-07-11 12:15:02 241

241

了新一代定制設計平臺 Cadence Virtuoso Studio ,該平臺采用全新的底層架構,以獨特的方法來管理設計流程,可將當今大型設計的設計同步吞吐量提升 3 倍,是面臨大型復雜項目和有短時間

2023-09-01 12:20:01 413

413

Cadence Virtuoso定制設計平臺的一套全面的集成電流(IC)設計系統,能夠在多個工藝節點上加速定制IC的精確芯片設計,其定制設計平臺為模擬、射頻及混合信號IC提供了極其方便、快捷而精確的設計方式。

2023-09-11 15:14:16 3202

3202

● AI 驅動的 Cadence Virtuoso Studio 助力 IC 設計在 TSMC 的制程技術之間實現遷移時自動優化電路 ●? 新的生成式設計技術可將設計遷移時間縮短

2023-09-27 10:10:04 301

301 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布與臺積電(TSMC)合作將新推出的 Cadence Virtuoso Studio 集成到 TSMC N16 毫米波設計參考流程

2023-09-28 10:10:02 533

533 平臺以獨特的方式將系統規劃、實現和系統層級分析整合成為一個解決方案,實現無縫的原型驗證 ●? 共同客戶可為其 AI、移動、5G、超大規模計算和物聯網 3D-IC 設計進行系統原型建模,加快

2023-10-08 15:55:01 249

249 Cadence印刷電路板指南

2022-12-30 09:19:47 13

13 Cadence高速電路板設計與仿真(第2版)

2022-12-30 09:19:52 2

2 Cadence高速電路板設計與仿真(第3版)

2022-12-30 09:19:52 2

2 CADENCE高速電路板設計與仿真(第4版)

2022-12-30 09:19:53 56

56 Cadence高速電路板設計與仿真

2022-12-30 09:19:53 19

19 內容提要●熱、應力和電子散熱設計同步分析,讓設計人員可以無縫利用ECAD和MCAD對機電系統進行多物理場仿真●融合FEM和CFD引擎,應對各種熱完整性挑戰——從芯片到封裝,從電路板到完整的電子系統

2024-02-19 13:00:09 216

216

Cadence 與 Intel 代工廠合作開發并驗證了一項集成的先進封裝流程。該流程能利用嵌入式多晶粒互連橋接(EMIB)技術來應對異構集成多芯粒架構不斷增長的復雜性。

2024-03-11 11:48:05 210

210

電子發燒友App

電子發燒友App

評論