的靈活性和較低的差錯誤碼特性,可實現并行操作,譯碼復雜度低,適合硬件實現,吞吐量大,極具高速譯碼的潛力,在碼長較長的情況下,仍然可以有效譯碼。 目前常用的信道編碼體制有BCH碼、RS碼、卷積碼、Turbo碼和LDPC碼等。其中BCH碼和RS碼都屬于線性分組碼的范疇

2020-11-02 13:56:16 39198

39198

LDPC碼在IEEE802.16e、IEEE802.11n、IEEE802.11ac、IEEE802.11ad以及5G等高吞吐量系統中得到了廣泛的應用。

2023-04-27 09:09:31 7769

7769

論壇里面的大神們,有沒有已經完成LDPC碼編譯碼算法的FPGA實現,本人目前在做這方面的項目,時間比較緊,緊急求購IP核。。

2012-04-16 23:43:28

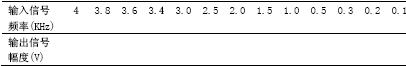

編譯碼的原理是什么?如何對編譯碼算法進行仿真測試?

2021-04-28 06:54:22

MATLAB卷積編譯碼源代碼

2012-04-10 20:38:14

system view中如何進行AMI編譯碼,求大神!!!!!!!!!!!!

2012-12-24 11:11:30

【作者】:申睿;鄧運松;向波;陳赟;曾曉洋;【來源】:《小型微型計算機系統》2010年03期【摘要】:提出一種通用的QC-LDPC碼譯碼器架構.該架構采用一種特殊的綁定結構和一個可配置的循環移位網

2010-04-24 09:26:56

請問各路大神有沒有基于multisim的線性分組碼 循環碼 卷積碼的編譯碼電路圖啊,在這里謝過你們了

2015-04-23 17:56:37

增量調制(ΔM)編譯碼實驗一、實驗目的 1、了解語音信號的ΔM編碼過程; 2

2009-10-11 08:58:46

LDPC碼是近年來發展較快且日趨成熟的一種信道編碼方案,因其具有的優越性能和實用價值而被人們認知,但由于隨機結構的LDPC碼編譯碼器硬件實現較為復雜,具有的準循環特性QC_LDPC碼已成為IEEE802.11n(WiFi)、IEEE802.16e(WiMAX)、(DVB—S2)等眾多標準的信道編碼方案。

2019-09-30 07:19:45

本文研究了RS碼的實現方法,并基于Xilinx的FPGA芯片Spartan-6 XC6SLX45完成了RS編譯碼器的設計,同時對其進行了仿真和在線調試,并給出了功能仿真圖和測試結果。時序仿真結果表明,該編譯碼器能實現預期功能。

2021-06-21 06:23:53

低密度奇偶校驗(LowDensityParityCheck,LDPC)碼是由Gallager博士在1962年首次提出來的,由于LDPC碼的誤碼性能能夠逼近香農限,因而在無線通信、衛星通信等領域都得

2019-08-23 07:22:50

標準中LDPC碼的構造、編碼及解碼算法原理,結合MAT-LAB仿真對其算法有效性進行了分析比較。【關鍵詞】:數字電視傳輸系統;;低密度奇偶校驗碼;;DMB-TH;;編譯碼器【DOI】:CNKI:SUN

2010-04-23 11:36:52

用matlab來仿真turbo編譯碼的程序,有沒有完整的程序及仿真過程

2014-04-23 10:22:56

Turbo碼編碼器的FPGA實現Turbo碼譯碼器的FPGA實現Turbo碼編譯碼器的性能有哪些?

2021-05-07 06:06:23

本文在SvstemGenerator中對LDPC碼整個編譯碼系統進行了參數化的硬件實現,并構建了超寬帶通信系統LDPC碼硬件仿真平臺,驗證了LDPC碼在UWB通信中的優異性能。

2021-06-03 07:01:58

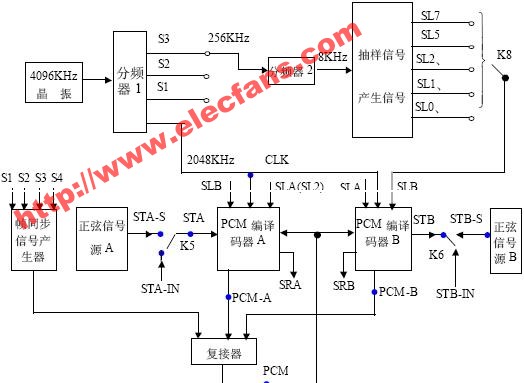

PCM編譯碼器是數字通信中必不可少的部件,MT896X系列編譯碼器性能滿足CCIT T 和ATT規范要求、且還有環回、測試等各種附加功能,片上還集成了4/5個獨立的驅動器,可簡化交換機用戶環路

2009-04-23 14:22:40 20

20 針對LDPC碼與RS碼的串行級聯結構,提出了一種基于Chase的聯合迭代譯碼方法。軟入軟出的RS譯碼器與LDPC譯碼器之間經過多次信息傳遞,性能可以逼近最大似然譯碼。模擬結果顯示:

2009-05-12 21:47:25 22

22 簡易編譯碼電路圖

2009-05-19 10:47:26 9

9 本文基于Altera的FPGA(StatixⅡ-EP2S30F484C3)架構,實現了碼率為1/2,幀長為1008bits的規則(3,6)LDPC碼譯碼器。所采用的最小-和算法相對于傳統的和-積算法在不損失譯碼性能的前提下,

2009-06-06 14:12:20 31

31

Low-Density Parity-Check (LDPC) codes are linear

block codes specified by very sparse

2009-07-24 14:45:06 0

0

Recently, a number of LDPC decoder architectures have

been proposed

2009-07-24 14:49:51 0

0 Low-Density Parity-Check (LDPC) code achieves informa-tion rates close to the Shannon limit

2009-07-24 15:00:01 0

0 A 640-Mbs 2048-bit programmable LDPC decoder chipA Memory Efficient Partially Parallel Decoder

2009-07-24 15:02:24 0

0 LDPC原理與應用的主要內容:

第一章 緒論第二章 信道編碼基礎第三章 LDPC碼概述第四章 LDPC碼譯碼第五章 結構LDPC碼的編碼構造第六章 各種編碼方法設計的LDPC碼

2009-07-24 15:07:06 0

0 An Introduction to LDPC Codeslow_power VLSI Decoder architectures for ldpc codesLow-Density

2009-07-24 15:45:40 0

0 面向IEEE 802.16e 中 LDPC 碼,分析了各種譯碼算法的譯碼性能,歸一化最小(NMS)算法具備較高譯碼性能和實現復雜度低的特點。提出一種基于部分并行方式的LDPC 譯碼器結構,可以滿

2009-08-05 08:46:59 24

24 VSPC-LDPC串行級聯碼的結構與性能分析:提出了一種基于LDPC碼和縱向單奇偶校驗(VSPC)乘積碼的級聯編碼方法。該方法利用LDPC碼能否成功地譯碼的判定信息以取代常規乘積碼中的橫向校

2009-10-20 18:01:32 15

15 基于LDPC譯碼軟信息的迭代載波恢復:針對較低信噪比(≤2 dB)下載波恢復難題,該文提出了基于LDPC 軟信息的迭代載波恢復算法。該算法以最大化LDPC 軟信息絕對值的和為準則,對載波

2009-10-29 13:03:50 18

18 基于可靠性更新的低復雜度B譯碼算法:基于部分符號更新策略的BP (Belief Propagation)譯碼算法減少了LDPC (Low-Density Parity-Check)碼的譯碼運算量,提高了譯碼效率。然而在其譯碼過程中,由

2009-10-29 13:09:21 16

16 循環移位置換單元是準循環LDPC 碼的部分并行譯碼器的重要組成部分。該文研究并證明了ReverseBanyan 交換結構在實現信息循環移位時各個基本交換單元的連接規律。基于該規律設計了

2009-11-09 14:21:56 17

17 本文以CCSDS 推薦的7/8 碼率LDPC 碼為例,提出了一種適于高碼率LDPC 碼譯碼器的硬件結構優化方法。高碼率的LDPC 碼通常也伴隨著行重與列重的比例較高的問題。本方法是在拆分校驗矩

2009-11-25 15:21:25 26

26 該文從譯碼速率、硬件實現的復雜度和誤碼率3 個方面對比研究了兩種典型的高速譯碼算法:Turbo 型和積算法與并行加權比特翻轉算法。以準循環LDPC 碼為對象,給出了Turbo 型和積算

2009-11-25 15:26:58 9

9 本文利用可編程邏輯的靈活性和Nios 的強大處理能力,將多種編譯碼模塊和微處理器模塊集成到一片FPGA 內部,方便地實現了通用編譯碼器的設計。由于采用了VHDL 語言,使系統具有可移

2009-11-30 14:27:56 22

22 規則LDPC碼的密度進化方法及其高斯近似:密度進化方法是分析現代高效糾錯編譯碼漸進性能的新方法。在簡要闡述LDPC碼及其和積算法的基礎上,較系統的論述了密度進化方法的基本

2010-01-12 18:55:09 18

18 數字光纖通信系統的原理框圖如圖1所示(其中調制器與解調器包括電光轉換與光電轉換功能),我們所做的工作是設計信道編譯碼部分的電路,在通信系統中所處的位置如圖中虛線

2010-04-20 22:33:12 83

83 摘要:在數字通信中,選擇合適在信道中傳輸的碼型是十分重要的,HDB3碼是比較常用的信道傳輸碼型,因此HDB3碼的編譯碼就顯得非常重要.多數的數字基帶信號用單極性不歸零碼(NR

2010-05-17 09:08:49 41

41 基于TMS320C6416高性能通用DSP,實現了對AWGN信道的信噪比(SNR)估計,并以此估計值設計了一種低密度奇偶校驗(LDPC)碼的譯碼系統;詳盡介紹了集成SNR估計的譯碼系統的實現方案和流程;仿真

2010-07-27 16:28:32 11

11 低密度奇偶校驗碼(Low-Density-Parity-Checkcodes,簡稱LDPC碼)是第四代通信系統強有力的競爭者,它是一種逼近香農限的線性分組碼,譯碼的復雜度較低;但它的直接編碼運算量較大,

2010-08-09 15:06:22 0

0 針對固定碼長Turbo碼適應性差的缺點,以LTE為應用背景,提出了一種幀長可配置的Turbo編譯碼器的FPGA實現方案。該設計可以依據具體的信道環境和速率要求調節信息幀長,平衡譯碼性

2010-11-11 16:07:59 26

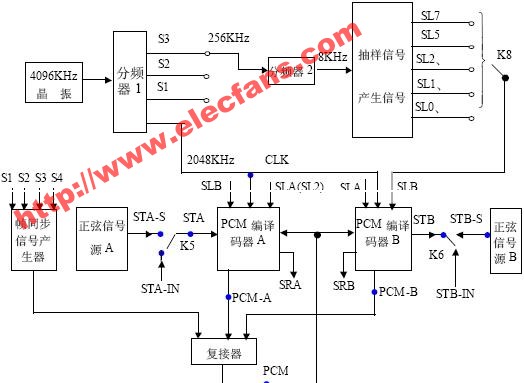

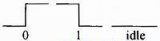

26 PCM編譯碼模塊原理

本模塊的原理方框圖圖5-2所示,模塊內部使用+5V和-5V電壓,其中-5V電壓由-12V電源經7905變換得到。

2008-10-21 13:31:10 7114

7114

PCM編譯碼實驗

一、實驗目的1. 掌握PCM編譯碼

2008-10-21 13:35:45 8339

8339

基于BIST的編譯碼器IP核測

隨著半導體工藝的發展,片上系統SOC已成為當今一種主流技術。基于IP復用的SOC設計是通過用戶自定義邏輯(UDL)和連線將IP核整合

2008-12-27 09:25:39 794

794

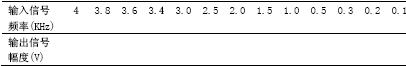

實驗九 PCM編譯碼 一、實驗目的

1. 掌握PCM編譯碼原理。 2. 掌握PCM基帶信號的形成過程

2009-04-01 14:44:49 10289

10289

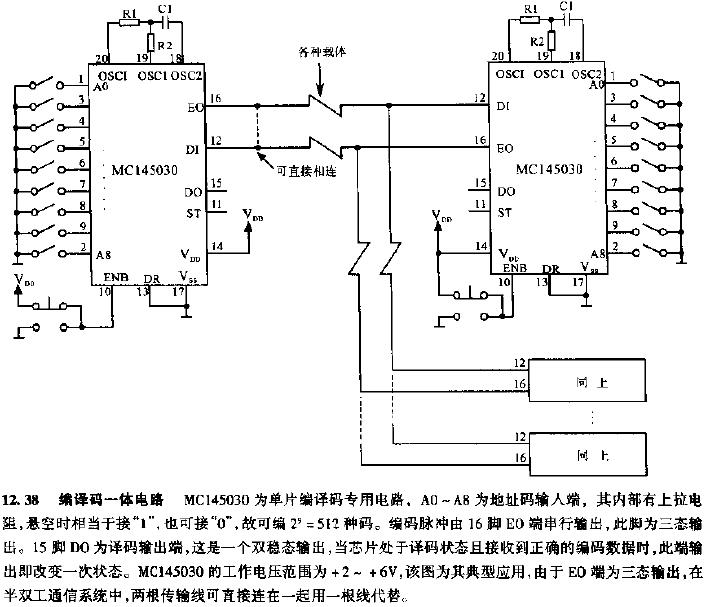

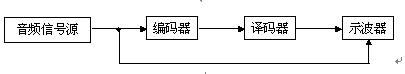

編譯碼一體電路圖

2009-04-18 15:34:48 752

752

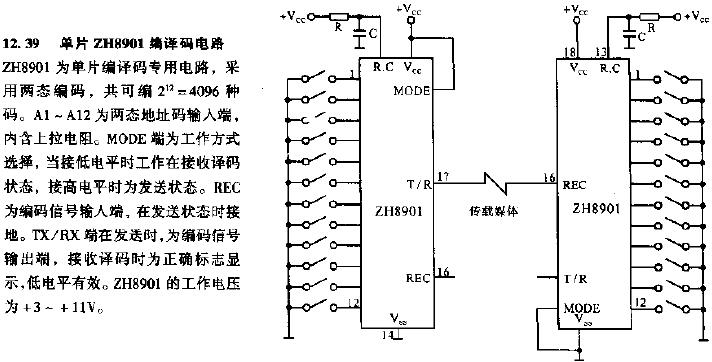

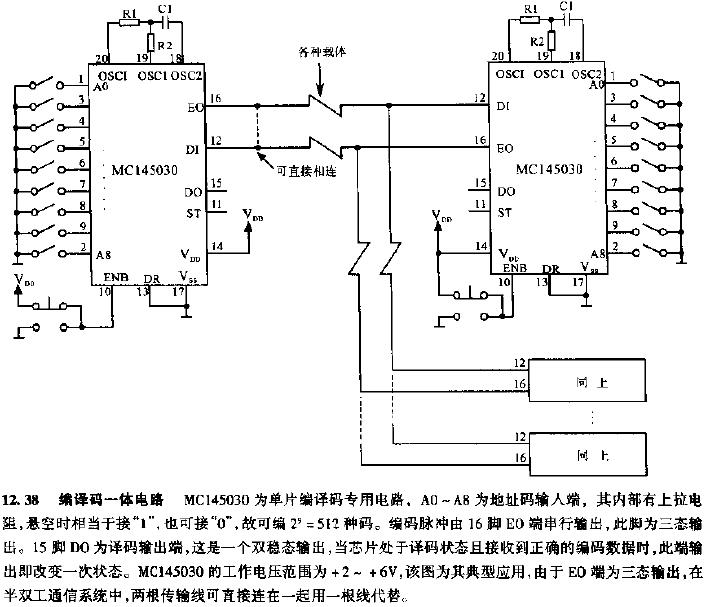

單片ZH8901編譯碼電路

2009-04-18 15:36:11 910

910

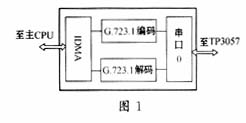

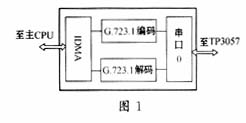

【摘 要】 介紹了ITU-TG.723.1標準語音編譯碼器的算法及其在ADSP-2181芯片上的實現 。軟硬件結合實現了語音信號的采樣和實時編譯碼,完全符合ITU-TG.723.1標準的定點算法

2009-05-10 19:54:11 1284

1284

摘要:提出了基于歐氏算法和頻譜分析相結合的RS碼硬件編譯碼方法;利用FPGA芯片實現了GF(2 8)上最高速率為50Mbps、最大延時為640ns的流式譯碼方案,滿足了高速

2009-06-20 14:19:33 856

856

ADPCM編譯碼系統電路

模擬信號

2009-10-11 11:07:30 1366

1366

應科院伙拍歐思電子及Silterra推出全新音頻編譯碼兼音效后處理方案OPT5256

香港應用科技研究院(應科院)伙拍歐思電子有限公司(歐思電子),一家位于深圳的集成電

2009-12-01 08:40:01 960

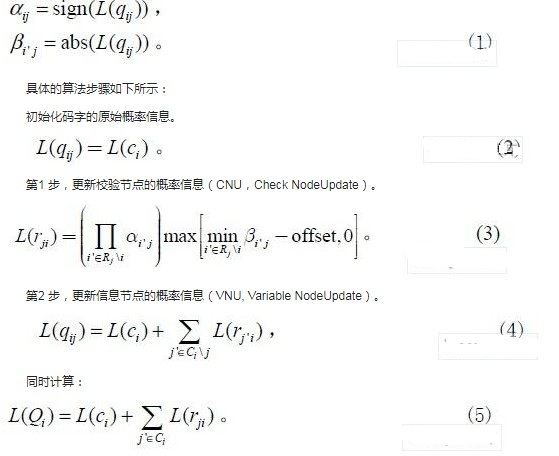

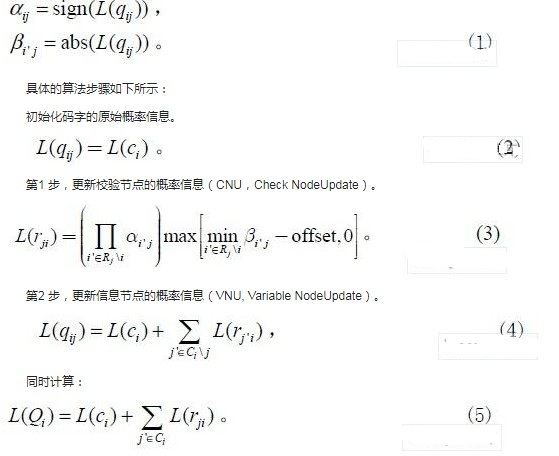

960 針對低密度奇偶校驗(LDPC)譯碼算法性能低的問題,提出一種基于最小和的高效譯碼算法。該算法從概率的角度分析消息的傳遞過程中校驗節點的更新過程,得到近似的最小和算法等式,

2011-05-18 18:54:20 0

0 本文設計實現了一種支持WIMAX標準的碼長、碼率可配置LDPC碼譯碼器,通過設計一種基于串行工作模式的運算單元,實現了對該標準中所有碼率的支持

2011-06-08 09:52:17 1766

1766

介紹了ITU-TG.723.1標準語音編譯碼器的算法及其在ADSP-2181芯片上的實現 。軟硬件結合實現了語音信號的采樣和實時編譯碼,完全符合ITU-TG.723.1標準的定點算法,通過了ITU-T的所

2011-07-06 09:49:07 1295

1295

雙網傳真系統完成與Internet和PSTN網絡的傳真通信,采用嵌入式系統的設計思路劃分軟硬件。其中,傳真協議采用軟件實現,傳真編譯碼和外圍設備控制器采用硬件實現,以降低設計復雜

2011-07-12 11:19:59 1523

1523

本文首先介紹了信道編碼的發展歷程,以及LDPC碼的基本原理和摹本概念,然后從校驗矩陣的構造方法、迭代譯碼算法以及性能分析等幾個方面對LDPC碼進行了討論, 介紹了相關技術的主

2011-08-26 11:44:01 0

0 提出了一種新的動態補償最小和譯碼算法,并將本算法和修正最小和譯碼算法進行了性能比較。仿真結果顯示,動態補償最小和譯碼雖然算法迭代的收斂速度有所減慢,但具有比修正最

2011-10-08 15:05:33 27

27 從赫夫曼樹定義及算法出發,介紹了一個赫夫曼編譯碼系統的設計與實現過程。這對于深入理解數據結構、程序設計有益。

2011-10-19 14:44:01 31

31 本文提出了一種基于STM32F103RET6的編譯碼系統方案,利用了STM32F103RET6強大的定時器功能,采用靈活的編譯碼方式,傳輸速率和數據幀格式都可以根據需要完全自行定義。

2012-03-04 14:38:45 6524

6524

在描述置信傳播(BP)譯碼算法基礎上, 研究和分析了兩種降低復雜度的譯碼算法。Min.Sum 算法主要討論了簡化校驗節點的消息更新運算,并應用密度進化方法對此算法進行極限性能分析

2012-03-31 15:22:03 7

7 本文介紹了 RS[ 255, 223 ]編譯碼器的 FPGA設計和基于線形反饋移位寄存器的編碼器設計 , 以及由伴隨式計算、關鍵方程求解、錢氏搜索、Forney算法等功能模塊組成的譯碼器。為了實現簡單

2012-05-22 10:43:40 45

45 在LDPC譯碼時,使用LLR BP算法其校驗節點的計算復雜度十分高,而且當LDPC碼中有許多的短環時,譯碼性能也會降低。基于以上的這些問題提出了一個新的混合校驗變量過程,通過調整校

2012-07-06 16:44:03 42

42 上世紀60年代初,香農的學生Gallager在他的博士畢業論文中首次提出了LDPC碼的概念和完整的譯碼方法,但是直到上世紀末期,隨著LDPC碼譯碼理論的進步和計算機技術的發展,LDPC碼才以其

2012-11-07 15:05:11 0

0 香農的學生Gallager首次提出了LDPC碼的概念和完整的譯碼方法,目前LDPC碼正向著高速高增益的方向發展。文中針對目前對高速LDPC碼譯碼技術的迫切需求,以CCSDS標準近地通信(8176,7154)

2013-07-26 11:17:00 0

0 MIMO系統中基于因子圖的聯合迭代檢測和LDPC譯碼_王忠勇

2017-01-07 16:00:43 0

0 一種基于改進線性規劃的LDPC碼混合譯碼算法_陳紫強

2017-01-07 16:52:06 0

0 基于FPGA的3B4B編譯碼電路

2017-02-07 14:58:18 11

11 的運行,可以考慮將循環較多的功能采用C編寫,MATLAB調用。本文將概述這一過程。雖然本文以LDPC譯碼算法為例,但不懂該算法不影響本文閱讀。

2018-07-12 01:49:00 3953

3953 利用C++仿真了LDPC碼,譯碼采用了基于對數似然比的BP算法。編碼矩陣可以在根文件夾中選擇。

2017-03-29 09:22:24 0

0 本文從研究應用于AOS系統的RS(255,223)編譯碼接口卡出發,深入地分析和研究了糾錯碼原理、RS編譯碼算法與設計、PCI總線標準與設計和FPGA技術。 隨著科技的發展,糾錯碼技術在通信領域

2017-08-31 14:50:39 4

4 提出了一種實用的LDPC碼譯碼停止準則,利用信息節點的對數概率似然比來控制迭代次數,避開了設置停止準則門限,可以很快判斷出譯碼情況,較其他方法省去了大量繁雜的計算。

2017-09-07 19:38:11 10

10 為了降低非規則低密度奇偶校驗(low-densityparity-check,LDPC)碼譯碼算法的復雜度,提出一種適合數字信號處理囂(digital signal processor,DSP)實現

2017-10-20 10:41:11 0

0 該文通過對低密度校驗(LDPC)碼的編譯碼過程進行分析,提出了一種基于FPGA 的LDPC 碼編譯碼器聯合設計方法,該方法使編碼器和譯碼器共用同一校驗計算電路和復用相同的RAM 存儲塊,有效減少

2017-11-22 07:34:01 3928

3928

中小長度的數據報文業務為主,所以突發通信中的Turbo碼的碼長也是中等長度以下的。本文面向突發數據通信中的信道編碼應用,研究了短幀長Turbo碼編譯碼算法的FPGA實現。實現中采用了優化的編譯碼算法,以降低譯碼復雜度和譯碼延時。最后仿真和測試了Turbo譯碼器的糾錯性能和吞吐量。

2018-07-12 08:15:00 3247

3247

信息協調是量子密鑰分發中的關鍵步驟,基于LDPC實現量子信息協調是當前國內外研究的焦點。目前QKD系統LDPC譯碼器普遍采用單碼字順序譯碼機制設計,且采用的是性能較差的準循環LDPC碼,LDPC

2017-11-25 10:10:46 2

2 由于曼徹斯特(MancheSTer)編碼具有傳輸時無直流分量,時鐘提取方便等特點,被廣泛地應用于以太網、車輛總線、工業總線中。現在工程上常用的曼徹斯特編譯碼芯片為HD-6408和HD-6409,但是

2017-11-27 11:31:28 4

4 信道編譯碼技術可以檢測并且糾正信號在傳輸過程中引入的錯誤,能夠保證數據進行可靠的傳輸[1]. LDPC碼的校驗矩陣具有稀疏的特性,因此存在高效的譯碼算法,其糾錯能力非常強。1981年,Tanner

2017-11-30 10:21:27 4604

4604

1996年LDPC(低密度奇偶校驗,Low-Density Parity-Check)碼是性能限與香農限僅差0.0045 dB的一種差錯控制碼,譯碼采用SPA(和積算法),但其性能受Tanner圖中

2017-12-26 11:09:14 0

0 算法展開研究,以保證矩陣稀疏性為目標,分析了行主元選取策略。同時研究了多元域LDPC碼的迭代譯碼算法。對多元域LDPC碼糾錯系統的糾錯性能進行了仿真,測試結果表明多元域LDPC碼的性能優于信源信息速率和碼率相同的二進制LDPC碼,為多元域L

2017-12-29 14:04:59 0

0 的重視。基于準循環LDPC(QC-LDPC)碼結構特點,提出了一種支持多種碼率QC-LDPC 譯碼器的設計方法,并設計實現了一個能夠實時自適應支持三個不同H 陣的通用QC-LDPC 譯碼器。

2019-01-08 09:22:00 2787

2787

本文介紹用配套數字編譯碼器YN5103/YN5203組裝的紅外遙控電路,最多可提供12位地址或6位數據、譯碼輸出有鎖存L和暫留M兩種模式供選擇。用于一發多收、一收多發的紅外遙控電路中。

2018-09-25 11:09:00 4312

4312

第三代移動通信系統多種方案中,考忠將Turbo碼作為無線信道的編碼標準之- ~。 本文討論了Turbo碼的編譯碼基本原理,對Turbo碼的幾種常用的編譯碼算法進行了分析,并在給出編譯碼器模型的基礎上,用MATLAB語言實現了整個系統的計算機仿真并給出參

2019-01-04 10:40:42 19

19 本文檔的主要內容詳細介紹的是漢明碼編譯碼器的數據手冊免費下載。

2019-12-13 08:00:00 0

0 信道編碼作為移動通信系統可靠通信的基石, 在第五代移動通信系統(TheFifth Generation Wireless System,5G)中顯得尤為重要。由于性能接近Shannon限、編譯碼算法

2020-07-22 17:51:12 20

20 為塊準循環結構,從而能夠并行化處理譯碼算法的行與列操作。使用這個架構,我們在Xilinx Virtex-5 LX330 FPGA上實現了(8176,7154)有限幾何LDPC碼的譯碼器,在15次迭代的條件下其譯碼吞吐量達到800Mbps。

2021-01-22 15:08:39 9

9 針對一類規則(r,c)-LDPC(low-density parity check)碼,提出了一種基于Turbo譯碼算法的高吞吐量存儲器效率譯碼器。與傳統的和積譯碼算法相比,Turbo譯碼算法對多個

2021-02-03 14:46:00 9

9 結構化LDPC碼可進行相應擴展通過對編譯碼算法,優化編譯碼結構進行調整,降低了編譯碼囂硬件實現中的關鍵路徑遲延,并采用Xilinx公司的Virtex一4 VLX80 FPGA芯片實現了一個碼長10 240,碼率1/2的非正則結構化LDPC碼編碼器和譯碼器。實現結果表明:該編碼器信息吞吐量為1.878 Gb/

2021-03-26 15:58:00 12

12 基于軟件無線電的NRLDPC編譯碼設計與實現。

2021-05-28 10:07:04 5

5 基于FPGA的800Mbps準循環LDPC碼譯碼器

2021-06-08 10:31:31 26

26 電子發燒友網站提供《基于VHDL語言的循環碼編譯碼系統的設計.pdf》資料免費下載

2023-10-13 14:31:37 1

1 電子發燒友網站提供《漢明碼編譯碼文檔.doc》資料免費下載

2023-11-17 16:04:06 0

0

電子發燒友App

電子發燒友App

評論