電路板系統(tǒng)的互連包括:芯片到電路板、PCB板內(nèi)互連以及PCB與外部器件之間的三類互連。

2023-03-08 17:01:27 981

981

如果說人工智能推動了第四次工業(yè)革命,那么工業(yè)物聯(lián)網(wǎng)必然是這次革命的領(lǐng)潮者之一。近日,國外的一項調(diào)查結(jié)果顯示,工業(yè)物聯(lián)網(wǎng)已經(jīng)開始對行業(yè)產(chǎn)生影響。

2016-06-12 10:55:28 1348

1348 微處理器中常用的集成串行總線是通用異步接收器傳輸總線、串行通信接口、同步外設接口(SPI)、內(nèi)部集成電路(I2C)和通用串行總線,以及車用串行總線,包括控制器區(qū)域網(wǎng)(CAN)和本地互連網(wǎng)(LIN)。為了說明方便起見,本文的闡述是基于微處理器的設計。

2019-01-02 08:33:00 3572

3572

電路板系統(tǒng)的互連包括:芯片到電路板、PCB板內(nèi)互連以及PCB與外部器件之間的三類互連。

2018-12-29 10:27:28 6709

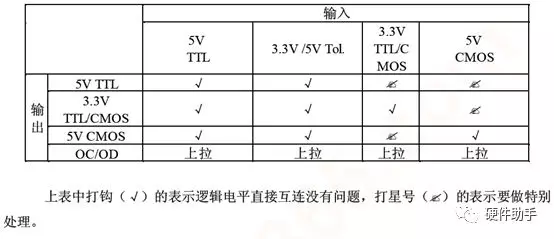

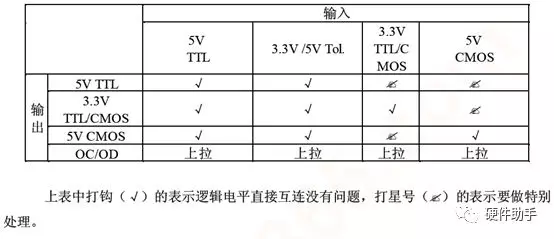

6709 本篇主要介紹TTL/CMOS電平的互連、OC/OD的互連,其余單端邏輯電平的互連可參考相關(guān)器件規(guī)范、電平規(guī)范。 1、TTL/CMOS互連 常用的TTL和CMOS電平主要是5V TTL、5V CMOS

2020-12-23 14:15:12 5648

5648

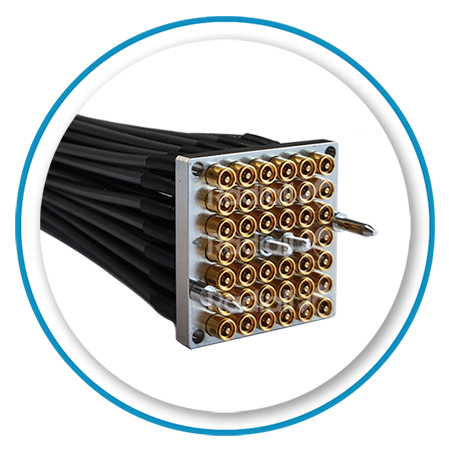

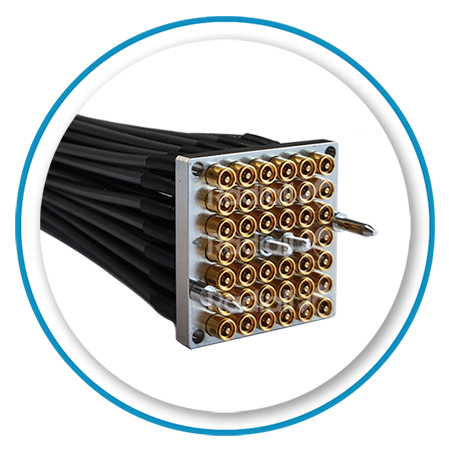

量子計算機可以解決當今最強大的超級計算機無法解決的復雜問題,而量子技術(shù)(傳感器、通信和計算機)有望成為一場技術(shù)革命,在這場技術(shù)革命的發(fā)展過程中,互連解決方案是重要的助推劑。 作為嚴苛環(huán)境下的互連

2023-09-25 17:40:49 348

348

,不但景區(qū)、城市要抓,農(nóng)村也要抓,要把這項工作作為鄉(xiāng)村振興戰(zhàn)略的一項具體工作來推進,努力補齊這塊影響群眾生活品質(zhì)的短板。廁所革命在國家的強力推動下迎來新的建設高潮,給從事廁所建設的相關(guān)單位帶來巨大的商機

2017-12-06 09:01:46

AHCC2001PCI/CPCI 是能提供 4 路高速串行數(shù)據(jù)通信的模板, 完成系統(tǒng)內(nèi)部計算機網(wǎng)絡與外部多路串行接口的互連功能。它內(nèi)含一片高性能的串行通信控制器,可以用于各種高速數(shù)據(jù)通信場合。每路

2019-04-25 09:40:07

因素。JESD204B串行接口規(guī)范專為解決這一關(guān)鍵數(shù)據(jù)鏈路的問題而建立。圖1表示使用JESD204A/B的典型高速轉(zhuǎn)換器至FPGA互連配置。本文余下篇幅將探討推動該規(guī)范發(fā)展的某些關(guān)鍵的終端系統(tǒng)

2019-05-29 05:00:04

本人理解的差分線最明顯的優(yōu)點,這些優(yōu)點奠定了串行信號穩(wěn)定傳輸?shù)幕A。當然,差分信號也存在一些缺點,最大的缺點就是與單端信號傳輸相比,差分互連需要兩倍數(shù)量的信號線。再者,如果差分信號不對稱,會產(chǎn)生潛在的EMI,這些問題都會在后續(xù)的文章中做詳細的分析。

2017-12-15 17:43:00

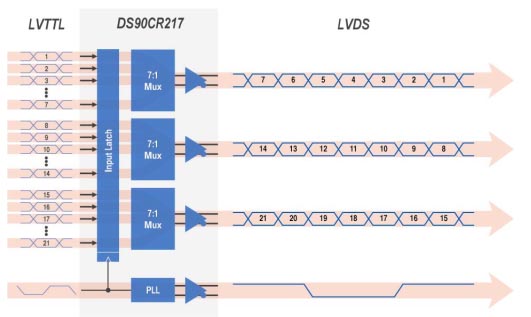

的減少、長距電纜驅(qū)動(長達10公尺)等等。為了應付這些挑戰(zhàn),美國國家半導體開發(fā)出了一款新型的互連數(shù)量極少(雙線)的串行接口產(chǎn)品。本文將介紹這款新型互連產(chǎn)品的特點,以及它是如何克服技術(shù)上的困難與相關(guān)產(chǎn)品

2019-05-05 09:29:34

互連測試的原理是什么?互連測試的主要功能有哪些?互連測試的基本算法有哪些?

2021-05-17 06:43:00

[attach]74350[/attach]IP核互連策略及規(guī)范

2012-08-12 12:20:18

IoT是怎樣推動傳感器創(chuàng)新的?求解

2021-05-21 07:15:43

` 本帖最后由 化二為一 于 2015-8-19 14:51 編輯

EMI問題常常因為高速、高邊沿信號的互連而變得更為復雜,因此互連的過程通常伴隨著串擾和地參考電平的分離,一個沒有屏蔽或良好地平

2015-08-19 14:49:47

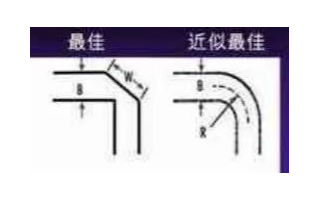

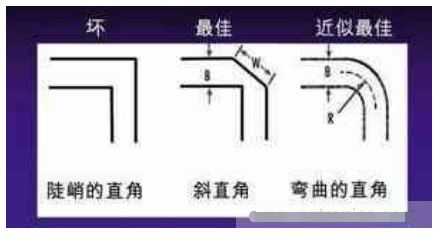

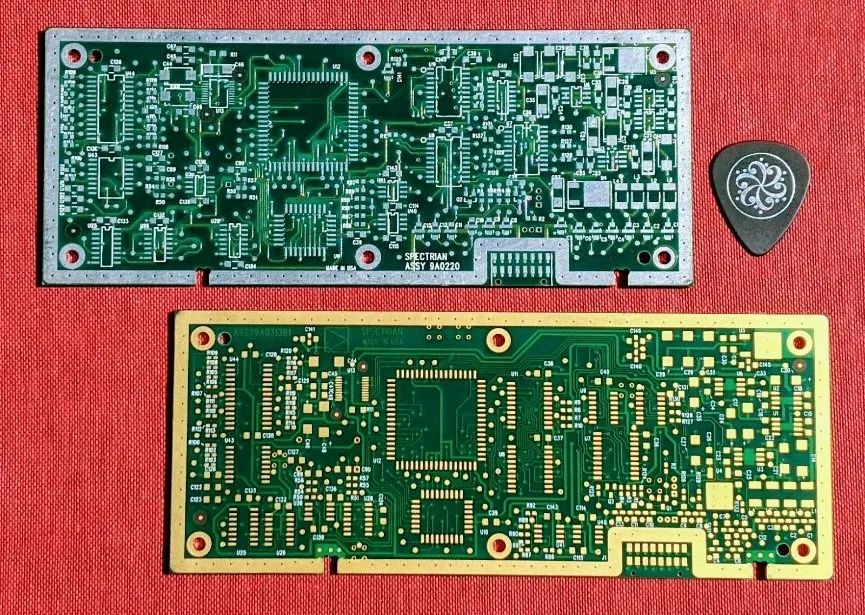

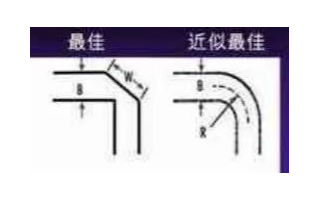

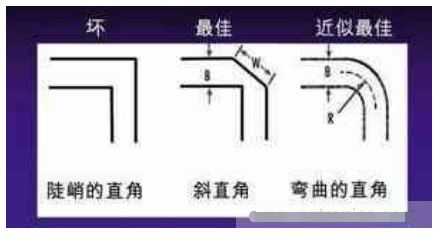

本文將介紹電路板系統(tǒng)的芯片到電路板、PCB板內(nèi)互連以及PCB與外部器件之間的三類互連設計的各種技巧,包括器件安裝、布線的隔離以及減少引線電感的措施等,以幫助設計師最大程度降低PCB互連設計中的RF效應。

2019-08-14 07:37:46

大家好!我想將Pandaboard與FPGA互連。在互聯(lián)網(wǎng)上搜索我發(fā)現(xiàn)可以使用GPMC互連它們,但遺憾的是我沒有找到任何關(guān)于USB的信息。我的問題是:是否可以通過USB互連兩塊板?如果是的話,必須執(zhí)行哪些操作才能連接這兩個板,以便它們能夠彼此“交談”?預先感謝。利瑪竇。

2019-09-04 09:39:40

iPhone 11中的U1芯片開啟了超寬帶革命。作者|Jason Snell譯者 |彎月,責編 | 郭芮出品 | CSDN(ID:CSDNnews)以下為譯文:蘋果很喜歡討論他們?yōu)閕Phone

2021-07-23 09:01:31

的模塊,然后作為一種主要的構(gòu)建技術(shù)將其疊加或盲插。這就需要毫微級的互連器件。醫(yī)療工業(yè)乃至軍事/宇航工業(yè)的制造商正推動著系統(tǒng)沿著這一模塊化方向發(fā)展以滿足復雜信號所要求的尺寸、重量及電流的降低。為應對這些

2016-06-06 15:40:32

stm32ad7606 spi串行,ad7606與stm32連接電路介紹 在STM32F105和STM32F107互連型系列微控制器之前,意法半導體已經(jīng)推出STM32基本型系列、增強型系列、USB

2021-08-05 07:03:12

`金秋九月,資源革命期八月逝而九月至,思緒浮沉頻回首;人生難得幾回搏,莫讓兩鬢霜對月。如果八月是一種回味,九月便是一種向往~俗話說時間等于金錢,知識等于力量,那么Jenny覺得資源等于知識源泉,力量

2016-08-31 17:19:23

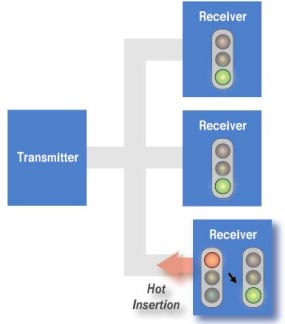

了解貨架和系統(tǒng)互連的影響(AN 1465-6)

2019-09-12 10:37:17

。相信,隨著互聯(lián)網(wǎng)與工業(yè)自動化融合的不斷深入,還將推動更多的新模式、新業(yè)態(tài)涌現(xiàn),互聯(lián)網(wǎng)將為制造業(yè)變革注入嶄新的力量!互聯(lián)網(wǎng)+工業(yè)自動化,將掀起新一輪的工業(yè)革命!快易優(yōu)自動化選型大全平臺

2016-02-25 20:35:16

人工智能對人類來說是革命還是傷害呢?能會給人類帶來很大的便利,但有一部分人卻擔心過于智能會威脅到人類的安全。那么人工智能對人類來說是革命還是傷害呢?`

2016-10-10 14:21:29

體驗。我們的VIVE?解決方案采用高通創(chuàng)銳訊基于算法的革命性技術(shù)進行增強,將使網(wǎng)絡容量提高三倍,優(yōu)化Wi-Fi設備的使用方式,最大限度地提高網(wǎng)絡上每個用戶的連接能力。

2019-08-15 07:58:07

從結(jié)構(gòu)來看,光互連可以分為:1)芯片內(nèi)的互連; 2)芯片之間的互連;3)電路板之間的互連;4)通信設備之間的互連。從互連所采用的信道來看,光互連可以分為:1)自由空間互連;2)波導互連;3)以及光纖

2016-01-29 09:17:10

的對準問題特別突出。雖然有很多的相關(guān)技術(shù)如有源和無源對準、自對準等,但都不是很理想。而且,很多的光互連技術(shù)是基于混合集成,光電芯片的單片集成困難很大。因此,光互連仍然需要更加適用和靈活的工藝技術(shù)來推動

2016-01-29 09:21:26

1)對光互連研究,以美國、日本、歐洲為中心日趨高漲,國內(nèi)的高校和研究所應該抓住機會,積極推動這一領(lǐng)域的研究。今后,作為解決因集成電路特征尺寸按比例縮小而引起的無法克服的困難,光互連仍然是研究的熱點

2016-01-29 09:23:30

的推動作用。近年來也出現(xiàn)了很多新技術(shù)和結(jié)構(gòu),促進其實用化。自由組織光波網(wǎng)絡技術(shù)該技術(shù)應用于波導、光開關(guān)、反射器、等光學器件的互連。先將要互連的光學器件放在一個光反射材料如全息光聚合物、光反射晶體上,這些

2016-01-29 09:19:33

光互連主要有兩種形式波導光互連和自由空間光互連。波導互連的互連通道,易于對準,適用于芯片內(nèi)或芯片間層次上的互連。但是,其本身損耗比較嚴重,而且集成度低。自由空間光互連可以使互連密度接近光的衍射極限

2019-10-17 09:12:41

描述ADAS 傳感器互連板適合需要將諸如攝像頭、激光雷達或雷達模塊之類的遙感器連接到中央處理 ECU 的應用。此板支持多達 3 個同軸電纜輸入和 1 個 LVDS 雙絞線數(shù)據(jù)輸入,以及 3 條

2018-08-08 07:57:11

隨著可穿戴設備持續(xù)推動封裝與互連技術(shù)超越極限,業(yè)界專家指出,未來還將出現(xiàn)許多更有趣的可穿戴設備創(chuàng)新。 可穿戴設備是一個多元化的領(lǐng)域,“至少有十幾種不同的細分市場,”高通(Qualcomm)負責

2016-08-09 17:19:41

基于FPGA的通用高速串行互連協(xié)議設計基于FPGA的通用高速串行互連協(xié)議設計

2012-08-11 15:46:52

DFT技術(shù)的發(fā)展具有深遠的影響。而其中互連測試又是其中最關(guān)鍵的技術(shù)之一。 二、互連測試的原理 互連測試主要是指對電路板上器件之間互連線的測試,主要檢測電路板級的開路、短路或者呆滯型等故障。互連測試

2011-09-23 11:44:40

推動電源管理變革的5個趨勢

2021-03-11 07:50:56

本文將介紹電路板系統(tǒng)的芯片到電路板、PCB板內(nèi)互連以及PCB與外部器件之間的三類互連設計的各種技巧,包括器件安裝、布線的隔離以及減少引線電感的措施等,以幫助設計師最大程度降低PCB互連設計中的RF效應。

2019-09-24 06:25:39

(Lorry)如此說道。如果說工業(yè)4.0是一場革命,ADI以μModule技術(shù)為主的高性能電源正在推動基礎技術(shù)變革。作為高端工業(yè)智能領(lǐng)域的高性能模擬器件供應商,ADI 認為未來工業(yè)4.0的設備和裝置

2018-10-30 14:57:33

求總線終端互連總線畫法?

2016-10-26 11:20:30

熱點。01“造車”,百度自動駕駛的一次戰(zhàn)略“大調(diào)整”從行業(yè)來看,自動駕駛的實現(xiàn)主要有三大實現(xiàn)路線,一是以傳統(tǒng)汽車廠商為主的路線,二是特斯拉路線,三是百度和谷歌Waymo為主的高科技路線。以傳統(tǒng)汽車廠商為主導第一種路線,由于利益原因,該路線的推動者始終難以盡全力完成自我“革命”,至多做到“但求..

2021-07-27 08:07:03

[中國,深圳,2021年9月6日]全球光互連技術(shù)革新者——易飛揚(GIGALIGHT)將出席9月15日于北京召開的2021開放數(shù)據(jù)中心峰會。 本屆ODCC以“推動高質(zhì)低碳,筑基美好生活”為大會主題

2021-09-06 14:29:19

,第四次工業(yè)革命什么時候開始?答案已經(jīng)有了。世界經(jīng)濟論壇(WEF)的結(jié)論是,我們可能已經(jīng)進入經(jīng)濟、政治和社會新時代的過渡階段。推動第四次工業(yè)革命的技術(shù)仍處于起步階段,但它們將持續(xù)下去。物聯(lián)網(wǎng): 一個

2019-03-08 11:27:41

最重要的提升帶寬的方法,這也是推動數(shù)據(jù)中心網(wǎng)絡高速發(fā)展的原始動力。隨著物理層單鏈路達到 112Gbps ,數(shù)據(jù)中心網(wǎng)絡將會在絡系統(tǒng)設計、設備整機設計、關(guān)鍵組件設計多個方面面臨巨大的信號完整性的挑戰(zhàn)

2022-09-28 10:43:13

虛擬化是如何推動運營商進行變革的?

2021-05-11 06:29:15

電子元器件和機電部件都有電接點,兩個分立接點之間的電氣連通稱為互連。電子設備必須按照電路原理圖互連,才能實現(xiàn)預定的功能。那么PCB板互連的方式有哪些呢?

2021-03-18 08:19:23

嗨!在vivado 2015.4中,我生成了AXI互連IP核,6個masterand1從站。資源是如此之大約9000片或更多,MIG約3500片。A7 100T共有15850片,沒有什么可供用戶使用!!AXI互連必須使用這么多資源嗎?謝謝

2020-08-13 09:44:55

請問如何推動物聯(lián)網(wǎng)的高能效創(chuàng)新?

2021-06-17 08:57:28

請問技術(shù)創(chuàng)新是如何推動設計工藝發(fā)展的?

2021-04-21 06:46:39

我試圖把一個輸出列勾回到芯片的輸入端,這樣我就可以在不同的行中使用這個信號。我需要通過行來輸出互連,以在行上執(zhí)行塊或塊之間的異或。這阻止了我使用行的廣播特性。我知道無論我選擇輸入輸出互連或反之亦然

2019-03-14 13:12:27

的萌芽。 而如今,我們現(xiàn)在已經(jīng)揭開了第四次工業(yè)革命的序幕,即通過高級集成電路 (IC) 實現(xiàn)機器智能,進而推動整個變革進程。而我們正處于這次革命的風口浪尖,面臨著許多挑戰(zhàn)與機遇。在第四次工業(yè)革命

2018-09-11 14:30:47

IEEE 1394串行接口:IEEE 1394高速串行接口總線是IEEE委員會1995年確認的高速度、低成本串行總線標準,原稱Firewire(火線)。廣泛用于局域多媒體設備互連,如PC、攝象機、錄象機、

2009-08-01 07:56:21 104

104 芯片間的互連速率已經(jīng)達到GHz量級,相比較于低速互連,高速互連的測試遇到了新的挑戰(zhàn)。本文探討了高速互連測試的難點,傳統(tǒng)互連測試方法的不足,進而介紹了互連內(nèi)建自測試(I

2010-07-31 17:00:16 15

15 美信公司的高速互連 (第9版本) 資料,主要內(nèi)容有:

3mm x 3mm串行器支持微型安全攝像機設計 .2吉比特、多端口、LVDS交叉點開關(guān),有效降低系統(tǒng)成本 ...318位、智能型雙

2010-10-02 09:57:57 0

0 針對個人計算機只有1~2個串口,給同時連接多個串口設備進行聯(lián)合測量帶來的不便,提出了一種由多個單片機基于高速同步串行接口(SPI)互連的串口擴展方法。采用此方

2010-12-10 17:35:30 33

33 從嵌入式系統(tǒng)看現(xiàn)代計算機產(chǎn)業(yè)革命

人類近代史上有兩次重大的產(chǎn)業(yè)革命: 一次是18世紀的由蒸汽機推動的第1次產(chǎn)業(yè)革命,另一次是當前人們正面臨著

2009-03-29 15:12:13 386

386 高速串行連接火爆 推動保障性技術(shù)創(chuàng)新和市場發(fā)展

隨著USB和HDMI等等高速串行接口技術(shù)和產(chǎn)品開始向5G等超高傳輸速度方向發(fā)展,與之相配套的相關(guān)技術(shù)的重

2009-12-26 08:37:55 556

556 串行 RapidI 高性能嵌入式互連技術(shù)

摘要

串行RapidIO針對高性能嵌入式系統(tǒng)芯片間和板間互連而設計,它將是未來十幾年中嵌入式系統(tǒng)互連的最佳選擇。

2010-02-25 16:45:04 1022

1022

安捷倫發(fā)布E5071C與TDR相結(jié)合的高速串行互連分析綜合處理方案

安捷倫科技公司宣布推出適用于 Agilent E5071C ENA 網(wǎng)絡分析儀的時域反射(TDR)應用軟件選件。E5071C 與 TDR

2010-03-04 10:14:09 1769

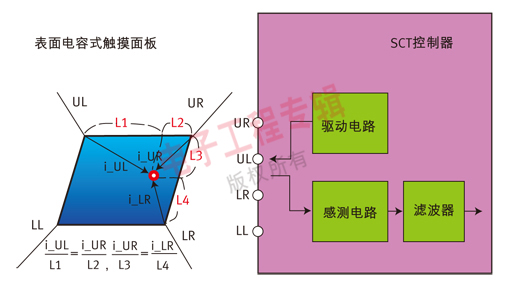

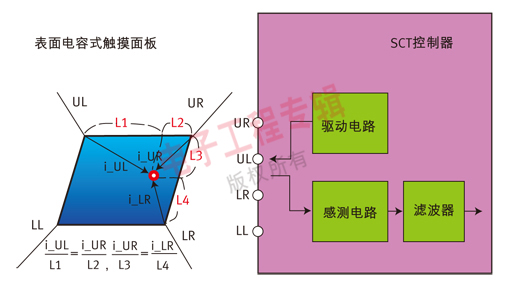

1769 分析:表面電容式觸摸技術(shù)為何能推動人機接口的新革命?

電容式觸摸技術(shù)與目前市場占有率最高的傳統(tǒng)電阻式觸摸技術(shù)相比,為使用者帶來了多項優(yōu)點,包括:高達9

2010-01-04 11:37:00 898

898

高速串行互連是標志并行數(shù)據(jù)總線向串行總線轉(zhuǎn)變的技術(shù)里程碑,這種技術(shù)是減少設計師面臨的信號阻塞問題的方法

2011-05-05 10:57:35 1194

1194

本內(nèi)容介紹了分級環(huán)片上網(wǎng)絡互連

2011-05-19 15:37:33 21

21 OrCAD中如何建立電氣互連,同一個頁面內(nèi)建立互連有兩種方法,使用wire

2011-12-02 10:12:52 6665

6665 基于FPGA的通用高速串行互連協(xié)議設計。

2016-05-11 09:46:01 18

18 光互連的背景 最早提出光互連概念是美國著名光學專家J.W.Goodman先生, 于1984年提出的; 光互連的產(chǎn)生主要源于電子集成電路,由于線寬越來越小、 工作頻率越來越高、互連線密度越來越大、連接

2017-09-19 08:38:48 16

16 摘 要:本文分析了傳統(tǒng)的多個DSP 的各種互聯(lián)的方法,提出將串行RapidIO 協(xié)議,這種基于開關(guān)的、點對點的互連方法作為基帶數(shù)據(jù)處理中的互連方案,可以減少成本,并且提供高帶寬下低延時的雙向通信

2017-10-21 09:29:51 1

1 。隨后業(yè)內(nèi)人士開始探討,企業(yè)是否能以適當?shù)姆绞饺ダ锰摂M現(xiàn)實技術(shù)。

美國汽車巨頭福特已經(jīng)給出了一個明確的答案:是的,虛擬現(xiàn)實技術(shù)能推動汽車設計的革命。

2018-06-02 11:40:00 963

963 貿(mào)澤電子(Mouser Electronics)即日起備貨Molex 的 zCD 互連系統(tǒng)連接器。此款連接器高度集成,具有出眾的性能、耐用性和緊湊的外形尺寸,有助于推動400 Gbps技術(shù)的廣泛應用,可以在電信、網(wǎng)絡和企業(yè)級計算環(huán)境中支持下一代高帶寬以太網(wǎng)應用。

2018-08-10 08:44:00 1078

1078 中國經(jīng)濟已由高速增長階段轉(zhuǎn)向高質(zhì)量發(fā)展階段,高質(zhì)量發(fā)展的微觀基礎是更高質(zhì)量的產(chǎn)品和服務,推動高質(zhì)量發(fā)展對中國制造的品質(zhì)提出了更高要求。黨的十八大以來,習近平總書記多次對中國制造轉(zhuǎn)型升級作出重要論述

2018-12-02 11:03:00 644

644

新浪美股訊據(jù)外媒報道,電動汽車革命即將到來,但它不會由美國來推動,相反,中國將走在前列。從石油燃料汽車到電動汽車的全球交通轉(zhuǎn)型已經(jīng)在中國發(fā)生。

2019-05-16 09:24:09 684

684 電動汽車革命即將到來,但它可能不會由美國來推動,而中國將走在革命道路前列。

2019-05-26 09:02:27 2926

2926

通信帶來根本性的轉(zhuǎn)變。正如蒸汽機、電力和硅引發(fā)了前三次工業(yè)革命,5G技術(shù)將成為推動第四次工業(yè)革命的關(guān)鍵因素。

2019-06-28 08:44:24 2082

2082 5G技術(shù)將會成為推動第四次工業(yè)革命的重要因素。

2019-07-01 11:43:35 1392

1392 電路板系統(tǒng)的互連包括:芯片到電路板、PCB板內(nèi)互連以及PCB與外部器件之間的三類互連。

2019-11-22 17:34:06 1247

1247 以人工智能、大數(shù)據(jù)、機器人等為代表的新技術(shù)推動的第四次工業(yè)革命,正在不斷走向深入,使人類的生產(chǎn)和生活發(fā)生深刻的變化。

2019-09-29 09:45:11 631

631 從第一次工業(yè)革命發(fā)明軋棉機和蒸汽機開始,到第二次工業(yè)革命開發(fā)出裝配線,新技術(shù)的快速采用推動著世界大步向前發(fā)展。

2020-03-01 08:20:00 2155

2155 機器學習、AI和Wi-Fi 6的結(jié)合,將為服務提供商帶來前所未有的能力,從而推動家庭Wi-Fi網(wǎng)絡市場的新革命。

2020-04-05 19:34:36 1966

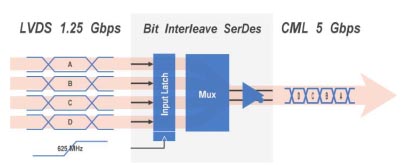

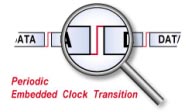

1966 串行互連接口的速率在過去幾年里得到了顯著提高,每線的速率從2.5Gbit/s提高到10Gbit/s,而每個接口可以容納1到32線。8B10B作為互連接口的一種編碼技術(shù),設計簡單、性能出眾,因此成為

2020-04-12 11:06:52 4777

4777

隨著物聯(lián)網(wǎng)推動下一次工業(yè)革命,管理人員可以開始告別停機。

2020-04-28 16:39:30 742

742 智能電網(wǎng)作為新能源變革的核心,從能源開發(fā)方式、能源配置方式、能源消費方式三個方面推動著第三次工業(yè)革命的能源變革。

2020-06-14 09:22:58 560

560 在數(shù)字系統(tǒng)互連設計中,高速串行/O技術(shù)取代傳統(tǒng)的并行/O技術(shù)成為當前發(fā)展的趨勢。與傳統(tǒng)并行丨/技術(shù)相比,串行方案提供了更大的帶寬、更遠的距離、更低的成本和更高的擴展能力,克服了并行l(wèi)/O設計存在的缺陷在實際設計應用中,采用現(xiàn)場可編程門陣列FPGA實現(xiàn)高速串行接口是一種性價比較高的技術(shù)途徑。

2020-08-24 17:28:00 15

15 亞馬遜網(wǎng)絡服務(AWS)看到了機器學習為運輸和物流行業(yè)推動移動革命的四個主要領(lǐng)域。

2020-10-26 12:01:34 2912

2912 具超低靜態(tài)電流的 IC 有效地推動智能可穿戴式設備革命

2021-03-19 11:56:23 12

12 具超低靜態(tài)電流的IC有效地推動智能可穿戴式設備革命概述。

2021-04-09 16:17:50 15

15 工業(yè)革命是技術(shù)和科學交叉推動,科學推動技術(shù),技術(shù)轉(zhuǎn)化為應用,應用對技術(shù)提出要求,技術(shù)要解決問題,又想辦法從科學上來解決,以此循環(huán)。好比,第一次工業(yè)革命是從技術(shù)開始,然后到科學,再到技術(shù)。第二次工業(yè)革命就不一樣了,完全是從科學開始,然后到技術(shù)再到科學。

2022-08-01 16:11:28 1361

1361 RapidIO 與傳統(tǒng)嵌入互連方式的比較 ????隨著高性能嵌入式系統(tǒng)的不斷發(fā)展,芯片間及板間互連對帶寬、成本、靈活性及可靠性的要求越來越高,傳統(tǒng)的互連方式,如處理器總線、PCI總線和以太網(wǎng),都難以

2023-02-02 14:15:05 356

356 封裝互連是指將芯片I/0端口通過金屬引線,金屬凸點等與封裝載體相互連接,實現(xiàn)芯片的功能引出。封裝互連主要包括引線鍵合( Wire Bonding, WB)載帶自動鍵合(Tape Automated Bonding,TAB)和倒裝焊 (Flip Chip Bonding)。

2023-04-03 15:12:20 2882

2882 自第一次工業(yè)革命以來,每次重大技術(shù)革命都會推動人類社會經(jīng)濟飛速增長。新技術(shù)能否引發(fā)新一輪革命的標準在于,能否廣泛應用于生產(chǎn)生活,并解放發(fā)展生產(chǎn)力。

2023-07-24 09:36:15 556

556 銅互連是一種比較新的技術(shù)。在經(jīng)過深入的研究和開發(fā)后,具有銅互連的IC芯片產(chǎn)品第一次在1999年出現(xiàn)。

2023-08-18 09:41:56 652

652

互利共贏共同發(fā)展。華為數(shù)字能源副總裁、首席營銷官方良周應邀出席并發(fā)表“推動能源革命,共建綠色美好未來”的主題演講。 方良周表示,華為融合數(shù)字技術(shù)和電力電子技術(shù),發(fā)展清潔能源與能源數(shù)字化,推動能源革命,共建綠色美好未來

2023-09-27 17:10:07 321

321

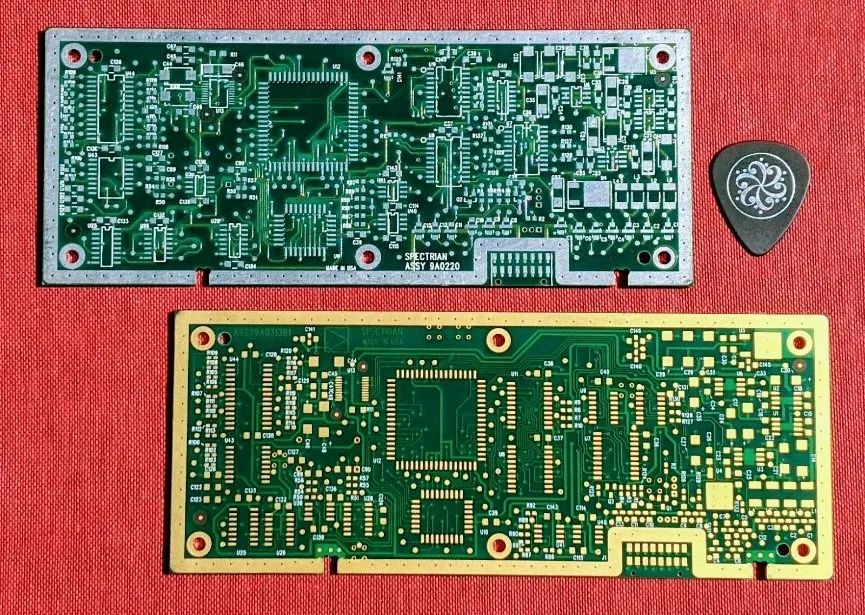

電路板系統(tǒng)的互連包括:芯片到電路板、PCB板內(nèi)互連以及PCB與外部器件之間的三類互連。在RF設計中,互連點處的電磁特性是工程設計面臨的主要問題之一,本文介紹上述三類互連設計的各種技巧,內(nèi)容涉及器件安裝方法、布線的隔離以及減少引線電感的措施等等。

2023-11-16 17:38:23 96

96

高密度互連印刷電路板:如何實現(xiàn)高密度互連 HDI

2023-12-05 16:42:39 227

227

隨著科技的不斷進步,WiFi模塊在醫(yī)療領(lǐng)域的應用正推動著遠程醫(yī)療和健康監(jiān)測的革命。這一技術(shù)的引入不僅提高了醫(yī)療服務的效率,也為患者提供了更為便捷、智能的醫(yī)療體驗。本文將深入探討WiFi模塊如何推動

2024-02-29 15:24:56 185

185

電子發(fā)燒友App

電子發(fā)燒友App

評論