軟件無線電(SDR)在80年代后期,從先進的軍事和智能應用轉向衛星和蜂窩系統,并將成為消費應用的主流,這包括蜂窩無線電基站、新一代數字VHF系統、汽車用多波段AM/FM/XM衛星無線電等。

軟件無線電是信號鏈路部分為軟件的無線電。它具有如下特性:

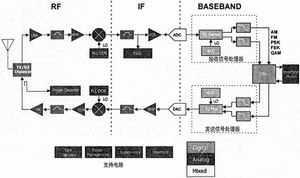

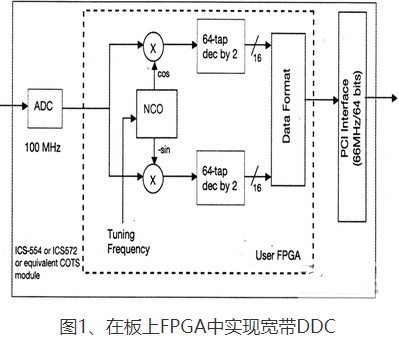

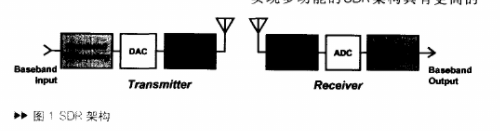

圖1示出一般軟件無線電框圖。

可以用模擬或數字形式實現很多功能,但是要在元件的可用性、復雜性和成本問題折衷考慮選擇方案。

典型的軟件發送器元件包括:

軟件接收器元件包括:

問題是要設計盡可能完善的線性不隨時間變化的發送和接收器硬件,使系統能提供一個“干凈”的輸入信號到數字信號處理硬件,這樣,在軟件控制下一個通用信號鏈路可用于所有工作模式。

也就是說,接收器結構依賴于ADC的選擇,ADC決定可用的動態范圍。

單個ADC可過取樣或欠取樣被調制的信號,在處理中執行下變頻并用4x取樣提供I和Q輸出。

然而,取樣頻率越高,孔經誤差效應就越大,由于時鐘抖動,會影響有效位數。因此,在速度和分辨率間總是存在固有的折衷考慮。

單ADC可在帶數控振蕩器(NCO)的數字下變頻器之后實現如FPGA或接收信號處理器(專用數字芯片)的功能,在信號到達DSP解調前也可濾波和分樣。

圖1 軟件無線電框圖

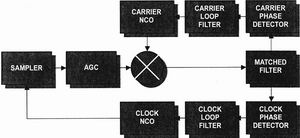

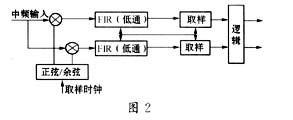

圖2 建立恢復時間、相位和幅度所必須的軟件

相比,用一個帶模擬基帶同相(I)和正交(Q)輸出的模擬解調器減輕ADC上的負擔并允許另外對基帶的無源濾波來降低所需的動態范圍。

其缺點是會導致正交不穩定性,這是由于I和Q通道中相位和幅度失配的原因。也需要兩個匹配的抗混淆濾波器(可加倍做為通道濾波器)和匹配的ADC(或匹配的S/H放大器和單個ADC)。

另一個設計折衷考慮是在模擬和數字濾波之間。無源模擬濾波器具有低互調失真而且不耗電,但它有組合延遲,占有顯著的板空間(特別在低頻)以及要折衷考慮成本、帶寬和Q值。

數字濾波器可設計成具有接近于理想的性能,但也得考慮速度—功率折衷,更多的抽頭或更高的工作頻率需要DSP更高的MIPS、FPGA中專用硬件或接收信號處理器(可提供下變頻、分樣和濾波)。

ADC的動態范圍是模擬和數字濾波之間的基本折衷考慮:模擬濾波更多地降低ADC所需的動態范圍,而且無源濾波器不耗電,而數字濾波器更增加ADC所需的動態范圍,但數字濾波器可具有接近于理想的特性。

對于線性系統,ADC必須適應所有希望的信號加干擾加衰減容限以及自動增益控制(AGC)響應時間。確定ADC動態范圍的計算必須包括:

通常,寬帶接收器比窄帶接收器含有更寬的ADC動態范圍和較小的總增益(~35dB)和較窄的AGC范圍(~10dB)。

系統設計也包括級聯噪聲指數和監聽分析以及頻率規劃。頻率規劃是一種技巧,設計人員必須仔細選擇系統時鐘、中頻和本地振蕩器頻率,使內部和外部干擾最小。

不關注系統時鐘將是不完整的頻率規劃。系統時鐘通常是編碼數據幀率的倍數。往往也是信道間隔的倍數,允許使用整數N鎖相環(PLL)。

一個完整的設計也包括用于最小和最大輸入信號電平的總系統計算,最小輸入信號的一組計算是在AGC關掉無增益降低情況下進行,最大信號電平的一組計算是在AGC完全工作在最大增益降低情況下進行。這也包括最小和最大信號電平的交互調制失真(IMD)效應。

系統設計的一個敏感點是AGC系統。在軟件無線電中,AGC靠降低大信號的增益來保持系統線性度。這樣設置AGC閾值:C/N增加線性度,直到達到最佳C/N為止,然后,降低增益。

所設置的AGC閾值也應使ADC有余量,這樣AGC系統有時間來響應輸入信號的快速變化并避免過載。AGC有兩種基本實現方法:前饋和反饋。

AGC實現

典型的前饋AGC系統用對數放大器測量輸入信號(通常在中頻)并置下游增益來保持在AGC中的恒定信號電平。這是最快的響應系統,但需要定標,這是由于它依賴于對數放大器和可變增益放大器定標因數(dB/v)的精度。

典型的反饋AGC系統對被檢測信號與基準進行比較,并用反饋來保持被檢信號電平恒定。系統應具有快速起動(增益降低)和慢速(增益增大)AGC時間常數。對于穩定的環路它需要線性dB增益。信號通路等待時間可允許接收器被強信號封閉。

例如,用帶峰值檢測器(在IF)的模擬AGC在反饋有效前用幾個周期充電AGC電容器。

用基帶中的檢測器并從I和Q基帶值計算信號電平值,但等待時間比IF所希望AGC的值更壞,特別是在DSP中計算時更是這樣。

在改變頻率時也必須考慮PLL的建立時間,此時間延遲會導致經過系統的等待時間。例如,改變頻率的時間必須包括PLL的建立時間、AGC響應時間、信號從天線到ADC的傳播時間,ADC轉換時間和DSP中信號處理時間。

DSP中相關的解調是最復雜的結構,最好的結構形式示于圖2。

匹配濾波器通常對于二進制相移鍵控(BPSK)和正交相移鍵控(QPSK)分別是最大似然檢測器(MLD)或平方/正交檢測器。若可以處理MLD的額外處理,則低信號跟蹤性能的增益可以是6dB或更高。在很多情況下,由PLL恢復載波和時鐘。

輸入一般為過取樣,并存儲在環形緩沖器中。對此緩沖器的讀標志是經NCO的時鐘環路濾波器的輸出。另外,可以用經過ADC的插入器或直接取樣。

復合混頻器(在基帶)區分正和負頻率。它們也不需要低通濾波來去除混頻分量。混頻器的輸出饋入匹配濾波器單元,此單元采用一個最大的似然檢測器。每個輸入波形用每個可能的輸入波形校正。選擇最大校正做為最類似被接收的波形。

對于包含在存儲器中的波形,如最小鍵移(MSK)、匹配濾波器單元應該用格子結構方法來達到最好誤碼率(BEK)性能。而選擇最大相關,可用每個相關做為Viterbi算法的分支量度。

在選擇逆行程長度時,為了不導致過量延遲進入恢復環路應該小心從事。對于調制需要較長逆行程來講,恢復環路可以用比數據判定更短的逆行程。

載波相位檢測器單元用最類似的基準波形計算關于輸入波形相關相位的微商。這種相位檢測器比傳統的相移鍵控平方環路檢測器好3dB。

環路濾波器單元的階指示環路可以精確恢復的誤差類型。

1階環路對頻率步具有穩態誤差響應。2階環路可以精確地恢復頻率步,但對頻率斜波具有穩態誤差響應。3階環路也用于需要精確頻率斜波恢復的地方,然而,必須小心避免輸入增益不穩定度問題。

類型指示環路中精確積分器數。NCO是1種積分器,而環路濾波器將包含其余部分。

根據缺席規則,1階濾波器是在濾波器中不帶積分器的I型。2階濾波器可以是I型有“漏隙”的積分器或II型“精確”積分器。注意,2階II型在其精確積分器中具有無限大的存儲器,因此,不強迫恢復到零。因此,它必須箱位到最大和最小值。

載波NCO單元產生頻率正比于輸入值的正弦波,可以用內置 sin() 和cos()的C三角函數,但是耗時。可用查表替代相位數字化噪聲耗費的執行速度增加。

時鐘相位檢測器單元的設計取決于調制類型。因為對于匹配濾波器相關的時間導數沒有嚴格形式解,所以時鐘相位檢測器是與調制有關的。

BPSK和頻移鍵控(FSK)解調器一般采用early-late gater技術。這可經過±Ts/2符號變化積分實現。

MSK和連續相位調制形式做為時鐘相位檢測器。這是由于波形是正弦波和時間導數正比于相比導數。

結語

以前,軍事通信系統領域的軟件無線電正在進入主流應用。軟件無線電所帶來相互適用性和能力,使得在不同應用中用軟件更新可增加新的模式。與這種靈活性相伴而來的是復雜的設計問題。

電子發燒友App

電子發燒友App

評論