以下是筆者一些關(guān)于FPGA功耗估計(jì)和如何進(jìn)行低功耗設(shè)計(jì)的知識(shí)。##關(guān)于FPGA低功耗設(shè)計(jì),可從兩方面著手:1)算法優(yōu)化;2)FPGA資源使用效率優(yōu)化。

2014-12-17 09:27:28 9177

9177 應(yīng)用 正如上文所說,正因?yàn)?b class="flag-6" style="color: red">全新Xilinx 7 系列FPGA芯片具備的種種優(yōu)勢,所以它能做到進(jìn)一步拓展FPGA的應(yīng)用領(lǐng)域。其核心市場包括便攜式超聲波設(shè)備、無線基礎(chǔ)設(shè)備和新一代有線換入設(shè)備,新市場則包括

2012-09-21 13:46:16

FPGA(Field Programmable Gate Array)是在PAL、GAL等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了

2021-07-26 06:58:39

是90nm的1.2 V器件,與先前產(chǎn)品相比可降低靜態(tài)和動(dòng)態(tài)功耗,且FPGA制造商采用不同的設(shè)計(jì)技術(shù)進(jìn)一步降低了功耗,平衡了成本和性能。這些90nm器件都改變了門和擴(kuò)散長度,優(yōu)化了所需晶體管的開關(guān)速率

2015-02-09 14:58:01

器件無需外部引導(dǎo)PROM,從而進(jìn)一步節(jié)省了電路板空間,這使得他們成為傳感器接口的具有吸引力的可編程邏輯平臺(tái)。圖像信號(hào)處理(ISP)IP的可用性也使更大型的LatticeXP2器件可提供各種功能,如

2011-05-24 14:17:00

“從絕對市場份額上看,傳統(tǒng)的通信市場仍是低成本FPGA的主要領(lǐng)域。但消費(fèi)電子和汽車應(yīng)用正在快速增長,低成本、低功耗、小體積的FPGA將為這些應(yīng)用提供更強(qiáng)的發(fā)展動(dòng)力。”賽靈思公司(Xilinx)通用

2019-07-22 07:32:26

,半導(dǎo)體技術(shù)將更多晶體管集成到FPGA中,在提高其性能的同時(shí)進(jìn)一步降低自身功耗。那么,DSP又是如何在高性能與低功耗之間尋求最佳平衡點(diǎn)的? FPGA加速滲透 CEVA/德州儀器扛DSP大旗 作為全球

2014-01-09 17:52:31

的終端應(yīng)用的需求。并且,Actel還提供軟件開發(fā)工具和實(shí)時(shí)操作系統(tǒng)的支持,為FPGA設(shè)計(jì)者帶來更多的選擇和靈活性。譚軍最后表示,目前ST等半導(dǎo)體公司已應(yīng)用ARM的Cortex-M3推出MCU,ARM以后會(huì)考慮將Cortex-M3內(nèi)核應(yīng)用于FPGA,從而進(jìn)一步擴(kuò)展ARM核在FPGA的應(yīng)用。

2013-12-25 19:37:36

Array)是在PAL、GAL等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn)。FPGA設(shè)計(jì)不是簡單的芯片研究,主要是利用 FPGA 的模式進(jìn)行其他行業(yè)產(chǎn)品的設(shè)計(jì)

2022-02-23 07:26:05

FPGA的功耗高度依賴于用戶的設(shè)計(jì),沒有哪種單一的方法能夠?qū)崿F(xiàn)這種功耗的降低,在進(jìn)行低功耗器件的設(shè)計(jì)時(shí),人們必須仔細(xì)權(quán)衡性能、易用性、成本、密度以及功率等諸多指標(biāo)。

2019-08-29 07:52:29

FPGA的發(fā)展現(xiàn)狀如何?賽靈思推出的領(lǐng)域目標(biāo)設(shè)計(jì)平臺(tái)如何簡化設(shè)計(jì)、縮短開發(fā)時(shí)間?

2021-04-08 06:18:44

Programmable Gate Array,現(xiàn)場可編程門陣列),它是在 PLA、PAL、GAL、CPLD 等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路...

2021-07-28 08:43:58

Array)是在PAL、GAL等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn)。FPGA設(shè)計(jì)不是簡單的芯片研究,主要是利用 FPGA 的模式進(jìn)行其他行業(yè)產(chǎn)品的設(shè)計(jì)

2022-02-23 06:31:32

目前許多終端市場對可編程邏輯器件設(shè)計(jì)的低功耗要求越來越苛刻。工程師們在設(shè)計(jì)如路由器、交換機(jī)、基站及存儲(chǔ)服務(wù)器等通信產(chǎn)品時(shí),需要密度更大、性能更好的FPGA,但滿足功耗要求已成為非常緊迫的任務(wù)。而在

2019-07-15 08:16:56

增大,FPGA 廠商也正在不斷推出更大型的器件。這些器件能夠集成所有的應(yīng)用,而且與前代器件相比,功耗更低,價(jià)格更具競爭力。這種趨勢意味著可重配置計(jì)算技術(shù)在汽車產(chǎn)業(yè)將會(huì)得到進(jìn)一步推廣和應(yīng)用。 我們推出

2019-07-05 08:34:21

,加速產(chǎn)品上市進(jìn)程,大大降低風(fēng)險(xiǎn) 美國俄勒岡州希爾斯波羅市 — 2015年3月2日 —萊迪思半導(dǎo)體公司(NASDAQ: LSCC)—超低功耗、小尺寸客制化解決方案市場的領(lǐng)導(dǎo)者,今日宣布推出三款可免費(fèi)下載

2019-06-17 05:00:07

描述萊迪思HX4K FPGA 突破這款 FPGA 分線板旨在記錄如何開始 FPGA 編程,從硬件設(shè)計(jì)文件到加載比特流。為了嘗試將其作為一個(gè)項(xiàng)目進(jìn)行訪問,該板的一個(gè)設(shè)計(jì)目標(biāo)是使其能夠僅使用烙鐵進(jìn)行手工

2022-08-23 07:21:04

智能。將SiFive RISC-V實(shí)現(xiàn)與萊迪思低功耗FPGA配合使用可以將易于訪問的嵌入式解決方案推向市場,從而促進(jìn)安全,連接和智能的世界。SiFive和Lattice Semiconductor公司

2020-07-27 17:57:36

、安全的定時(shí)和同步。萊迪思ORAN在現(xiàn)有的控制數(shù)據(jù)安全和低功耗硬件加速功能的基礎(chǔ)上,實(shí)現(xiàn)了符合IEEE(電氣和電子工程師協(xié)會(huì))關(guān)鍵標(biāo)準(zhǔn)和ITU(國際電信聯(lián)盟)規(guī)范的ORAN前傳接口緊密同步,增強(qiáng)了該

2023-03-03 16:52:10

及設(shè)備用電安全的需要,更進(jìn)一步提高電源的可靠性,及時(shí)發(fā)現(xiàn)供電隱患,提高設(shè)備的運(yùn)行壽命,對電源進(jìn)行在線管理已經(jīng)成為普遍的需求。針對早期的UPS電源的RS232標(biāo)準(zhǔn),已經(jīng)無法滿足目前計(jì)算機(jī)硬件及軟件技...

2021-12-28 08:05:27

進(jìn)一步理解量子力學(xué)經(jīng)典理論與應(yīng)用 多方面豐富相關(guān)圖表為了進(jìn)一步深入理解量子力學(xué)理論經(jīng)典及其應(yīng)用,從多個(gè)方面豐富內(nèi)容,附圖頁碼一致,符合國際標(biāo)準(zhǔn)。聲學(xué),聲波自然現(xiàn)象,以及經(jīng)典原子理論的應(yīng)用等對理解量子力學(xué)經(jīng)典之波的概念有益。大灣區(qū)2020-8-2

2020-08-02 07:05:50

適合對C語言有一定基礎(chǔ)積累的童鞋 想進(jìn)一步學(xué)習(xí)C語言的 可以看哈

2012-09-10 22:26:29

MSP430在16位MCU領(lǐng)域低功耗之王的地位,反而將TI在超低功耗的領(lǐng)先地位延伸至32位MCU領(lǐng)域。通過MSP430和MSP432的可擴(kuò)展產(chǎn)品組合,TI的客戶可以根據(jù)應(yīng)用領(lǐng)域和設(shè)計(jì)需求選擇最合適的MCU產(chǎn)品,在不影響用戶體驗(yàn)的情況下集成更多的功能。

2018-05-22 04:57:41

可能性的適應(yīng)各種使用環(huán)境。在近一個(gè)月,生產(chǎn)車間對每個(gè)系列的產(chǎn)品進(jìn)行防水測試,目前從已測試的傳感器中看出傳感器靜止在水中,水完全不會(huì)滲透到里面。那么需要進(jìn)一步需要研究改進(jìn)的是如何使傳感器在運(yùn)行中水不會(huì)附在拉桿上

2019-08-20 16:40:48

有什么方法可以進(jìn)一步降低待機(jī)模式的功耗

2023-10-12 07:23:28

FPGA(Field-Programmable Gate Array),即現(xiàn)場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為專用集成電路(ASIC)領(lǐng)域

2018-08-22 09:40:18

國產(chǎn)有哪些FPGA入門?萊迪思半導(dǎo)體?高云半導(dǎo)體?

2023-12-05 16:05:38

項(xiàng)目名稱:進(jìn)行進(jìn)一步學(xué)習(xí)和研究試用計(jì)劃:此前一直從事單片機(jī)開發(fā),想進(jìn)一步深入學(xué)習(xí)各種MCU,看到有此活動(dòng),特來申請。也為下一步項(xiàng)目無人機(jī)攝像頭驅(qū)動(dòng)選擇合適的芯片。

2020-04-23 10:36:17

【單片機(jī)開發(fā)300問】怎樣進(jìn)一步降低功耗功耗,在電池供電的儀器儀表中是一個(gè)重要的考慮因素。PIC16C××系列單片機(jī)本身的功耗較低(在5V,4MHz振蕩頻率時(shí)工作電流小于2mA)。為進(jìn)一步降低功耗

2011-12-07 13:59:56

器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物, 是作為專用集成電路( ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn)。 簡而言之, FPGA 就是一個(gè)可以

2022-01-25 06:45:52

從Xilinx公司推出FPGA二十多年來,研發(fā)工作大大提高了FPGA的速度和面積效率,縮小了FPGA與ASIC之間的差距,使FPGA成為實(shí)現(xiàn)數(shù)字電路的優(yōu)選平臺(tái)。今天,功耗日益成為FPGA供應(yīng)商及其

2019-09-20 06:33:32

,FPGA能否在以便攜產(chǎn)品為主體的消費(fèi)電子領(lǐng)域占到一席之地呢?對于這個(gè)問題,萊迪思半導(dǎo)體公司給出了肯定的答案。

2019-09-03 07:55:28

初學(xué)linux,安裝了Ubuntu系統(tǒng)界面,請教該如何進(jìn)一步快速學(xué)習(xí),大家有什么好的初學(xué)的資料分享一下,謝謝啦

2015-08-24 18:39:29

完善的配置時(shí)間和“黃金”鏡像更新特性。在該項(xiàng)目成功的基礎(chǔ)之上,我們進(jìn)一步展望下一代賽靈思器件將如何為Anritsu 產(chǎn)品實(shí)現(xiàn)更多功能。例如,大量的功耗預(yù)算被片外 SDRAM 互聯(lián)占用。我們期望研究

2016-07-27 17:14:50

按照您的方式實(shí)現(xiàn)您想要的功能。靈活性——萊迪思FPGA支持各種I/O標(biāo)準(zhǔn),提供連接到各類傳感器、存儲(chǔ)器、儀表板等器件所需的靈活性。使用萊迪思FPGA芯片立即實(shí)現(xiàn)低成本、低功耗的創(chuàng)新。擁有豐富I/O

2019-09-20 15:13:30

在電子系統(tǒng)中,用于連接電路板和各個(gè)模塊之間的連接器不僅價(jià)格昂貴而且占據(jù)了電路板和系統(tǒng)的寶貴空間,并且它們還會(huì)降低產(chǎn)品的穩(wěn)定性。萊迪思開發(fā)了一種創(chuàng)新的方法,讓系統(tǒng)架構(gòu)師和開發(fā)人員使用尺寸極小的低功耗

2020-10-23 09:16:56

在電子系統(tǒng)中,用于連接電路板和各個(gè)模塊之間的連接器不僅價(jià)格昂貴而且占據(jù)了電路板和系統(tǒng)的寶貴空間,并且它們還會(huì)降低產(chǎn)品的穩(wěn)定性。萊迪思開發(fā)了一種創(chuàng)新的方法,讓系統(tǒng)架構(gòu)師和開發(fā)人員使用尺寸極小的低功耗

2021-05-25 14:36:00

blocks to receive and transmit HDMI sources. 對于這種應(yīng)用,萊迪思半導(dǎo)體提供了基本的組成部件,用于接收和發(fā)送HDMI信號(hào)源。 本文小結(jié) FPGA 提供了一個(gè)

2019-06-05 05:00:17

)進(jìn)行訓(xùn)練和分類。 隨著數(shù)據(jù)量的進(jìn)一步增加,機(jī)器學(xué)習(xí)將轉(zhuǎn)移到云。大型機(jī)器學(xué)習(xí)模式實(shí)現(xiàn)在云端的 CPU 上。盡管 GPU 對深度學(xué)習(xí)算法而言在性能方面是一種更好的選擇,但功耗要求之高使其只能用于高性能

2019-06-19 07:24:41

(使用FPGA引腳和DAC)任何人都可以給出一些答案如何進(jìn)一步使用以上兩個(gè)文件查看DSO上的輸出 提前感謝你Counter.v 3 KB以上來自于谷歌翻譯以下為原文Hello to all

2019-07-03 08:41:24

各位大俠好,最近公司要求將CC2640R2模塊的功耗進(jìn)一步縮減,我應(yīng)公司要求做了一個(gè)最簡電路,目前外圍電阻、電位器、LED等繁雜的元件已盡數(shù)砍掉,現(xiàn)在測量出僅中心的綠板CC2640R2模塊待機(jī)功耗在

2019-10-21 10:02:32

如何進(jìn)一步加強(qiáng)對RFID的安全隱私保護(hù)?

2021-05-26 06:09:27

GN1302 晶振引腳連接 2 個(gè) 30pf 電容,每天大約慢 4 秒,如何進(jìn)一步提高精度?時(shí)鐘每天慢 4 秒是因?yàn)榫д竦耐獠控?fù)載電容過大,即 30pf 電容過大。如果使用的晶振的負(fù)載電容參數(shù)為

2022-12-29 17:36:43

和實(shí)時(shí)處理的要求。低功耗、小尺寸的ECP5 FPGA系列可用作應(yīng)用處理器的協(xié)處理器,在網(wǎng)絡(luò)邊緣實(shí)現(xiàn)系統(tǒng)所需的高效實(shí)時(shí)處理功能。除了上文中提到的ISP外,ECP5 FPGA還可以實(shí)現(xiàn)視頻分析功能,進(jìn)一步減輕

2020-10-21 11:53:02

復(fù)雜器件專業(yè)技術(shù)相結(jié)合,將為系統(tǒng)供應(yīng)商提供低功耗的芯片方案,供他們在此基礎(chǔ)上持續(xù)提高帶寬容量,并完成更智能的處理。此外,TPACK提供的芯片解決方案可以導(dǎo)入到最新的FPGA中,進(jìn)一步降低功耗。最終實(shí)現(xiàn)

2019-07-31 07:13:26

全球可編程邏輯解決方案領(lǐng)導(dǎo)廠商賽靈思公司 (Xilinx Inc.) 宣布,為推進(jìn)可編程勢在必行之必然趨勢,正對系統(tǒng)工程師在全球發(fā)布賽靈思新一代可編程FPGA平臺(tái)。和前代產(chǎn)品相比,全新的平臺(tái)功耗降低

2019-08-09 07:27:00

如何讓計(jì)算機(jī)視覺更進(jìn)一步接近人類視覺?

2021-06-01 06:27:08

本文以嵌入式實(shí)時(shí)操作系統(tǒng)μC/OS-II在飛思卡爾8位單片機(jī)HCS08GT60上的移植為例,詳細(xì)討論如何利用μC/OS-II給出的內(nèi)核擴(kuò)展接口,實(shí)現(xiàn)一個(gè)低功耗的嵌入式實(shí)時(shí)系統(tǒng);進(jìn)一步分析如何選擇一種合適的低功耗模式。

2021-04-27 06:26:49

傳感器為震動(dòng)速度傳感器,待提取信號(hào)頻率0.1~200Hz ,幅度幾十uV,原來采用AD620放大,現(xiàn)在希望進(jìn)一步降低功耗與噪聲,采用什么片子好?

2018-10-25 09:25:24

說至關(guān)重要。圖10:基于iCE40 UltraPlus FPGA的sensAI會(huì)預(yù)處理傳感器數(shù)據(jù)以判斷該數(shù)據(jù)是否需要發(fā)送到SoC作進(jìn)一步處理結(jié)語:萊迪思的FPGA具有獨(dú)特的優(yōu)勢,可以滿足網(wǎng)絡(luò)邊緣設(shè)備

2020-10-23 11:43:04

(RF)通信能力進(jìn)入了一個(gè)新時(shí)代。新型 MSP430FR57xx FRAM 系列的面市進(jìn)一步彰顯了 TI 在嵌入式處理技術(shù)領(lǐng)域的領(lǐng)先地位,與基于閃存和 EEPROM 的微控制器相比,該 FRAM 系列可

2011-05-04 16:37:37

在過去的幾年間,FPGA技術(shù)備受矚目,而快閃FPGA的出現(xiàn)無疑引發(fā)FPGA領(lǐng)域的一場革命,推動(dòng)了FPGA的進(jìn)一步飛躍。由于PPGA的特性主要由其使用的可編程技術(shù)來決定,相對于SRAM FPGA,快閃FPGA具有更好的非易失性,這使其成為FPGA設(shè)計(jì)的更好的選擇。

2019-08-05 07:59:59

網(wǎng)絡(luò)時(shí)間協(xié)議NTP是什么意思?NTP授時(shí)的原理是什么?怎樣去進(jìn)一步提高NTP的授時(shí)精度呢?

2021-11-01 07:12:40

、電視手機(jī)。這些采用多種RF技 術(shù)的手機(jī)在提供便利的同時(shí)也使得手機(jī)的設(shè)計(jì)變得復(fù)雜,如何進(jìn)一步集成射頻元件也變得至關(guān)重要。

2019-08-27 08:33:19

日前,Altium 宣布推出另一款面向桌面 NanoBoard 可重構(gòu)硬件開發(fā)平臺(tái)的全新子板,進(jìn)一步幫助電子設(shè)計(jì)人員輕松利用可編程硬件的優(yōu)勢。這款最新插入式子板采用 780 BGA 封裝,內(nèi)置

2019-07-25 06:07:43

專家進(jìn)行探討交流的機(jī)會(huì),提高對技術(shù)知識(shí)的應(yīng)用和產(chǎn)品商業(yè)化的認(rèn)知;為廣大電子愛好者深入了解賽靈思產(chǎn)品的機(jī)會(huì),利用賽靈思FPGA器件,開發(fā)設(shè)計(jì)產(chǎn)品,進(jìn)一步提高FPGA設(shè)計(jì)能力和水平。 大賽參與情況

2012-09-06 11:54:16

了最新XENSIV? MEMS麥克風(fēng)產(chǎn)品,一款超低功耗的數(shù)字麥克風(fēng)IM69D128S。這款麥克風(fēng)專為需要高信噪比(SNR)/低自噪聲、持久的電池續(xù)航能力和高可靠性的應(yīng)用而設(shè)計(jì)。在不影響電池續(xù)航能力的前提下,其

2023-03-03 16:53:59

如何進(jìn)一步減小DTC控制系統(tǒng)的轉(zhuǎn)矩脈動(dòng)?

2023-10-18 06:53:31

自適應(yīng)和智能計(jì)算的全球領(lǐng)先企業(yè)賽靈思公司(Xilinx, Inc.,(NASDAQ:XLNX))今天宣布推出全球最大容量的 FPGA – Virtex UltraScale+ VU19P,從而進(jìn)一步

2020-11-02 08:34:50

。這是雙方工程團(tuán)隊(duì)為進(jìn)一步提升良率、增強(qiáng)可靠性并縮短生產(chǎn)周期而努力合作的成果。Virtex-6系列通過生產(chǎn)驗(yàn)證,意味著聯(lián)華電【關(guān)鍵詞】:生產(chǎn)驗(yàn)證,高性能,電子,可靠性,生產(chǎn)周期,系列,制造工藝,生產(chǎn)

2010-04-24 09:06:05

本帖最后由 曾12345 于 2018-5-23 15:49 編輯

全新的毫瓦級(jí)功耗FPGA解決方案為機(jī)器學(xué)習(xí)推理在大眾市場物聯(lián)網(wǎng)應(yīng)用中實(shí)現(xiàn)快速部署創(chuàng)造機(jī)遇。1. 將AI加速部署到快速增長

2018-05-23 15:31:04

難度,但是接口帶寬還是略顯局促。另外,在價(jià)格和功耗方面也需較大的改進(jìn)。” 英特爾對此回應(yīng)表示,該SoC的性能完全可以滿足我們目前所涉及的市場領(lǐng)域客戶的設(shè)計(jì)需求。當(dāng)然,針對未來的需求,還會(huì)進(jìn)一步完善

2011-07-21 10:52:00

)

FPGA設(shè)計(jì)是可移植的,使人們關(guān)注的產(chǎn)品使用壽命得到最大限度延長。大多數(shù)DVI器件是針對基于PC的應(yīng)用,通常這些接口適合

進(jìn)一步集成至其他的ASSP。這種情況發(fā)生時(shí),這些分立器件或許不再可用,因?yàn)橹圃焐?/div>

2019-06-06 05:00:34

全球領(lǐng)先的中文互聯(lián)網(wǎng)搜索引擎提供商百度正在采用賽靈思FPGA加速其中國數(shù)據(jù)中心的機(jī)器學(xué)習(xí)應(yīng)用。兩家公司正合作進(jìn)一步擴(kuò)大FPGA加速平臺(tái)的部署規(guī)模。新興應(yīng)用的快速發(fā)展正日漸加重計(jì)算工作的負(fù)載,數(shù)據(jù)中心

2016-12-15 17:15:52

帶來領(lǐng)先的低功耗架構(gòu)、小尺寸和高性能優(yōu)勢。萊迪思Avant-E FPGA系列旨在解決客戶在網(wǎng)絡(luò)邊緣面臨的關(guān)鍵挑戰(zhàn),包括汽車應(yīng)用。在汽車世界大會(huì)上,我們展示了首款基于萊迪思Avant-E FPGA、運(yùn)行

2023-02-21 13:40:29

飛思卡爾產(chǎn)品的應(yīng)用領(lǐng)域飛思卡爾的市場領(lǐng)先地位

2021-02-19 07:20:07

降低成本。物聯(lián)網(wǎng)將進(jìn)一步增加共享、處理和存儲(chǔ)的“大數(shù)據(jù)”的絕對數(shù)量。顯然,Achronix關(guān)注到了“高帶寬+聯(lián)網(wǎng)”在未來產(chǎn)品戰(zhàn)略的重要性,并制定相當(dāng)明智的決策,以應(yīng)對全球及中國的巨大市場需求,勇于挑戰(zhàn)

2013-05-07 15:05:03

Altera增強(qiáng)MAX II系列,進(jìn)一步拓展其CPLD應(yīng)用

Altera公司宣布,提供工業(yè)級(jí)溫度范圍以及功耗更低的MAX IIZ器件,從而進(jìn)一步增強(qiáng)了MAX II CPLD系列。MAX IIZ CPLD完美的結(jié)合了邏輯

2009-11-05 09:53:58 1283

1283 具有低功耗意識(shí)的FPGA設(shè)計(jì)方法

ILGOO系列低功耗FPGA產(chǎn)品

Actel公司的ILGOO系列器件是低功耗FPGA產(chǎn)品,是在便攜式產(chǎn)品設(shè)計(jì)中替代ASIC和CPLD的最

2009-11-26 09:41:19 676

676

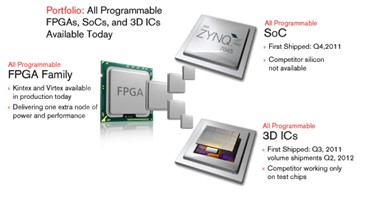

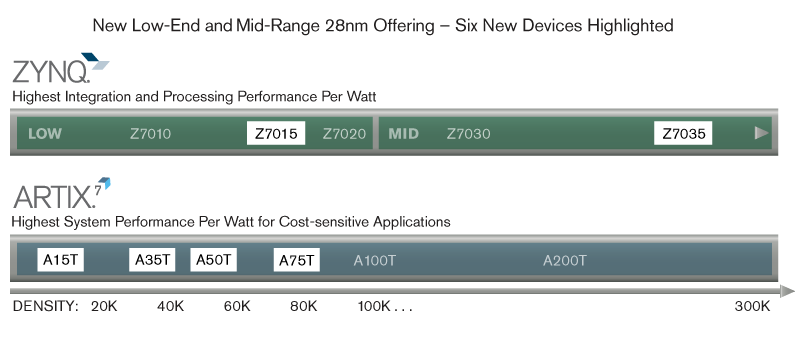

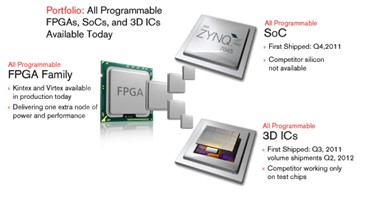

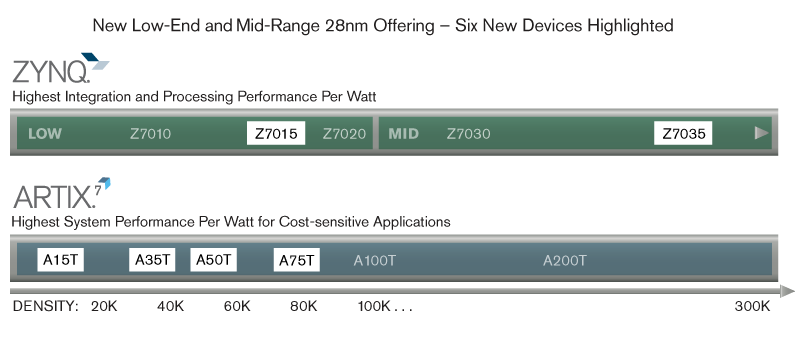

電子發(fā)燒友網(wǎng)核心提示 :賽靈思28nm,實(shí)現(xiàn)了超越一代的領(lǐng)先地位。其產(chǎn)品組合 All Programmable FPGA、SoC 和 3D IC 現(xiàn)已開始供貨;在性能、功耗和集成度上該產(chǎn)品組合有著重大突破;此外,

2012-09-28 17:23:17 612

612

)推出Design Compiler系列的全新RTL Synthesis產(chǎn)品Design Compiler NXT,進(jìn)一步擴(kuò)大了Design Compiler Graphical的市場領(lǐng)先地位

2018-11-14 17:50:01 220

220 持續(xù)創(chuàng)新 28HPL 高性能低功耗工藝,成就跨越全新中低端器件,和 Artix-7 FPGA、Kintex-7 FPGA 及 Zynq-7000 SoC 產(chǎn)品系列的全新低功耗工業(yè)速度等級(jí)的器件敬請

2019-08-01 09:07:32 3066

3066

2019 年 12 月 10 日——萊迪思半導(dǎo)體公司(NASDAQ:LSCC),低功耗可編程器件的領(lǐng)先供應(yīng)商,今日宣布推出全新低功耗 FPGA 技術(shù)平臺(tái)——Lattice Nexus?。該技術(shù)平臺(tái)

2019-12-11 15:05:51 899

899 2019 年 12 月 10 日——萊迪思半導(dǎo)體公司(NASDAQ:LSCC),低功耗可編程器件的領(lǐng)先供應(yīng)商,今日宣布推出首款基于萊迪思 Nexus? FPGA 技術(shù)平臺(tái)的產(chǎn)品

2019-12-11 15:09:56 711

711 低功耗FPGA大廠萊迪思半導(dǎo)體(Lattice Semiconductor)近日推出全新FPGA軟件解決方案Lattice Propel,提供擴(kuò)充RISC-V IP及更多類型周邊組件的IP

2020-07-14 16:36:17 1156

1156 除了支持全新的制造平臺(tái),萊迪思還依托其低功耗、小尺寸 FPGA 領(lǐng)先開發(fā)商的行業(yè)經(jīng)驗(yàn),在系統(tǒng)設(shè)計(jì)的各個(gè)層面(從完善的系統(tǒng)解決方案到 FPGA 架構(gòu),再到電路)取得創(chuàng)新,進(jìn)一步降低功耗,減小 FPGA 尺寸,同時(shí)提升系統(tǒng)性能。全新的制造工藝與多個(gè)層面的創(chuàng)新催生了萊迪思 Nexus? FPGA 開發(fā)平臺(tái)。

2020-08-10 16:41:34 390

390 的功耗高度依賴于用戶的設(shè)計(jì),沒有哪種單一的方法能夠?qū)崿F(xiàn)這種功耗的降低。目前許多終端市場對可編程邏輯器件設(shè)計(jì)的低功耗要求越來越苛刻。在消費(fèi)電子領(lǐng)域,OEM希望采用FPGA的設(shè)計(jì)能夠?qū)崿F(xiàn)與ASIC相匹敵的低功耗。 盡管基于90nm工藝的FPGA的功耗已低

2020-10-28 15:02:13 2498

2498 的功耗高度依賴于用戶的設(shè)計(jì),沒有哪種單一的方法能夠?qū)崿F(xiàn)這種功耗的降低。目前許多終端市場對可編程邏輯器件設(shè)計(jì)的低功耗要求越來越苛刻。在消費(fèi)電子領(lǐng)域,OEM希望采用FPGA的設(shè)計(jì)能夠?qū)崿F(xiàn)與ASIC相匹敵的低功耗。 盡管基于90nm工藝的FPGA的功耗已低

2020-10-26 18:51:16 2583

2583 憑借萊迪思Avant平臺(tái),我們將鞏固在低功耗FPGA行業(yè)的領(lǐng)導(dǎo)地位,有助于我們持續(xù)快速創(chuàng)新,將我們產(chǎn)品的潛在市場擴(kuò)大一倍。我們開發(fā)Avant 是為了滿足客戶對優(yōu)質(zhì)中端FPGA解決方案的需求,我們很高興能幫助他們以更低功耗和更強(qiáng)性能加速設(shè)計(jì)。

2022-12-07 16:01:35 546

546 電子發(fā)燒友網(wǎng)報(bào)道(文/黃晶晶)三年前萊迪思推出NEXUS系列FPGA,以低功耗、超小尺寸、質(zhì)量穩(wěn)定可靠以及不斷的產(chǎn)品迭代創(chuàng)新獲得認(rèn)可,廣泛應(yīng)用于工業(yè)、通信、汽車、數(shù)據(jù)中心等領(lǐng)域。最近,萊迪思重磅發(fā)布

2022-12-12 14:31:10 2078

2078

隨著Avant平臺(tái)的推出,萊迪思為市場注入了新的可能性。萊迪思Avant旨在將行業(yè)領(lǐng)先的低功耗、小尺寸和高性能優(yōu)勢引入中端FPGA。

2022-12-30 12:26:20 340

340 與現(xiàn)有的中端FPGA相比,得益于專為低功耗設(shè)計(jì)的可編程結(jié)構(gòu)、功耗優(yōu)化的嵌入式存儲(chǔ)器和DSP、低功耗高性能SERDES與I/O設(shè)計(jì)、內(nèi)置協(xié)議邏輯等全方位優(yōu)化措施,Avant系列產(chǎn)品的功耗比同類競品器件低2.5倍。

2023-01-04 11:32:11 343

343 萊迪思憑借MachXO系列FPGA在控制功能方面長期處于領(lǐng)先地位。這些FPGA為當(dāng)今數(shù)據(jù)中心、通信基礎(chǔ)設(shè)施和工業(yè)系統(tǒng)不斷增長的計(jì)算需求提供了理想的低功耗解決方案。

2023-04-25 14:46:52 207

207

已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評論