我們生活已經(jīng)離不開網(wǎng)絡(luò),而網(wǎng)絡(luò)能順利通信,離不開其中的PHY、MAC。

本文主要介紹以太網(wǎng)的MAC(Media Access Control,即媒體訪問控制子層協(xié)議)和PHY(物理層)之間的MII(Media Independent Interface ,媒體獨立接口),以及MII的各種衍生版本——GMII、SGMII、RMII、RGMII等。

簡介

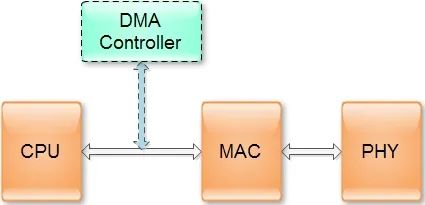

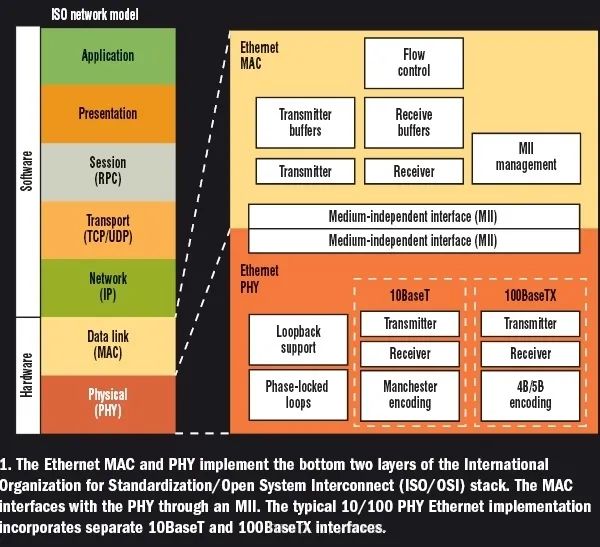

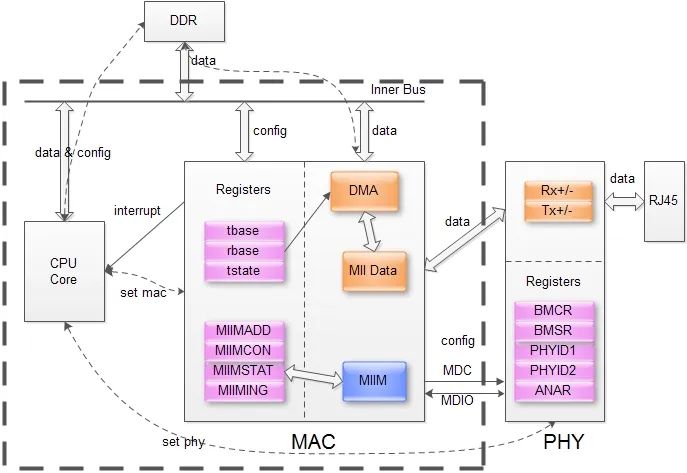

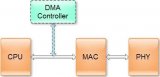

從硬件的角度看,以太網(wǎng)接口電路主要由MAC(Media Access Control)控制器和物理層接口PHY(Physical Layer,PHY)兩大部分構(gòu)成。如下圖所示:

DMA控制器通常屬于CPU的一部分,用虛線放在這里是為了表示DMA控制器可能會參與到網(wǎng)口數(shù)據(jù)傳輸中。

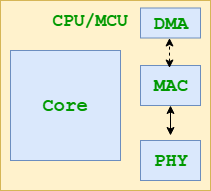

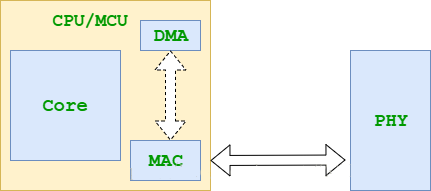

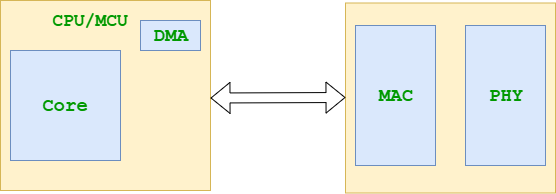

但是,在實際的設(shè)計中,以上三部分并不一定獨立分開的。由于,PHY整合了大量模擬硬件,而MAC是典型的全數(shù)字器件。考慮到芯片面積及模擬/數(shù)字混合架構(gòu)的原因,通常,將MAC集成進(jìn)微控制器而將PHY留在片外。更靈活、密度更高的芯片技術(shù)已經(jīng)可以實現(xiàn)MAC和PHY的單芯片整合。可分為下列幾種類型:

CPU集成MAC與PHY。目前來說并不多見

CPU集成MAC,PHY采用獨立芯片。比較常見

CPU不集成MAC與PHY,MAC與PHY采用集成芯片。比較常見

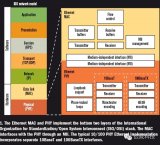

MAC及PHY工作在OSI七層模型的數(shù)據(jù)鏈路層和物理層。具體如下:

什么是MAC

MAC(Media Access Control)即媒體訪問控制子層協(xié)議。

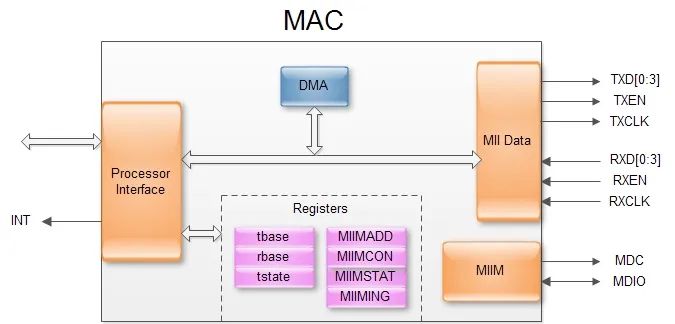

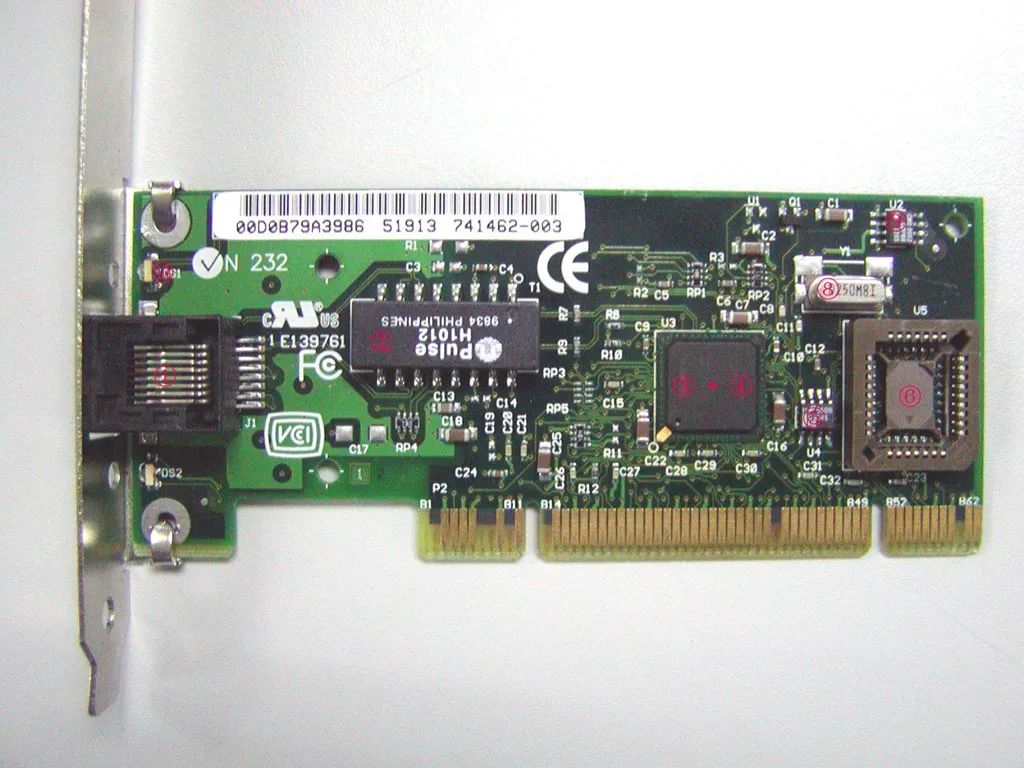

該部分有兩個概念:MAC可以是一個硬件控制器 及 MAC通信以協(xié)議。該協(xié)議位于OSI七層協(xié)議中數(shù)據(jù)鏈路層的下半部分,主要負(fù)責(zé)控制與連接物理層的物理介質(zhì)。MAC硬件大約就是下面的樣子了:

在發(fā)送數(shù)據(jù)的時候,MAC協(xié)議可以事先判斷是否可以發(fā)送數(shù)據(jù),如果可以發(fā)送將給數(shù)據(jù)加上一些控制信息,最終將數(shù)據(jù)以及控制信息以規(guī)定的格式發(fā)送到物理層。

在接收數(shù)據(jù)的時候,MAC協(xié)議首先判斷輸入的信息并是否發(fā)生傳輸錯誤,如果沒有錯誤,則去掉控制信息發(fā)送至LLC(邏輯鏈路控制)層。該層協(xié)議是以太網(wǎng)MAC由IEEE-802. 3以太網(wǎng)標(biāo)準(zhǔn)定義。

以太網(wǎng)數(shù)據(jù)鏈路層其實包含MAC(介質(zhì)訪問控制)子層和LLC(邏輯鏈路控制)子層。一塊以太網(wǎng)卡MAC芯片的作用不但要實現(xiàn)MAC子層和LLC子層的功能,還要提供符合規(guī)范的PCI界面以實現(xiàn)和主機的數(shù)據(jù)交換。

MAC從PCI總線收到IP數(shù)據(jù)包(或者其他網(wǎng)絡(luò)層協(xié)議的數(shù)據(jù)包)后,將之拆分并重新打包成最大1518Byte、最小64Byte的幀。

這個幀里面包括了目標(biāo)MAC地址、自己的源MAC地址和數(shù)據(jù)包里面的協(xié)議類型(比如IP數(shù)據(jù)包的類型用80表示,最后還有一個DWORD(4Byte)的CRC碼。

可是目標(biāo)的MAC地址是哪里來的呢?

這牽扯到一個ARP協(xié)議(介乎于網(wǎng)絡(luò)層和數(shù)據(jù)鏈路層的一個協(xié)議)。第一次傳送某個目的IP地址的數(shù)據(jù)的時候,先會發(fā)出一個ARP包,其MAC的目標(biāo)地址是廣播地址,里面說到:“誰是xxx.xxx.xxx.xxx這個IP地址的主人?”

因為是廣播包,所有這個局域網(wǎng)的主機都收到了這個ARP請求。收到請求的主機將這個IP地址和自己的相比較,如果不相同就不予理會,如果相同就發(fā)出ARP響應(yīng)包。

這個IP地址的主機收到這個ARP請求包后回復(fù)的ARP響應(yīng)里說到:“我是這個IP地址的主人”。這個包里面就包括了他的MAC地址。以后的給這個IP地址的幀的目標(biāo)MAC地址就被確定了。(其它的協(xié)議如IPX/SPX也有相應(yīng)的協(xié)議完成這些操作)。

IP地址和MAC地址之間的關(guān)聯(lián)關(guān)系保存在主機系統(tǒng)里面,叫做ARP表。由驅(qū)動程序和操作系統(tǒng)完成。

在Microsoft的系統(tǒng)里面可以用arp-a 的命令查看ARP表。收到數(shù)據(jù)幀的時候也是一樣,做完CRC校驗以后,如果沒有CRC效驗錯誤,就把幀頭去掉,把數(shù)據(jù)包拿出來通過標(biāo)準(zhǔn)的接口傳遞給驅(qū)動和上層的協(xié)議棧。最終正確的達(dá)到我們的應(yīng)用程序。

還有一些控制幀,例如流控幀也需要MAC直接識別并執(zhí)行相應(yīng)的行為。

以太網(wǎng)MAC芯片的一端接計算機PCI總線,另外一端就接到PHY芯片上,它們之間是通過MII接口鏈接的。

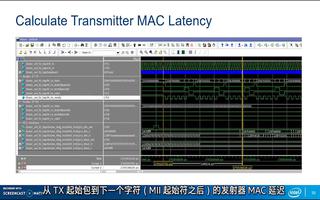

一個MAC的結(jié)構(gòu)圖如下圖所示:

什么是PHY

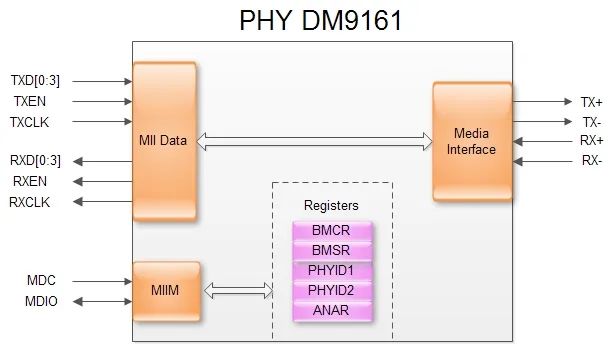

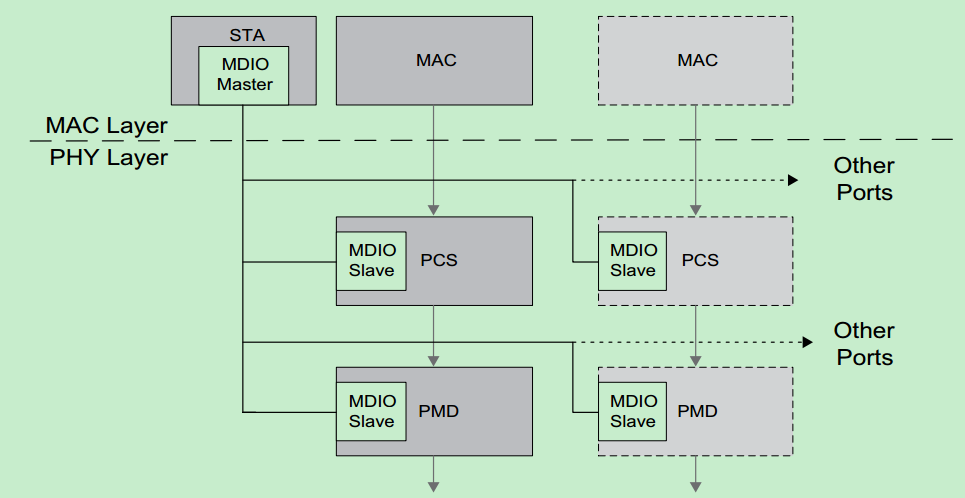

PHY((Physical Layer,PHY))是IEEE802.3中定義的一個標(biāo)準(zhǔn)模塊,STA(station management entity,管理實體,一般為MAC或CPU)通過SMI(Serial Manage Interface)對PHY的行為、狀態(tài)進(jìn)行管理和控制,而具體管理和控制動作是通過讀寫PHY內(nèi)部的寄存器實現(xiàn)的。一個PHY的基本結(jié)構(gòu)如下圖:

PHY是物理接口收發(fā)器,它實現(xiàn)OSI模型的物理層。

IEEE-802.3標(biāo)準(zhǔn)定義了以太網(wǎng)PHY。包括MII/GMII(介質(zhì)獨立接口)子層、PCS(物理編碼子層)、PMA(物理介質(zhì)附加)子層、PMD(物理介質(zhì)相關(guān))子層、MDI子層。它符合IEEE-802.3k中用于10BaseT(第14條)和100BaseTX(第24條和第25條)的規(guī)范。

注:PHY寄存器在IEEE802.3標(biāo)準(zhǔn)的 22.2.4 Management functions 節(jié)有介紹,但不涉及所有的寄存器,個別寄存器需要到其它章節(jié)中看,當(dāng)然,文檔里面也提到該在哪里找到哪個寄存器。

什么是MII

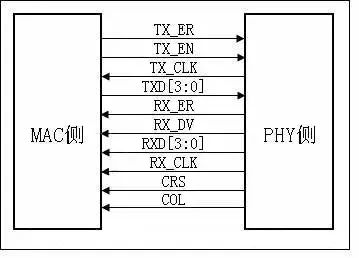

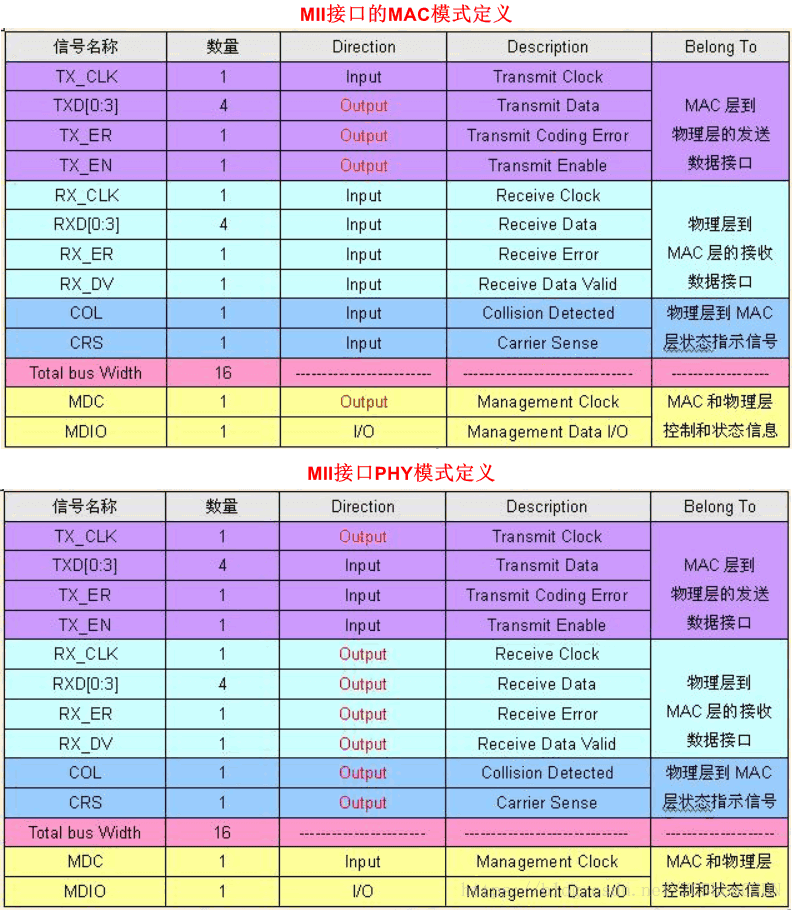

MII(Media Independent Interface)即媒體獨立接口,MII 接口是 MAC 與 PHY 連接的標(biāo)準(zhǔn)接口。它是 IEEE-802.3 定義的以太網(wǎng)行業(yè)標(biāo)準(zhǔn)。MII 接口提供了 MAC 與 PHY 之間、PHY 與 STA(Station Management)之間的互聯(lián)技術(shù),該接口支持 10Mb/s 與 100Mb/s 的數(shù)據(jù)傳輸速率,數(shù)據(jù)傳輸?shù)奈粚挒?4 位。MII 接口如下圖所示:

“媒體獨立” 表明在不對 MAC 硬件重新設(shè)計或替換的情況下,任何類型的 PHY 設(shè)備都可以正常工作。802.3 協(xié)議最多支持 32 個 PHY,但有一定的限制:要符合協(xié)議要求的 connector 特性。此外,提到 MII,就有可能涉及到 RS,PLS,STA 等名詞術(shù)語,下面講一下他們之間對應(yīng)的關(guān)系。

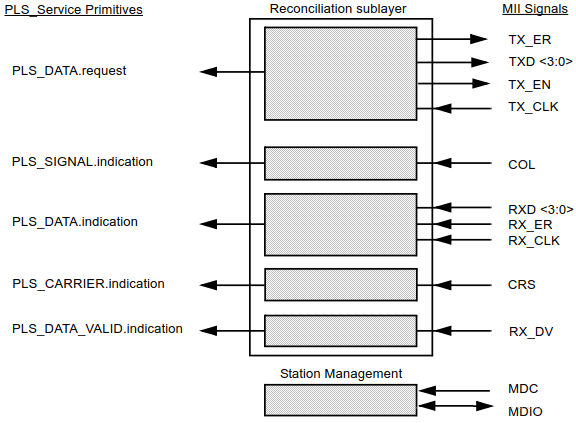

所謂 RS 即 Reconciliation sublayer,它的主要功能主要是提供一種 MII 和 MAC/PLS 之間的信號映射機制。它們(RS 與 MII)之間的關(guān)系如下圖:

MII的Management Interface是與STA(Station Management)相連的。

注:關(guān)于本節(jié),具體可參考IEEE以太網(wǎng)標(biāo)準(zhǔn)802.3的22.3 Signal timing characteristics節(jié),其中包含時鐘信號等更詳細(xì)內(nèi)容。

MII接口主要包括四個部分。一是從MAC層到PHY層的發(fā)送數(shù)據(jù)接口,二是從PHY層到MAC層的接收數(shù)據(jù)接口,三是從PHY層到MAC層的狀態(tài)指示信號,四是MAC層和PHY層之間傳送控制和狀態(tài)信息的MDIO接口。

MII 包括一個數(shù)據(jù)接口,以及一個 MAC 和 PHY 之間的管理接口:

數(shù)據(jù)接口: 包括分別用于發(fā)送器和接收器的兩條獨立信道。每條信道都有自己的數(shù)據(jù)、時鐘和控制信號。MII 數(shù)據(jù)接口總共需要 16 個信號,包括

TX_ER(transmit coding error): TX_ER 同步于 TX_CLK,在數(shù)據(jù)傳輸過程中,如果 TX_ER 有效超過一個時鐘周期,并且此時TX_EN 是有效的,則數(shù)據(jù)通道中傳輸?shù)臄?shù)據(jù)是無效的,沒用的。注:當(dāng) TX_ER 有效并不影響工作在 10Mb/s 的 PHY 或者 TX_EN 無效時的數(shù)據(jù)傳輸。在 MII 接口的連線中,如果 TX_ER 信號線沒有用到,必須將它下拉接地。

TXD<3:0>(transmit data): TXD 由 RS 驅(qū)動,同步于 TX_CLK,在 TX_CLK 的時鐘周期內(nèi),并且TX_EN 有效,TXD 上的數(shù)據(jù)被 PHY 接收,否則 TXD 的數(shù)據(jù)對 PHY 沒有任何影響。

TX_EN: 發(fā)送使能。TX_EN 由 Reconciliation 子層根據(jù) TX_CLK 上升沿同步進(jìn)行轉(zhuǎn)換。

TX_CLK(transmit clock): TX_CLK (Transmit Clock) 是一個連續(xù)的時鐘信號(即系統(tǒng)啟動,該信號就一直存在),它是 TX_EN、TXD、TX_ER(信號方向為從 RS 到 PHY)的參考時鐘,TX_CLK 由 PHY 驅(qū)動 TX_CLK 的時鐘頻率是數(shù)據(jù)傳輸速率的 25%,偏差 ±100ppm。例如,100Mb/s 模式下,TX_CLK 時鐘頻率為 25MHz,占空比在 35% 至 65% 之間。

COL(collision detected): COL 不需要同步于參考時鐘。The behavior of the COL signal is unspecified when the duplex mode bit0.8 inthe control register is set to a logic one(自動協(xié)商禁止,人工設(shè)為全雙工模式), or when the Auto-Negotiation process selects a full duplex mode of operation。即半雙工模式信號有效,全雙工模式信號無效。

RXD<3:0>(receive data): RXD由RS驅(qū)動,同步于 RX_CLK,在 RX_CLK 的時鐘周期內(nèi),并且 RX_DV 有效,RXD 上的數(shù)據(jù)被RS 接收,否則 RXD 的數(shù)據(jù)對 RS 沒有任何影響。While RX_DV is de-asserted, the PHY may provide a False Carrier indication by asserting the RX_ER signal while driving the value <1110> onto RXD<3:0>。

RX_ER(receive error): RX_ER 同步于 RX_CLK,其在 RX 通道中的作用類似于 TX_ER 對于 TX 通道數(shù)據(jù)傳輸?shù)挠绊憽?/p>

RX_CLK: 它與 TX_CLK 具有相同的要求,所不同的是它是 RX_DV、RXD、RX_ER(信號方向是從 PHY 到 RS)的參考時鐘。RX_CLK 同樣是由 PHY 驅(qū)動,PHY 可能從接收到的數(shù)據(jù)中提取時鐘 RX_CLK,也有可能從一個名義上的參考時鐘(e.g., the TX_CLK reference)來驅(qū)動RX_CLK。

CRS(carrier sense): CRS 不需要同步于參考時鐘,只要通道存在發(fā)送或者接收過程,CRS 就需要有效。The behavior of the CRS signal is unspecified when the duplex mode bit0.8 inthe control register is set to a logic one(自動協(xié)商禁止,人工設(shè)為全雙工模式), or when the Auto-Negotiation process selects a full duplex mode of operation,即半雙工模式信號有效,全雙工模式信號無效。

RX_DV(Receive Data Valid): RXD_DV 同步于 RX_CLK,被 PHY 驅(qū)動,它的作用如同于發(fā)送通道中的 TX_EN,不同的是在時序上稍有一點差別:為了讓數(shù)據(jù)能夠成功被RS接收,要求RXD_DV有效的時間必須覆蓋整個 FRAME 的過程,即starting no later than the Start Frame Delimiter (SFD) and excluding any End-of-Frame delimiter。MII以4位半字節(jié)方式傳送數(shù)據(jù)雙向傳輸,時鐘速率25MHz。其工作速率可達(dá)100Mb/s。

MII 管理接口: 是個雙信號接口,通過管理接口,MAC 就能監(jiān)視和控制 PHY。其管理是使用 SMI(Serial Management Interface) 總線通過讀寫 PHY 的寄存器來完成的。一個是時鐘信號(***MDC (management data clock))。另一個是數(shù)據(jù)信號(MDIO (management data input/output)***)。

MDC: 由站管理實體向 PHY 提供,作為在 MDIO 信號上傳送信息的定時參考。MDC 是一種非周期性的信號,沒有最高或最低時間。無論 TX_CLK 和 RX_CLK 的標(biāo)稱周期如何,MDC 的最小高低時間應(yīng)為 160 ns,MDC 的最小周期為 400 ns。

MDIO: 是 PHY 和 STA 之間的雙向信號。它用于在 PHY 和 STA 之間傳輸控制信息和狀態(tài)。控制信息由 STA 同步地針對 MDC 驅(qū)動并且由 PHY 同步地采樣。狀態(tài)信息由 PHY 針對 MDC 同步驅(qū)動并由 STA 同步采樣。

PHY 里面的部分寄存器是 IEEE 定義的,這樣PHY把自己的目前的狀態(tài)反映到寄存器里面。

MAC 通過 SMI 總線不斷的讀取PHY 的狀態(tài)寄存器以得知目前 PHY 的狀態(tài)。例如連接速度、雙工的能力等。

當(dāng)然也可以通過 SMI 設(shè)置 PHY的寄存器達(dá)到控制的目的。例如流控的打開關(guān)閉、自協(xié)商模式還是強制模式等。

不論是物理連接的MII總線和 SMI 總線,還是 PHY 的狀態(tài)寄存器和控制寄存器都是由IEEE的規(guī)范的。因此不同公司的 MAC 和 PHY 一樣可以協(xié)調(diào)工作。當(dāng)然為了配合不同公司的 PHY 的自己特有的一些功能,驅(qū)動需要做相應(yīng)的修改。

MII 支持 10Mbps 和 100Mbps 的操作,一個接口由 14 根線組成,它的支持還是比較靈活的。

但是有一個缺點是因為它一個端口用的信號線太多,如果一個 8 端口的交換機要用到 112 根線,16 端口就要用到 224 根線,到 32 端口的話就要用到 448 根線。

一般按照這個接口做交換機是不太現(xiàn)實的。所以現(xiàn)代的交換機的制作都會用到其它的一些從 MII 簡化出來的標(biāo)準(zhǔn),比如 RMII、SMII、GMII等。

什么是RMII

簡化媒體獨立接口是標(biāo)準(zhǔn)的以太網(wǎng)接口之一,比 MII 有更少的 I/O 傳輸。RMII 口是用兩根線來傳輸數(shù)據(jù)的,MII 口是用 4 根線來傳輸數(shù)據(jù)的,GMII 是用 8 根線來傳輸數(shù)據(jù)的。MII/RMII 只是一種接口,對于10Mbps 線速,MII 的時鐘速率是 2.5MHz 就可以了,RMII 則需要 5MHz;對于 100Mbps 線速,MII 需要的時鐘速率是 25MHz,RMII 則是 50MHz。

MII/RMII 用于傳輸以太網(wǎng)包,在 MII/RMII 接口是 4/2bit 的,在以太網(wǎng)的PHY里需要做串并轉(zhuǎn)換,編解碼等才能在雙絞線和光纖上進(jìn)行傳輸,其幀格式遵循IEEE 802.3(10M)/IEEE 802.3u(100M)/IEEE 802.1q(VLAN)。

以太網(wǎng)幀的格式為:前導(dǎo)符 + 開始位 + 目的 mac 地址 + 源 mac 地址 + 類型/長度 + 數(shù)據(jù) + padding(optional) + 32bitCRC。如果有 vlan,則要在類型/長度后面加上 2 個字節(jié)的 vlan tag,其中 12bit 來表示vlan id,另外,4bit 表示數(shù)據(jù)的優(yōu)先級!

什么是GMII

GMII是千兆網(wǎng)的MII接口,這個也有相應(yīng)的RGMII接口,表示簡化了的GMII接口。GMII 采用 8 位接口數(shù)據(jù),工作時鐘125MHz,因此傳輸速率可達(dá) 1000Mbps。同時兼容 MII 所規(guī)定的10/100 Mbps工作方式。GMII 接口數(shù)據(jù)結(jié)構(gòu)符合IEEE以太網(wǎng)標(biāo)準(zhǔn),該接口定義見 IEEE 802.3-2000。

?

| 信號名稱 | 描述 | 方向 |

|---|---|---|

| GTX_CLK | 1000M發(fā)送時鐘 | MAC → PHY |

| TX_CLK | 100/10M發(fā)送時鐘 | MAC → PHY |

| TX_ER | 發(fā)送數(shù)據(jù)錯誤 | MAC → PHY |

| TX_EN | 發(fā)送使能 | MAC → PHY |

| TX_[7:0] | 發(fā)送數(shù)據(jù)8bit | MAC → PHY |

| RX_CLK | 接收時鐘 | PHY → MAC |

| RX_DV | 接收數(shù)據(jù)有效 | PHY → MAC |

| RX_ER | 接收數(shù)據(jù)錯誤 | PHY → MAC |

| RX_[7:0] | 接收數(shù)據(jù)8bit | PHY → MAC |

| CRS | 載波監(jiān)測 | PHY → MAC |

| COL | 沖突碰撞監(jiān)測 | PHY → MAC |

| MDIO | 管理數(shù)據(jù) | 雙向 |

| MDC | 管理數(shù)據(jù)時鐘 | MAC → PHY |

?

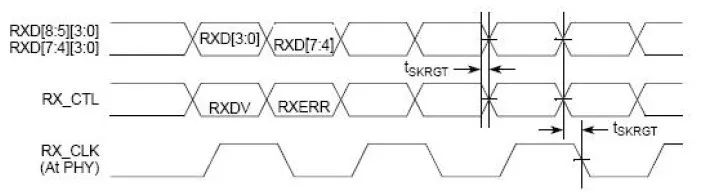

什么是RGMII

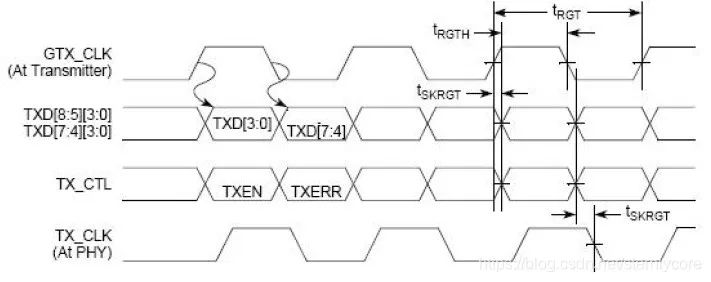

RGMII(Reduced Gigabit Media Independant Interface),精簡GMII接口。相對于GMII相比,RGMII具有如下特征:

發(fā)送/接收數(shù)據(jù)線由8條改為4條

TX_ER和TX_EN復(fù)用,通過TX_CTL傳送

RX_ER與RX_DV復(fù)用,通過RX_CTL傳送

1 Gbit/s速率下,時鐘頻率為125MHz

100 Mbit/s速率下,時鐘頻率為25MHz

10 Mbit/s速率下,時鐘頻率為2.5MHz

信號定義如下:

?

| 信號名稱 | 描述 | 方向 |

|---|---|---|

| TXC | 發(fā)送時鐘 | MAC→PHY |

| TX_CTL | 發(fā)送數(shù)據(jù)控制 | MAC → PHY |

| TXD[3:0] | 發(fā)送數(shù)據(jù)4bit | MAC → PHY |

| RXC | 接收時鐘 | PHY → MAC |

| RX_CTL | 接收數(shù)據(jù)控制 | PHY → MAC |

| RXD[3:0] | 接收數(shù)據(jù)4bit | PHY → MAC |

| MDIO | 管理數(shù)據(jù) | 雙向 |

| MDC | 管理數(shù)據(jù)時鐘 | MAC → PHY |

?

雖然RGMII信號線減半,但TXC/RXC時鐘仍為125Mhz,為了達(dá)到1000Mbit的傳輸速率,TXD/RXD信號線在時鐘上升沿發(fā)送接收GMII接口中的TXD[3:0]/RXD[3:0],在時鐘下降沿發(fā)送接收TXD[7:4]/RXD[7:4],并且信號TX_CTL反應(yīng)了TX_EN和TX_ER狀態(tài),即在TXC上升沿發(fā)送TX_EN,下降沿發(fā)送TX_ER,同樣的道理試用于RX_CTL,下圖為發(fā)送接收的時序:

什么是SMI

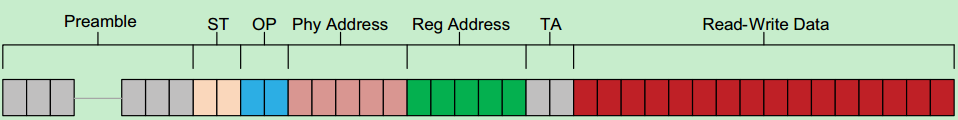

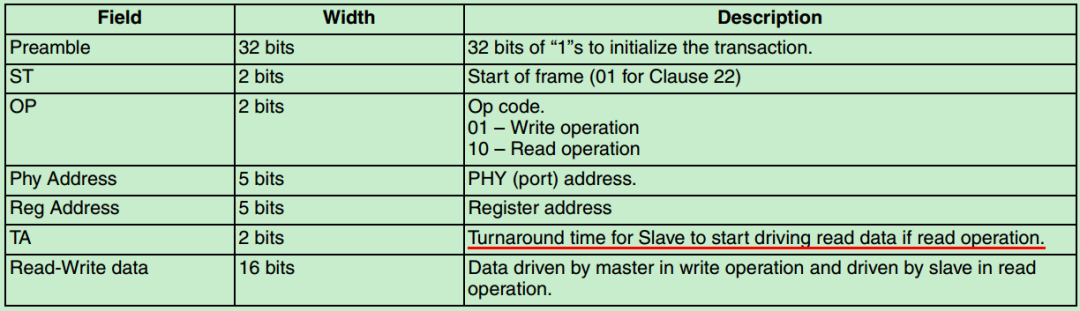

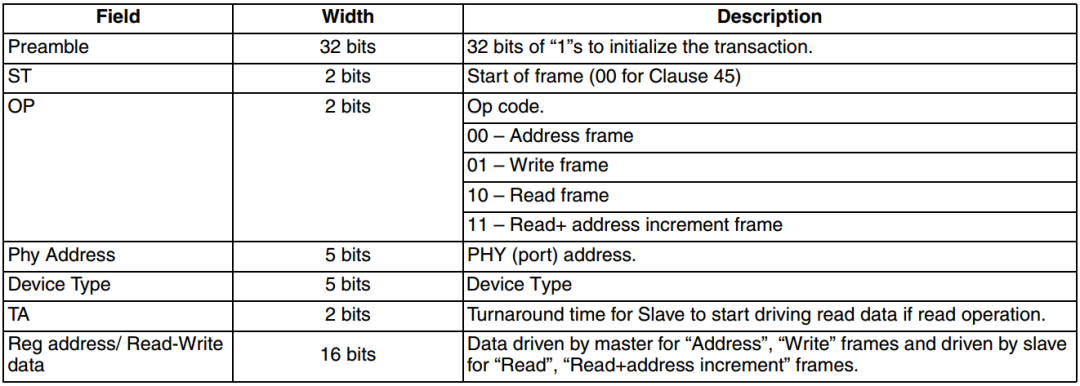

SMI:串行管理接口(Serial Management Interface),通常直接被稱為MDIO接口(Management Data Input/Output Interface)。MDIO最早在IEEE 802.3的第22卷定義,后來在第45卷又定義了增強版本的MDIO,其主要被應(yīng)用于以太網(wǎng)的MAC和PHY層之間,用于MAC層器件通過讀寫寄存器來實現(xiàn)對PHY層器件的操作與管理。

MDIO主機(即產(chǎn)生MDC時鐘的設(shè)備)通常被稱為STA(Station Management Entity),而MDIO從機通常被稱為MMD(MDIO Management Device)。通常STA都是MAC層器件的一部分,而MMD則是PHY層器件的一部分。

MDIO接口包括兩條線,MDIO和MDC,其中MDIO是雙向數(shù)據(jù)線,而MDC是由STA驅(qū)動的時鐘線。MDC時鐘的最高速率一般為2.5MHz,MDC也可以是非固定頻率,甚至可以是非周期的。MDIO接口只是會在MDC時鐘的上升沿進(jìn)行采樣,而并不在意MDC時鐘的頻率(類似于I2C接口)。如下圖所示。

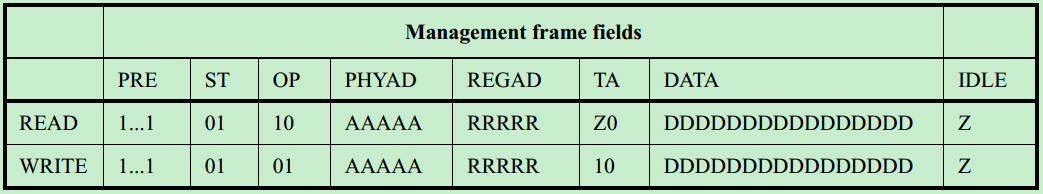

MDIO接口有兩個版本,通常被稱為卷22版本和卷45版本。卷22版本的MDIO接口最多支持連接32個MMD(PHY層設(shè)備),每個設(shè)備最多支持32個寄存器。卷45版本的MDIO接口最多支持連接32個MMD,32個設(shè)備類型,每個設(shè)備最多支持64K個寄存器。卷22版本的MDIO接口的數(shù)據(jù)幀格式如下:

具體每個bit描述如下:

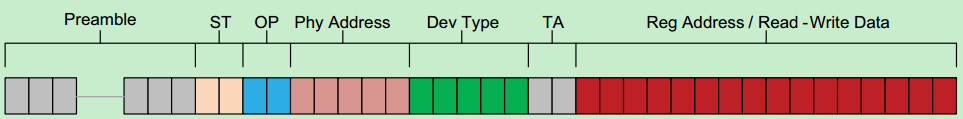

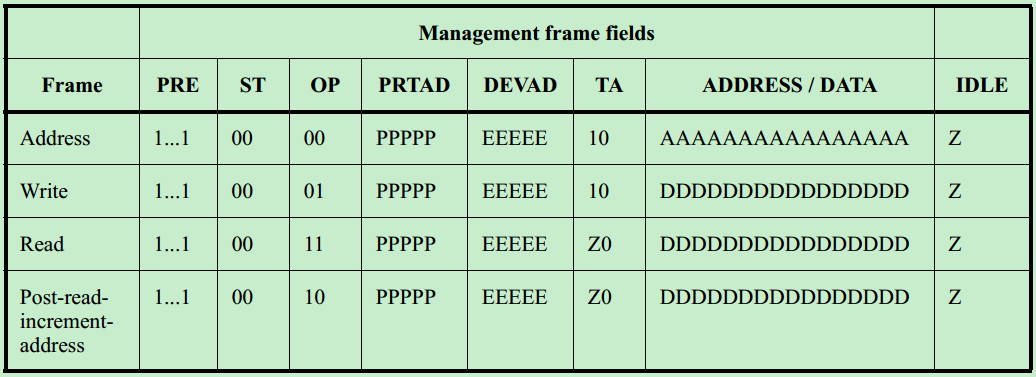

卷45版本的MDIO接口的數(shù)據(jù)幀格式如下:

具體每個bit的描述如下:

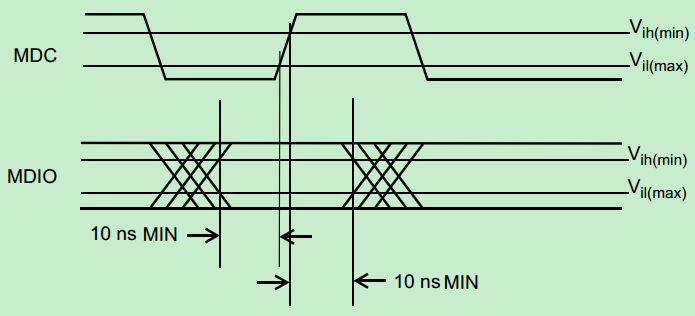

如果是STA(MAC層設(shè)備)驅(qū)動MDIO,則MDIO相對于MDC上升沿,至少要有10ns的建立時間(Setup Time)和10ns的保持時間(Hold Time)。如下圖所示:

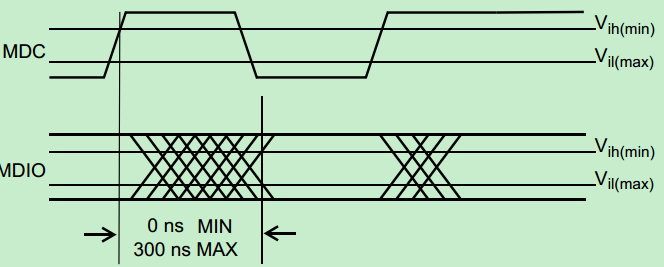

如果MDIO是由MMD(PHY層設(shè)備)驅(qū)動的,則MDIO相對于MDC的Tco(Clock to Output Delay)的范圍是0ns~300ns。如下圖所示:

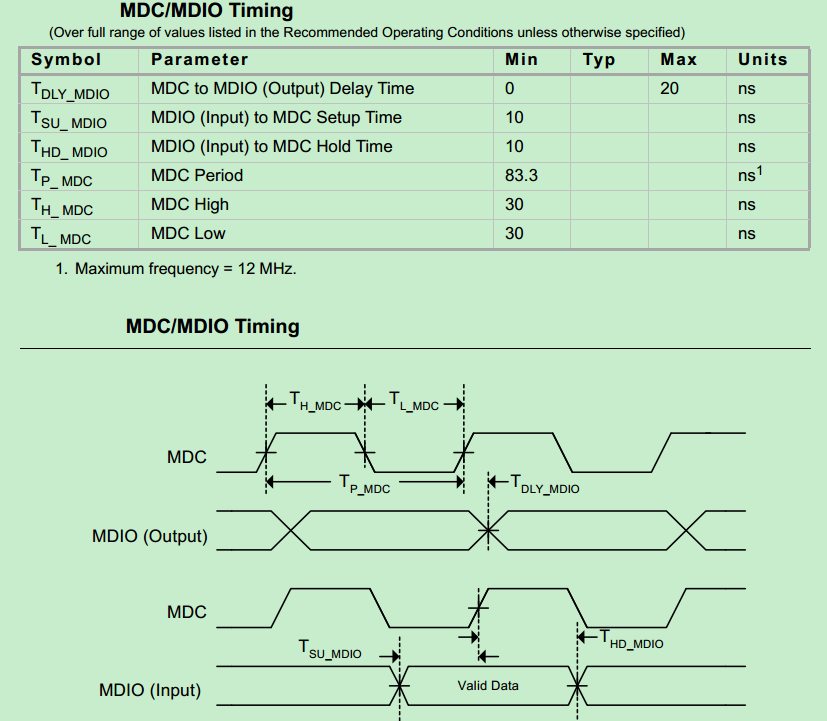

實際上,MDC的頻率也并非一定是小于或等于2.5MHz,比如Marvell的88E1512最大支持12MHz的MDC:

IEEE 802.3建議同時對MDIO進(jìn)行下拉(下拉電阻建議為2k歐姆+5%),和上拉(上拉電阻建議為1.5k歐姆+5%),使得在TA時,MDIO處于中間態(tài)。但是并非所有的PHY器件都有這樣的要求,比如Marvell的88E1512只要求對MDIO進(jìn)行上拉即可,上拉電阻范圍為1.5k~10kΩ。

QA

網(wǎng)卡的MAC和PHY間的關(guān)系?

網(wǎng)卡工作在osi的最后兩層,物理層和數(shù)據(jù)鏈路層,物理層定義了數(shù)據(jù)傳送與接收所需要的電與光信號、線路狀態(tài)、時鐘基準(zhǔn)、數(shù)據(jù)編碼和電路等,并向數(shù)據(jù)鏈路層設(shè)備提供標(biāo)準(zhǔn)接口.物理層的芯片稱之為PHY.

數(shù)據(jù)鏈路層則提供尋址機構(gòu)、數(shù)據(jù)幀的構(gòu)建、數(shù)據(jù)差錯檢查、傳送控制、向網(wǎng)絡(luò)層提供標(biāo)準(zhǔn)的數(shù)據(jù)接口等功能.以太網(wǎng)卡中數(shù)據(jù)鏈路層的芯片稱之為MAC控制器.

很多網(wǎng)卡的這兩個部分是做到一起的.他們之間的關(guān)系是pci總線接mac總線,mac接phy,phy接網(wǎng)線(當(dāng)然也不是直接接上的,還有一個變壓裝置).

網(wǎng)卡上除RJ-45接口外,還需要其它元件嗎?

PHY和MAC是網(wǎng)卡的主要組成部分,網(wǎng)卡一般用RJ-45插口,10M網(wǎng)卡的RJ-45插口也只用了1,2,3,6四根針,而100M或1000M網(wǎng)卡的則是八根針都是全的.

除此以外,還需要其它元件,因為雖然PHY提供絕大多數(shù)模擬支持,但在一個典型實現(xiàn)中,仍需外接6,7只分立元件及一個局域網(wǎng)絕緣模塊.絕緣模塊一般采用一個1:1的變壓器.這些部件的主要功能是為了保護PHY免遭由于電氣失誤而引起的損壞.

另外,一顆CMOS制程的芯片工作的時候產(chǎn)生的信號電平總是大于0V的(這取決于芯片的制程和設(shè)計需求),但是這樣的信號送到100米甚至更長的地方會有很大的直流分量的損失.而且如果外部網(wǎng)線直接和芯片相連的話,電磁感應(yīng)(打雷)和靜電,很容易造成芯片的損壞.再就是設(shè)備接地方法不同,電網(wǎng)環(huán)境不同會導(dǎo)致雙方的0V電平不一致,這樣信號從A傳到B,由于A設(shè)備的0V電平和B點的0V電平不一樣,這樣會導(dǎo)致很大的電流從電勢高的設(shè)備流向電勢低的設(shè)備.

為了解決以上問題Transformer(隔離變壓器)這個器件就應(yīng)運而生.它把PHY送出來的差分信號用差模耦合的線圈耦合濾波以增強信號,并且通過電磁場的轉(zhuǎn)換耦合到連接網(wǎng)線的另外一端.這樣不但使網(wǎng)線和PHY之間沒有物理上的連接而換傳遞了信號,隔斷了信號中的直流分量,還可以在不同0V電平的設(shè)備中傳送數(shù)據(jù).

隔離變壓器本身就是設(shè)計為耐2KV~3KV的電壓的.也起到了防雷感應(yīng)(我個人認(rèn)為這里用防雷擊不合適)保護的作用.有些朋友的網(wǎng)絡(luò)設(shè)備在雷雨天氣時容易被燒壞,大都是PCB設(shè)計不合理造成的,而且大都燒毀了設(shè)備的接口,很少有芯片被燒毀的,就是隔離變壓器起到了保護作用.

隔離變壓器本身是個被動元件,只是把PHY的信號耦合了到網(wǎng)線上,并沒有起到功率放大的作用.那么一張網(wǎng)卡信號的傳輸?shù)淖铋L距離是誰決定的呢?

一張網(wǎng)卡的傳輸最大距離和與對端設(shè)備連接的兼容性主要是PHY決定的.但是可以將信號送的超過100米的PHY其輸出的功率也比較大,更容易產(chǎn)生EMI的問題.這時候就需要合適的Transformer與之配合.作PHY的老大公司Marvell的PHY,常常可以傳送180~200米的距離,遠(yuǎn)遠(yuǎn)超過IEEE的100米的標(biāo)準(zhǔn).

RJ-45的接頭實現(xiàn)了網(wǎng)卡和網(wǎng)線的連接.它里面有8個銅片可以和網(wǎng)線中的4對雙絞(8根)線對應(yīng)連接.其中100M的網(wǎng)絡(luò)中1,2是傳送數(shù)據(jù)的,3,6是接收數(shù)據(jù)的.1,2之間是一對差分信號,也就是說它們的波形一樣,但是相位相差180度,同一時刻的電壓幅度互為正負(fù).這樣的信號可以傳遞的更遠(yuǎn),抗干擾能力強.同樣的,3,6也一樣是差分信號.

網(wǎng)線中的8根線,每兩根扭在一起成為一對.我們制作網(wǎng)線的時候,一定要注意要讓1,2在其中的一對,3,6在一對.否則長距離情況下使用這根網(wǎng)線的時候會導(dǎo)致無法連接或連接很不穩(wěn)定.

現(xiàn)在新的PHY支持AUTO MDI-X功能(也需要Transformer支持).它可以實現(xiàn)RJ-45接口的1,2上的傳送信號線和3,6上的接收信號線的功能自動互相交換.有的PHY甚至支持一對線中的正信號和負(fù)信號的功能自動交換.這樣我們就不必為了到底連接某個設(shè)備需要使用直通網(wǎng)線還是交叉網(wǎng)線而費心了.這項技術(shù)已經(jīng)被廣泛的應(yīng)用在交換機和SOHO路由器上.

在1000Basd-T網(wǎng)絡(luò)中,其中最普遍的一種傳輸方式是使用網(wǎng)線中所有的4對雙絞線,其中增加了4,5和7,8來共同傳送接收數(shù)據(jù).由于1000Based-T網(wǎng)絡(luò)的規(guī)范包含了AUTOMDI-X功能,因此不能嚴(yán)格確定它們的傳出或接收的關(guān)系,要看雙方的具體的協(xié)商結(jié)果.

一片網(wǎng)卡主要功能的實現(xiàn)就基本上是上面這些器件了.

其他的,還有一顆EEPROM芯片,通常是一顆93C46.里面記錄了網(wǎng)卡芯片的供應(yīng)商ID,子系統(tǒng)供應(yīng)商ID,網(wǎng)卡的MAC地址,網(wǎng)卡的一些配置,如SMI總線上PHY的地址,BOOTROM的容量,是否啟用BOOTROM引導(dǎo)系統(tǒng)等東西.

很多網(wǎng)卡上還有BOOTROM這個東西.它是用于無盤工作站引導(dǎo)操作系統(tǒng)的.既然無盤,一些引導(dǎo)用必需用到的程序和協(xié)議棧就放到里面了,例如RPL,PXE等.實際上它就是一個標(biāo)準(zhǔn)的PCI ROM.所以才會有一些硬盤寫保護卡可以通過燒寫網(wǎng)卡的BootRom來實現(xiàn).其實PCI設(shè)備的ROM是可以放到主板BIOS里面的.啟動電腦的時候一樣可以檢測到這個ROM并且正確識別它是什么設(shè)備的.AGP在配置上和PCI很多地方一樣,所以很多顯卡的BIOS也可以放到主板BIOS里面.這就是為什么板載的網(wǎng)卡我們從來沒有看到過BOOTROM的原因.

最后就是電源部分了.大多數(shù)網(wǎng)卡現(xiàn)在都使用3.3V或更低的電壓.有的是雙電壓的.因此需要電源轉(zhuǎn)換電路.

而且網(wǎng)卡為了實現(xiàn)Wake on line功能,必須保證全部的PHY和MAC的極少一部分始終處于有電的狀態(tài),這需要把主板上的5V Standby電壓轉(zhuǎn)換為PHY工作電壓的電路.在主機開機后,PHY的工作電壓應(yīng)該被從5V轉(zhuǎn)出來的電壓替代以節(jié)省5V Standby的消耗.(許多劣質(zhì)網(wǎng)卡沒有這么做).

有Wake on line功能的網(wǎng)卡一般還有一個WOL的接口.那是因為PCI2.1以前沒有PCI設(shè)備喚醒主機的功能,所以需要著一根線通過主板上的WOL的接口連到南橋里面以實現(xiàn)WOL的功能.新的主板合網(wǎng)卡一般支持PCI2.2/2.3,擴展了PME#信號功能,不需要那個接口而通過PCI總線就可以實現(xiàn)喚醒功能.

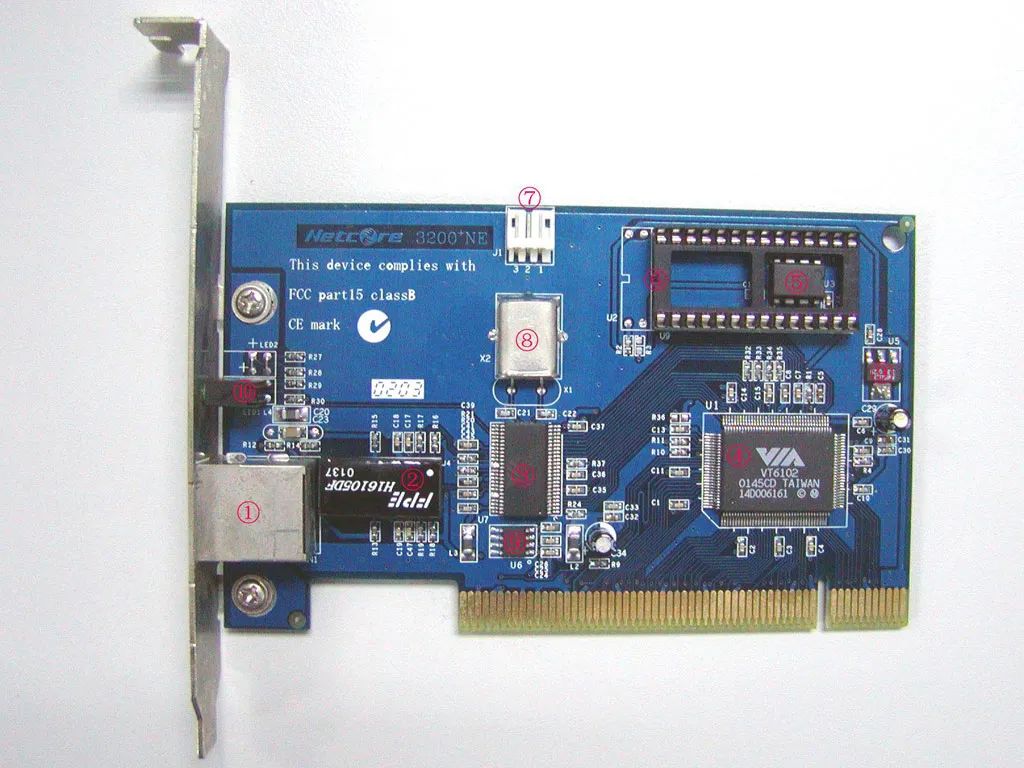

我們現(xiàn)在來看兩個圖

MAC和PHY分開的以太網(wǎng)卡

MAC和PHY集成在一顆芯片的以太網(wǎng)卡

上圖中各部件為:

①RJ-45接口

②Transformer(隔離變壓器)

③PHY芯片

④MAC芯片

⑤EEPROM

⑥BOOTROM插槽

⑦WOL接頭

⑧晶振

⑨電壓轉(zhuǎn)換芯片

網(wǎng)卡的功能主要有兩個:一是將電腦的數(shù)據(jù)封裝為幀,并通過網(wǎng)線(對無線網(wǎng)絡(luò)來說就是電磁波)將數(shù)據(jù)發(fā)送到網(wǎng)絡(luò)上去;二是接收網(wǎng)絡(luò)上其它設(shè)備傳過來的幀,并將幀重新組合成數(shù)據(jù),發(fā)送到所在的電腦中.網(wǎng)卡能接收所有在網(wǎng)絡(luò)上傳輸?shù)男盘?但正常情況下只接受發(fā)送到該電腦的幀和廣播幀,將其余的幀丟棄.然后,傳送到系統(tǒng)CPU做進(jìn)一步處理.當(dāng)電腦發(fā)送數(shù)據(jù)時,網(wǎng)卡等待合適的時間將分組插入到數(shù)據(jù)流中.接收系統(tǒng)通知電腦消息是否完整地到達(dá),如果出現(xiàn)問題,將要求對方重新發(fā)送.

PHY和MAC之間如何進(jìn)行溝通

通過IEEE定義的標(biāo)準(zhǔn)的MII/GigaMII(Media Independed Interfade,介質(zhì)獨立界面)界面連接MAC和PHY。這個界面是IEEE定義的。MII界面?zhèn)鬟f了網(wǎng)絡(luò)的所有數(shù)據(jù)和數(shù)據(jù)的控制。

而MAC對PHY的工作狀態(tài)的確定和對PHY的控制則是使用SMI(Serial Management Interface)界面通過讀寫PHY的寄存器來完成的。PHY里面的部分寄存器也是IEEE定義的,這樣PHY把自己的目前的狀態(tài)反映到寄存器里面,MAC通過SMI總線不斷的讀取PHY的狀態(tài)寄存器以得知目前PHY的狀態(tài),例如連接速度,雙工的能力等。當(dāng)然也可以通過SMI設(shè)置PHY的寄存器達(dá)到控制的目的,例如流控的打開關(guān)閉,自協(xié)商模式還是強制模式等。

我們看到了,不論是物理連接的MII界面和SMI總線還是PHY的狀態(tài)寄存器和控制寄存器都是有IEEE的規(guī)范的,因此不同公司的MAC和PHY一樣可以協(xié)調(diào)工作。當(dāng)然為了配合不同公司的PHY的自己特有的一些功能,驅(qū)動需要做相應(yīng)的修改。

一片網(wǎng)卡主要功能的實現(xiàn)就基本上是上面這些器件了。

其他的,還有一顆EEPROM芯片,通常是一顆93C46。里面記錄了網(wǎng)卡芯片的供應(yīng)商ID、子系統(tǒng)供應(yīng)商ID、網(wǎng)卡的MAC地址、網(wǎng)卡的一些配置,如SMI總線上PHY的地址,BOOTROM的容量,是否啟用BOOTROM引導(dǎo)系統(tǒng)等東西。

很多網(wǎng)卡上還有BOOTROM這個東西。它是用于無盤工作站引導(dǎo)操作系統(tǒng)的。

既然無盤,一些引導(dǎo)用必需用到的程序和協(xié)議棧就放到里面了,例如RPL、PXE等。實際上它就是一個標(biāo)準(zhǔn)的PCI ROM。所以才會有一些硬盤寫保護卡可以通過燒寫網(wǎng)卡的BootRom來實現(xiàn)。

其實PCI設(shè)備的ROM是可以放到主板BIOS里面的。啟動電腦的時候一樣可以檢測到這個ROM并且正確識別它是什么設(shè)備的。AGP在配置上和PCI很多地方一樣,所以很多顯卡的BIOS也可以放到主板BIOS里面。這就是為什么板載的網(wǎng)卡我們從來沒有看到過BOOTROM的原因。

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論