CXL (Compute Express Link) 技術(shù)是一種新型的高速互聯(lián)技術(shù),旨在提供更高的數(shù)據(jù)吞吐量和更低的延遲,以滿足現(xiàn)代計(jì)算和存儲(chǔ)系統(tǒng)的需求。它最初由英特爾、AMD和其他公司聯(lián)合推出,并得到了包括谷歌、微軟等公司在內(nèi)的大量支持。

01.?CXL介紹

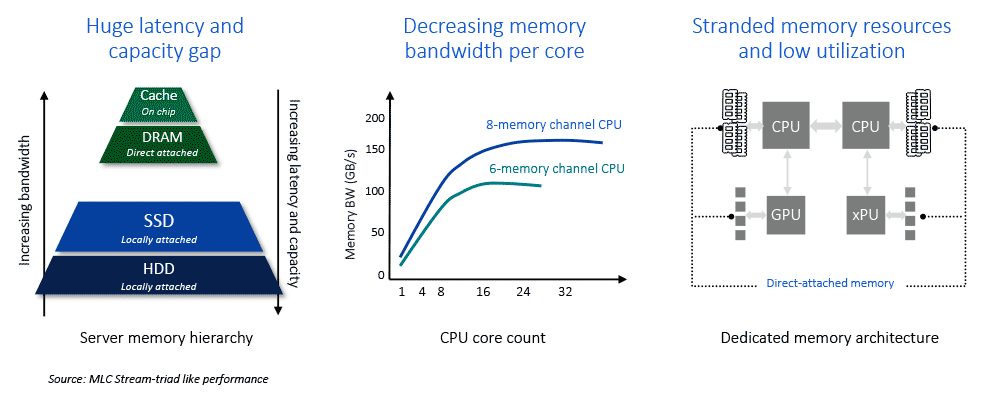

CXL的目標(biāo):解決CPU和設(shè)備、設(shè)備和設(shè)備之間的內(nèi)存鴻溝。服務(wù)器有巨大的內(nèi)存池和數(shù)量龐大的基于PCIe運(yùn)算加速器,每個(gè)上面都有很大的內(nèi)存。內(nèi)存的分割已經(jīng)造成巨大的浪費(fèi)、不便和性能下降。CXL就是為解決這個(gè)問題而誕生。 ?

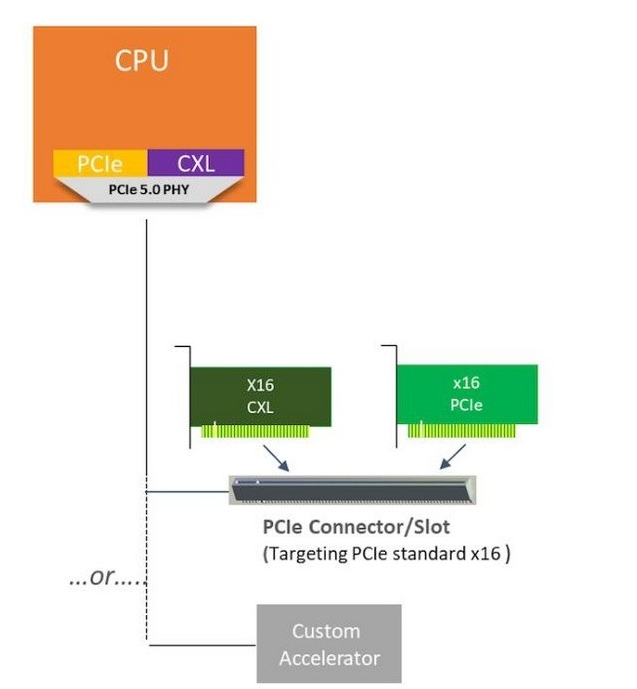

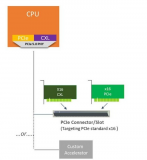

CXL技術(shù)的背景可以追溯到PCIe (Peripheral Component Interconnect Express) 技術(shù),PCIe是用于連接計(jì)算機(jī)內(nèi)部組件的一種標(biāo)準(zhǔn)接口技術(shù)。PCIe設(shè)備可以發(fā)起一個(gè)DMA來訪問內(nèi)存,只要知道目標(biāo)物理地址即可。在CXL之前就有以IBM牽頭的OpenCAPI,ARM為代表支持的CCIX,AMD等支持的GenZ和Nvidia自行提出的Nvlink等等多種協(xié)議。雖然PCIe已經(jīng)有了很多改進(jìn),但其難以滿足現(xiàn)代計(jì)算機(jī)處理器和加速器之間的高帶寬、低延遲通信需求。于是,CXL技術(shù)應(yīng)運(yùn)而生。

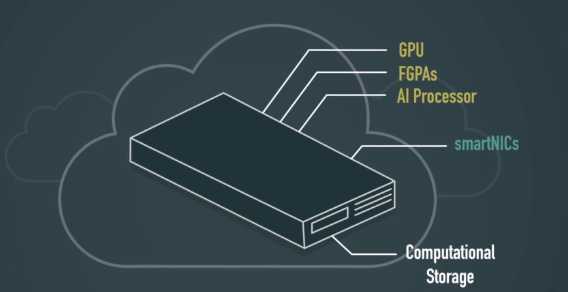

CXL技術(shù)的應(yīng)用場景非常廣泛,其中包括數(shù)據(jù)中心、人工智能和處理器互聯(lián)等領(lǐng)域。在數(shù)據(jù)中心領(lǐng)域,CXL技術(shù)可以將不同的計(jì)算和存儲(chǔ)資源進(jìn)行互聯(lián),提高系統(tǒng)性能和效率。在人工智能領(lǐng)域,CXL技術(shù)可以使GPU和FPGA等加速器更好地與主處理器進(jìn)行協(xié)作,提高AI模型訓(xùn)練和推理的速度。在處理器互聯(lián)方面,CXL技術(shù)可以實(shí)現(xiàn)不同廠商的處理器之間的互聯(lián),提高系統(tǒng)的整體性能和靈活性。

02.?CXL技術(shù)概覽

2.1、什么是CXL技術(shù)?

CXL(Compute Express Link)是一種高速串行協(xié)議,它允許在計(jì)算機(jī)系統(tǒng)內(nèi)部的不同組件之間進(jìn)行快速、可靠的數(shù)據(jù)傳輸。CXL在2020年推出,由英特爾、戴爾和惠普等公司共同設(shè)計(jì)。它旨在解決高性能計(jì)算中的瓶頸問題,包括內(nèi)存容量、內(nèi)存帶寬和I/O延遲等問題。CXL還可以實(shí)現(xiàn)內(nèi)存擴(kuò)展和內(nèi)存共享,并且可與計(jì)算加速器(如GPU、FPGA)等外設(shè)通信,提供更快、更靈活的數(shù)據(jù)交換和處理方式。

CXL技術(shù)不僅提供了高速傳輸,還支持內(nèi)存共享和虛擬化,使設(shè)備之間的協(xié)作更加緊密和高效。這種技術(shù)有助于滿足現(xiàn)代數(shù)據(jù)中心對(duì)大規(guī)模處理和分析的需求,同時(shí)也能夠?yàn)锳I、機(jī)器學(xué)習(xí)、區(qū)塊鏈等新興應(yīng)用提供更好的支持。

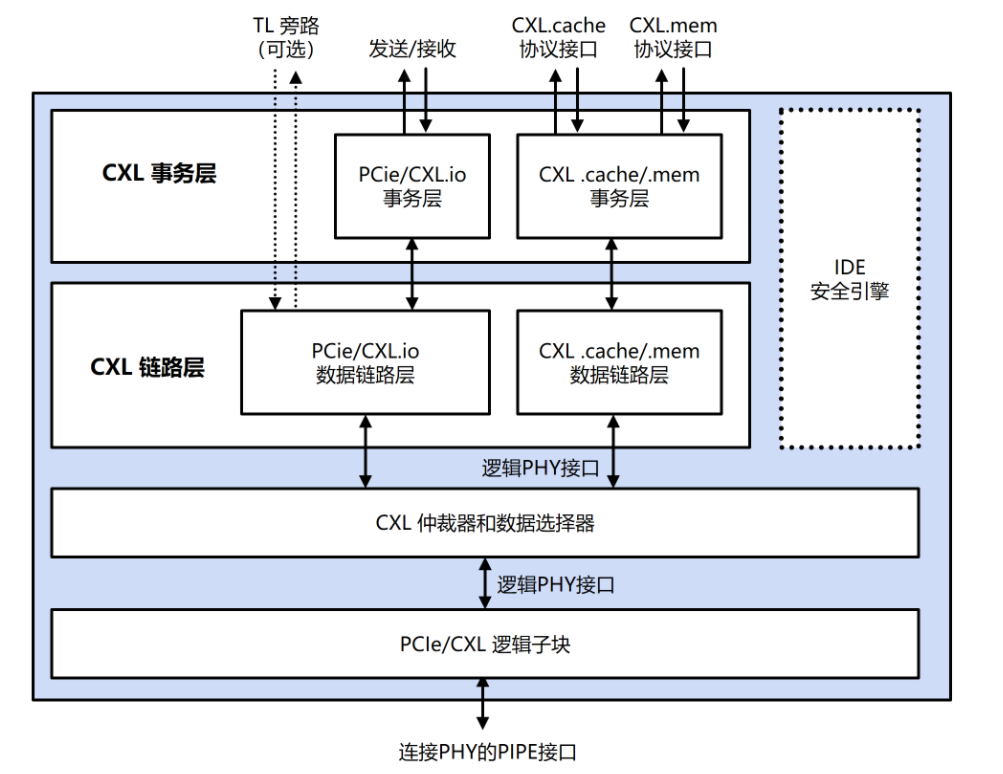

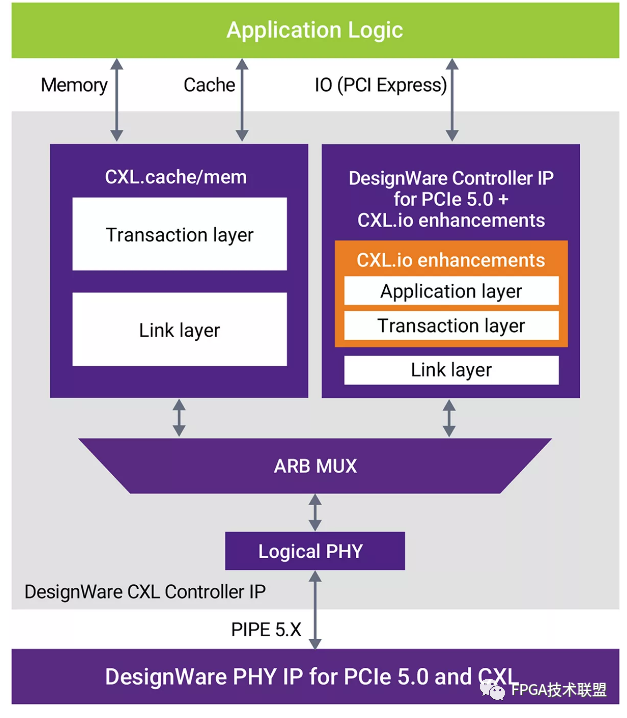

2.2、CXL技術(shù)的三種模式:http://CXL.io、CXL.cache和CXL.memory

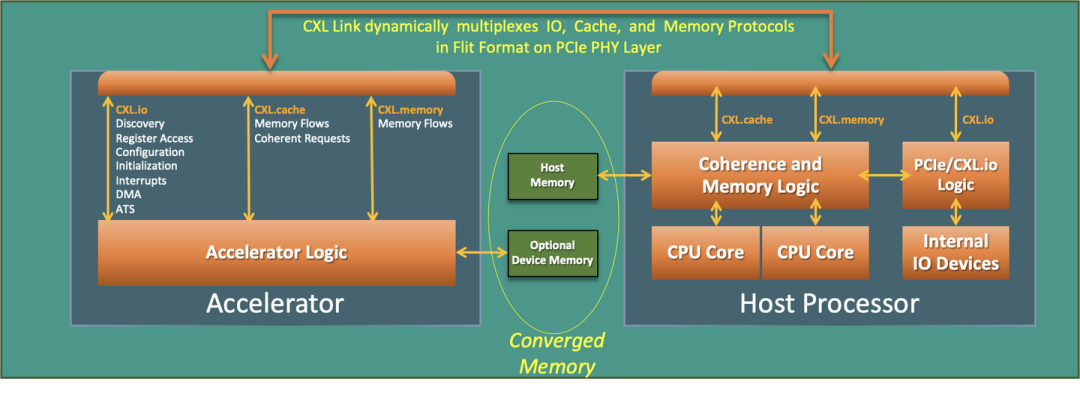

CXL協(xié)議包含三個(gè)子協(xié)議:

http://CXL.io:這種模式可以將內(nèi)存擴(kuò)展到外部設(shè)備,使得數(shù)據(jù)的傳輸速度更快。http://

CXL.io通過PCIe總線連接CPU和外部設(shè)備,這樣CPU就可以與外部設(shè)備共享內(nèi)存,并且可以直接訪問外部設(shè)備的I/O資源。

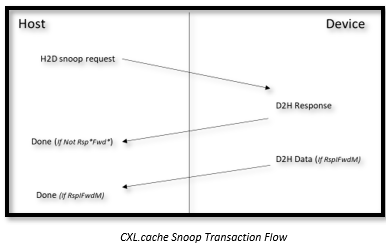

CXL.cache:這種模式可以通過將內(nèi)存緩存到外部設(shè)備中來提高性能。CXL.cache模式允許CPU在本地緩存中保留最常用的數(shù)據(jù),而將不常用的數(shù)據(jù)保存在外部設(shè)備中。這樣可以減少內(nèi)存訪問時(shí)間,提高整體系統(tǒng)性能。

CXL.memory:這種模式可以將外部設(shè)備作為主內(nèi)存使用,從而實(shí)現(xiàn)更大的內(nèi)存容量。CXL.memory模式允許CPU將外部設(shè)備看作是擴(kuò)展內(nèi)存,從而可以存儲(chǔ)更多的數(shù)據(jù)。這種方式可以提高系統(tǒng)的可靠性,因?yàn)榧词拱l(fā)生了內(nèi)存故障,CPU仍然可以通過外部設(shè)備繼續(xù)運(yùn)行。

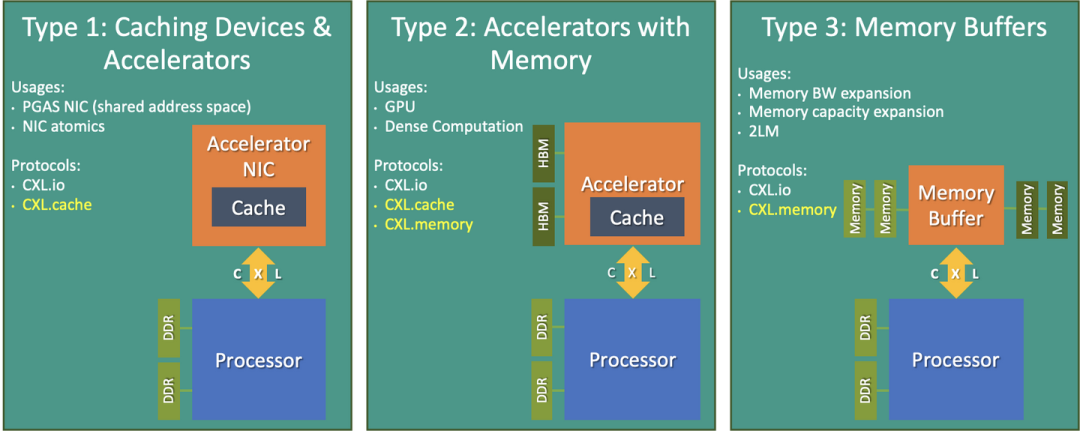

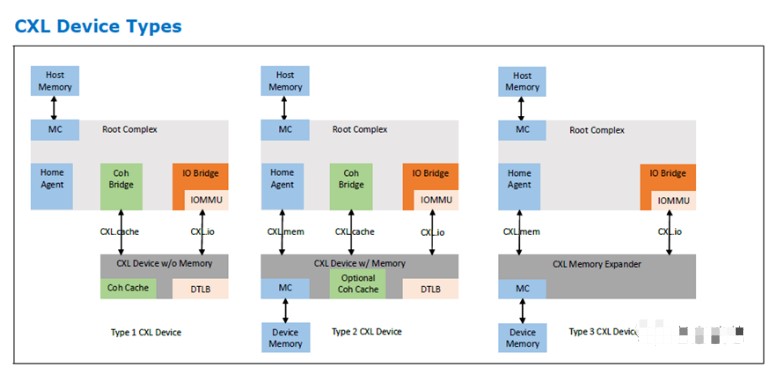

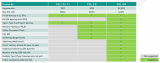

http://CXL.io是Compute Express Link(CXL)規(guī)范中定義的物理層接口,可以提供比傳統(tǒng)PCIe更低的延遲、更高的帶寬和更好的可擴(kuò)展性。 http://CXL.io通過使用SerDes技術(shù)(一種將串行數(shù)據(jù)轉(zhuǎn)換為并行數(shù)據(jù)以及反向轉(zhuǎn)換的技術(shù)),在單個(gè)物理通道上同時(shí)傳輸多個(gè)不同的數(shù)據(jù)流。這些數(shù)據(jù)流可以包括帶寬密集型的數(shù)據(jù)流、低延遲的命令和控制信息以及配置寄存器和狀態(tài)信息。http://CXL.io還支持熱插拔和鏈路訓(xùn)練等高級(jí)特性。 http://CXL.io的物理層規(guī)范定義了信號(hào)的電氣特性、時(shí)序要求和連接器接口,以確保高可靠性和高性能。http://CXL.io采用4x25Gbps或3x32Gbps的信號(hào)速率,并支持單向或雙向通信。連接器方面,http://CXL.io采用40個(gè)針腳的SMT連接器,其中27個(gè)針腳用于數(shù)據(jù)傳輸,其余用于電源、地線和時(shí)鐘信號(hào)。 CXL技術(shù)的三種類型:

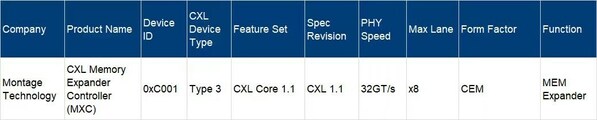

Type 1:通過 PCIe 插槽安裝的加速卡或附加卡。這些卡可以與現(xiàn)有系統(tǒng)集成,并通過 CXL 接口與 CPU 直接通信以提供更快的數(shù)據(jù)傳輸速度。用于網(wǎng)卡這類高速緩存設(shè)備。

Type 2:具有所有 Type 1 設(shè)備的功能,通常用于具有高密度計(jì)算的場景。比如 GPU 加速器。

Type 3:一種專用的存儲(chǔ)設(shè)備,與主機(jī)處理器直接通信,并且可以使用 CXL 協(xié)議來實(shí)現(xiàn)低延遲、高吞吐量的數(shù)據(jù)傳輸。用作內(nèi)存緩沖器,用于擴(kuò)展內(nèi)存帶寬和內(nèi)存容量。

03.?CXL技術(shù)的優(yōu)勢

更快的數(shù)據(jù)傳輸速度:CXL技術(shù)可以實(shí)現(xiàn)高達(dá)25GB/s的數(shù)據(jù)傳輸速度,比目前常用的PCIe 4.0技術(shù)還要快。這意味著在數(shù)據(jù)中心等高性能應(yīng)用場景下,可以更快地進(jìn)行數(shù)據(jù)處理和傳輸。

更低的延遲:CXL技術(shù)可以將CPU、GPU、FPGA等計(jì)算設(shè)備與內(nèi)存直接連接,避免了傳統(tǒng)的I/O總線帶來的時(shí)延,從而實(shí)現(xiàn)更低的延遲,提高了計(jì)算效率。

更高的能效:CXL技術(shù)支持在多臺(tái)計(jì)算設(shè)備之間共享內(nèi)存,降低了內(nèi)存冗余,提高了能效。此外,CXL技術(shù)還支持內(nèi)存虛擬化,可以根據(jù)應(yīng)用負(fù)載動(dòng)態(tài)分配內(nèi)存資源,進(jìn)一步提高了系統(tǒng)能效。

更強(qiáng)的可擴(kuò)展性:CXL技術(shù)可以支持內(nèi)存擴(kuò)展,允許在不停機(jī)的情況下添加更多的內(nèi)存容量,從而增加系統(tǒng)的可擴(kuò)展性,為未來的應(yīng)用需求做好準(zhǔn)備。

更廣泛的應(yīng)用場景:CXL技術(shù)不僅適用于數(shù)據(jù)中心等高性能計(jì)算領(lǐng)域,還可以應(yīng)用于人工智能、區(qū)塊鏈、物聯(lián)網(wǎng)等多個(gè)領(lǐng)域。

一句話:支持高帶寬、低延遲數(shù)據(jù)傳輸、具有更好的靈活性和可擴(kuò)展性、可以實(shí)現(xiàn)混合使用不同類型的硬件設(shè)備。 04.?CXL技術(shù)的應(yīng)用

4.1、計(jì)算機(jī)系統(tǒng)中的應(yīng)用

CXL可以用于計(jì)算機(jī)系統(tǒng)中的許多應(yīng)用:

高性能計(jì)算:CXL可以提供低延遲、高帶寬的協(xié)議,可用于連接CPU、GPU、FPGA等處理器,在高性能計(jì)算中提供更快的數(shù)據(jù)傳輸。

存儲(chǔ)加速:CXL可以用于連接存儲(chǔ)設(shè)備,如SSD和NVMe驅(qū)動(dòng)器,以提供更快的存儲(chǔ)訪問速度。此外,CXL還可以與內(nèi)存控制器集成,為存儲(chǔ)加速提供更大的帶寬。

人工智能:CXL可用于連接AI芯片,以提供更快的數(shù)據(jù)傳輸,從而提高AI工作負(fù)載的性能和效率。

網(wǎng)絡(luò)加速:CXL還可以用于連接網(wǎng)絡(luò)適配器,以提供更快的網(wǎng)絡(luò)傳輸速度,從而提高網(wǎng)絡(luò)應(yīng)用程序的性能。

4.2、數(shù)據(jù)中心中的應(yīng)用

在數(shù)據(jù)中心中,CXL可以應(yīng)用于以下方面:

高性能計(jì)算:CXL可以提供比傳統(tǒng)PCIe更快的數(shù)據(jù)傳輸速度和更低的延遲,從而提高高性能計(jì)算的效率和吞吐量。

存儲(chǔ)加速:CXL可以將存儲(chǔ)加速器與主機(jī)CPU直接連接,從而實(shí)現(xiàn)更快的數(shù)據(jù)訪問和更高的IOPS,提高存儲(chǔ)性能。

AI加速:CXL可以將AI加速器與CPU/GPU/FPGA等處理器直接連接,實(shí)現(xiàn)更快的模型訓(xùn)練和推理速度,提高人工智能應(yīng)用的性能。

大規(guī)模虛擬化:CXL可以將多個(gè)CPU和內(nèi)存資源組合成一個(gè)大規(guī)模虛擬化集群,從而提高資源利用率和靈活性,并降低虛擬化管理的復(fù)雜性。

4.3、人工智能領(lǐng)域中的應(yīng)用

在人工智能領(lǐng)域中,CXL可以發(fā)揮以下作用:

提高數(shù)據(jù)傳輸效率:對(duì)于深度學(xué)習(xí)等任務(wù),需要大量的數(shù)據(jù)傳輸和計(jì)算,在傳統(tǒng)的PCIe互連中,由于數(shù)據(jù)傳輸速度慢,往返延遲高,會(huì)導(dǎo)致計(jì)算效率低下。而使用CXL互連,可以實(shí)現(xiàn)低延遲、高速的數(shù)據(jù)傳輸,提高計(jì)算效率。

加速模型訓(xùn)練:隨著深度學(xué)習(xí)模型變得越來越復(fù)雜,需要更多的計(jì)算資源來進(jìn)行訓(xùn)練。使用CXL互連,可以將CPU、GPU和其他加速器設(shè)備進(jìn)行緊密協(xié)作,提高模型訓(xùn)練的速度和效率。

實(shí)現(xiàn)AI與物聯(lián)網(wǎng)的集成:CXL技術(shù)可以使AI應(yīng)用程序直接連接到物聯(lián)網(wǎng)設(shè)備,實(shí)現(xiàn)更快速的數(shù)據(jù)處理和響應(yīng)。這對(duì)于需要快速響應(yīng)的實(shí)時(shí)應(yīng)用程序非常重要。

降低能源消耗:CXL技術(shù)可以減少傳輸數(shù)據(jù)所需的功耗,同時(shí)還可以減少系統(tǒng)中的數(shù)據(jù)緩存,從而實(shí)現(xiàn)更高效的能源管理。

05.?CXL技術(shù)與其他技術(shù)的對(duì)比

與PCIe、NVMe等技術(shù)的對(duì)比:

帶寬:CXL的帶寬比PCIe高得多,CXL 2.0標(biāo)準(zhǔn)最高可以達(dá)到32 GT/s,而PCIe 5.0的帶寬只能達(dá)到16 GT/s。相比之下,NVMe是一種協(xié)議而非互連技術(shù),其帶寬取決于所使用的互連技術(shù)。

延遲:CXL和PCIe都具有低延遲的特點(diǎn),但CXL在延遲方面稍微優(yōu)于PCIe。NVMe協(xié)議在延遲方面表現(xiàn)良好。

功能:CXL支持內(nèi)存擴(kuò)展、緩存一致性和設(shè)備直接內(nèi)存訪問等功能,這些功能不是PCIe或NVMe所具備的。

應(yīng)用場景:PCIe主要用于連接外部設(shè)備,如GPU、網(wǎng)卡和存儲(chǔ)設(shè)備。NVMe主要用于連接固態(tài)硬盤。而CXL則更加靈活,可用于連接處理器、存儲(chǔ)設(shè)備、網(wǎng)絡(luò)適配器和其他外圍設(shè)備,適用范圍更廣。

兼容性:由于CXL是相對(duì)較新的技術(shù),許多舊設(shè)備可能無法與其兼容。PCIe則已經(jīng)成為了一種通用的連接標(biāo)準(zhǔn),并且得到廣泛應(yīng)用。

成本:目前來看,CXL硬件和設(shè)備的成本相對(duì)較高,而PCIe則更加普及和經(jīng)濟(jì)實(shí)惠。

CXL和CCIX都是用于連接不同芯片之間的高速互聯(lián)標(biāo)準(zhǔn),但它們?cè)谝恍┓矫娲嬖诓町悺R韵率荂XL與CCIX的主要對(duì)比:

性能:CXL標(biāo)準(zhǔn)提供了更高的帶寬和更低的延遲,使其在高性能計(jì)算、機(jī)器學(xué)習(xí)、人工智能等領(lǐng)域中具有優(yōu)勢。而CCIX標(biāo)準(zhǔn)則專注于低功耗和高可靠性,適用于物聯(lián)網(wǎng)、移動(dòng)設(shè)備等場景。

兼容性:CXL標(biāo)準(zhǔn)基于PCI Express協(xié)議,因此與現(xiàn)有的PCIe接口兼容。而CCIX標(biāo)準(zhǔn)則需要使用新的物理層和控制層,在一定程度上限制了其兼容性。

應(yīng)用場景:CXL標(biāo)準(zhǔn)適用于需要高性能和更強(qiáng)的內(nèi)存擴(kuò)展的場景,例如大型服務(wù)器集群和超級(jí)計(jì)算機(jī)。而CCIX標(biāo)準(zhǔn)則適用于需要低功耗和高可靠性的場景,例如數(shù)據(jù)中心、物聯(lián)網(wǎng)、移動(dòng)設(shè)備等。

支持的架構(gòu):CXL支持x86、Power和ARM等多種處理器架構(gòu)。而CCIX則專注于ARM和Power架構(gòu),對(duì)于x86架構(gòu)的支持有限。

06.?實(shí)現(xiàn)CXL技術(shù)的挑戰(zhàn)及解決方案

CXL技術(shù)的實(shí)現(xiàn)面臨以下挑戰(zhàn):

復(fù)雜性:CXL技術(shù)的實(shí)現(xiàn)需要高度復(fù)雜的系統(tǒng)設(shè)計(jì)和集成,這意味著需要適應(yīng)不同的硬件、軟件和工具。

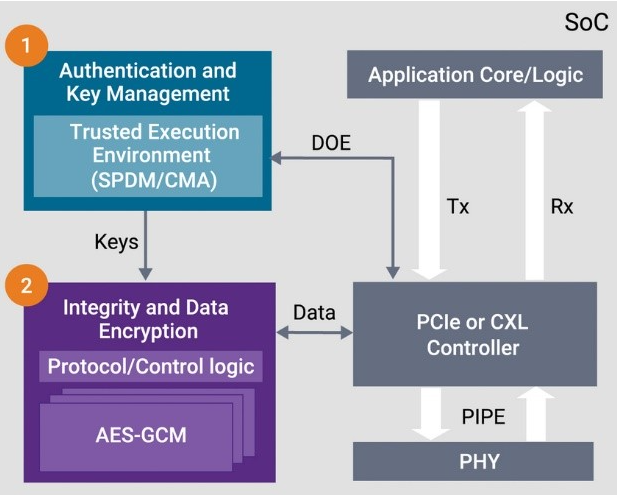

安全性:由于CXL技術(shù)涉及到底層硬件操作,并且可能涉及多個(gè)設(shè)備之間的數(shù)據(jù)共享,因此安全風(fēng)險(xiǎn)是一個(gè)重要考慮因素。需要采取適當(dāng)?shù)拇胧┐_保數(shù)據(jù)安全和隱私。

性能:CXL技術(shù)需要提供高速數(shù)據(jù)傳輸和低延遲,以滿足對(duì)計(jì)算能力和存儲(chǔ)能力的要求。這需要高效的協(xié)議和優(yōu)化的硬件和軟件設(shè)計(jì)。

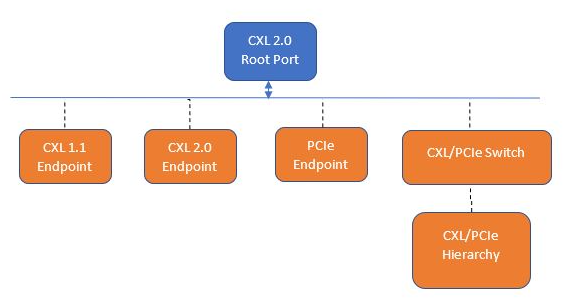

兼容性:CXL技術(shù)需要與現(xiàn)有的接口和協(xié)議兼容,以支持舊設(shè)備和系統(tǒng)的升級(jí)。這需要適當(dāng)?shù)?a target="_blank">轉(zhuǎn)換器和中間件。

為了解決這些挑戰(zhàn),可以采取以下方案:

標(biāo)準(zhǔn)化:制定統(tǒng)一的標(biāo)準(zhǔn)和規(guī)范,以確保不同廠商的設(shè)備和系統(tǒng)之間的兼容性和互操作性。

優(yōu)化設(shè)計(jì):通過優(yōu)化硬件和軟件設(shè)計(jì),提高性能和安全性。例如,增加硬件加速、內(nèi)存緩存和錯(cuò)誤糾正功能。

管理數(shù)據(jù)共享:采取適當(dāng)?shù)拇胧﹣砉芾碓O(shè)備之間的數(shù)據(jù)共享,例如訪問控制、認(rèn)證和加密。

提供中間件:提供轉(zhuǎn)換器和中間件,以支持現(xiàn)有系統(tǒng)的升級(jí)和兼容性。

07.?結(jié)論

更廣泛的應(yīng)用場景:隨著數(shù)據(jù)中心越來越重要,CXL技術(shù)將在更多的應(yīng)用場景中得到應(yīng)用,比如超級(jí)計(jì)算機(jī)、AI加速器、網(wǎng)絡(luò)加速器、NVMe SSD等。

更高的帶寬和更低的延遲:CXL技術(shù)支持更高的帶寬和更低的延遲,這使得它在處理大規(guī)模數(shù)據(jù)時(shí)具有優(yōu)勢。

更好的內(nèi)存擴(kuò)展性:CXL技術(shù)允許多個(gè)設(shè)備共享同一塊內(nèi)存,這極大地提高了內(nèi)存擴(kuò)展性和靈活性,在大型計(jì)算集群和超級(jí)計(jì)算機(jī)中應(yīng)用前景廣闊。

更好的兼容性:由于CXL技術(shù)基于PCIe協(xié)議,因此與現(xiàn)有的PCIe接口兼容。這使得CXL技術(shù)具有更好的兼容性和可擴(kuò)展性。

面向不同處理器架構(gòu):CXL技術(shù)可以支持x86、ARM和Power等不同的處理器架構(gòu),這為不同的系統(tǒng)提供了更多的選擇。

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論