設(shè)計概述

1.1 設(shè)計目的

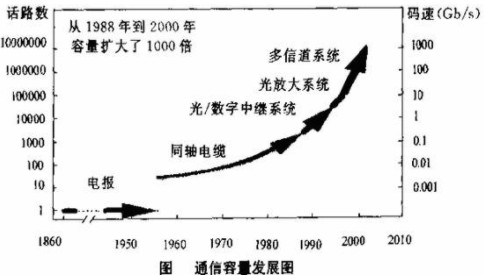

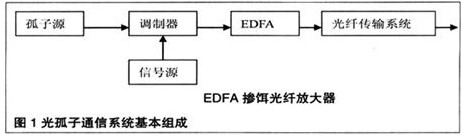

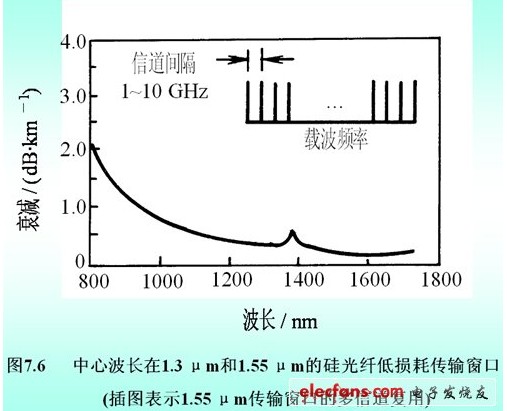

近年來,信息安全應用于生活中的各個領(lǐng)域。在光通信系統(tǒng)中,往往對速率 有著較高的追求。其中對光模塊,光纖通信中的傳輸算法,傳輸?shù)哪J揭约肮獠?段選取有密切關(guān)聯(lián)。隨著對帶寬,速率等要求日益增加,高速通信已經(jīng)成為基本 的要求。光纖通信因其具有低損耗,高抗干擾性,從而廣泛得到應用。近幾年由 于大量用戶數(shù)據(jù)的泄露,造成了極大的損失,使得信息安全成為人們關(guān)注的焦點。 目前光纖加密的研究多采用量子加密的方法,本人在中科大量子物理實驗室 下屬機構(gòu)問天量子實習發(fā)現(xiàn),目前國內(nèi)外在實際工程上存在很多漏洞,無法做到 光纖通信中的絕對安全,實現(xiàn)軍用和民用任重道遠。華為傳輸加密解決方案,采用 L1 層加密技術(shù),對業(yè)務層透明,采用高強度的 AES256 算法,確保各行業(yè)的數(shù)據(jù)安全性。此方案雖然實現(xiàn)簡單,但缺點是吞吐量小、端口少、速率低。 對于 ASE 算法的硬件實現(xiàn),國內(nèi)外研究學者大部分是基于 FPGA 的硬件實現(xiàn)。通過分析國內(nèi)外 ASE 在硬件上實現(xiàn)的研究現(xiàn)狀,我們想要用 FPGA 硬件實現(xiàn),達到 5Gbps 的傳輸速率,這是完全可行的。

1.2 應用領(lǐng)域

本作品應用前景廣泛。例如,各級市政機關(guān)之間在通信時,有些信息是需要嚴格加密的(如財務信息,公民戶籍隱私)。利用本設(shè)計進行加密后,即 便竊密者獲取到鏈路中的數(shù)據(jù),也只有窮舉才能破譯。同時,基于本設(shè)計的實時性,可以做到全雙工的突發(fā)式語音通話,幫助政務人員處理突發(fā)事件;或者運用 在軍事行動中,指揮中心與前線的通信往往具有簡潔,實時,突發(fā)的特點。本作品針對上述需求進行設(shè)計和驗證。改進后的基于混沌序列的 AES 算法具有高復雜度,可防止 SPADPA 攻擊。讓指揮信息能足夠保密,防止被敵人竊取。

1.3 主要技術(shù)特點

FPGA 設(shè)計加密算法具有安全性高,加密速度快,開發(fā)周期短,開發(fā)成本較低, 可重配,可靠性高以及移植性好等優(yōu)點。 系統(tǒng)鏈路部分采用 Aurora 協(xié)議,該協(xié)議是一款輕量級的光纖鏈路協(xié)議,具有冗余少,可定制度高,鏈路速率快等特點。

系統(tǒng)組成及功能說明

2.1 系統(tǒng)介紹

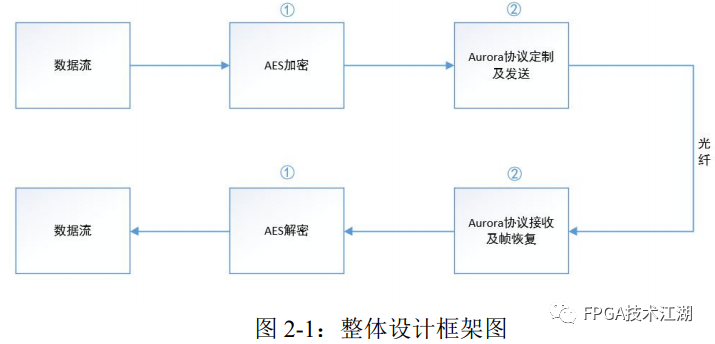

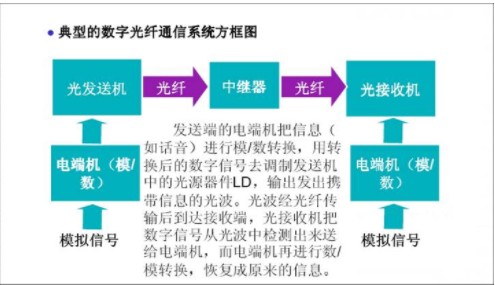

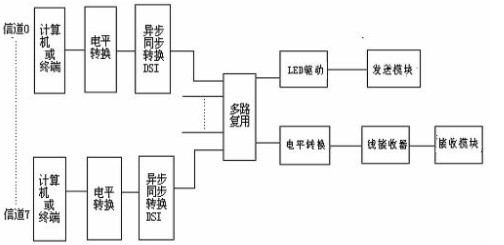

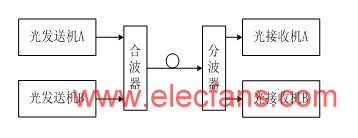

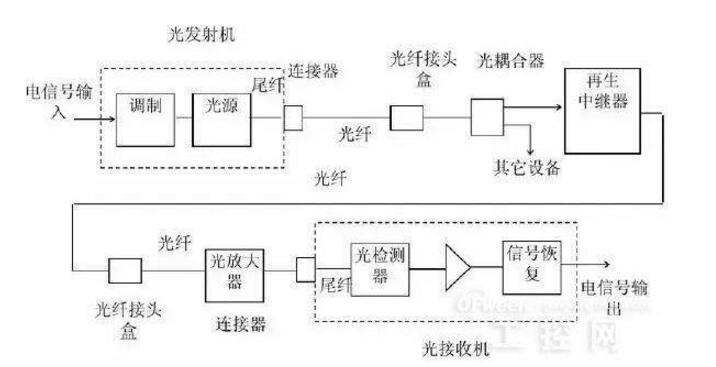

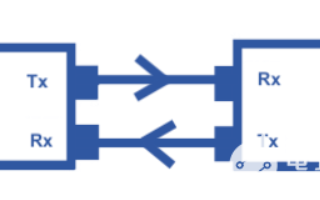

設(shè)計了一套完整的光纖通信加密系統(tǒng)(如圖 2-1)。系統(tǒng)鏈路部分采用 Aurora 協(xié)議,該協(xié)議是一款輕量級的光纖鏈路協(xié)議,具有冗余少,可定制度高,鏈路速率快等特點。加密協(xié)議采用目前 AES256 加密算法,該算法為目前國際最標準化加密算法之一,可抵抗所有已知的攻擊,并可在多個平臺上擁有速度快,編碼緊湊等特點。

2.2 各模塊介紹

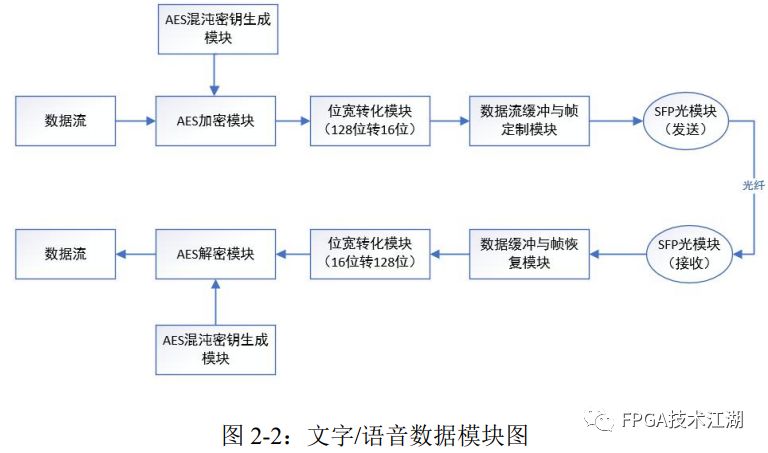

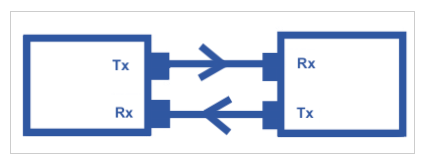

針對以上的框架,我們進行了模塊化設(shè)計,我們針對視頻流數(shù)據(jù)及語音/文字 數(shù)據(jù)設(shè)計了兩套不同的方案。 視頻流數(shù)據(jù)由于其需要高實時性,故我們摒棄了具有較高冗余度的幀結(jié)構(gòu)傳 輸方式,并對其采用外流水線設(shè)計進行傳輸(如圖 2-2);而語音/文字數(shù)據(jù)由于其數(shù)據(jù)流較少,往往對其安全性及正確性有更高的要求,故我們采用特定的幀結(jié)構(gòu), 針對該 AES 算法定制了其鏈路結(jié)構(gòu)(如圖 2-3)。 每一個模塊都對其進行了 modelsim 仿真及論證。FPGA 與光模塊通信的速率與數(shù)據(jù)校驗,我們通過 vivado 的 IBERT ip 核進行驗證;對光纖通信中的信號完整 性,我們通過眼圖進行觀察。

?

2.3 硬件電路設(shè)計

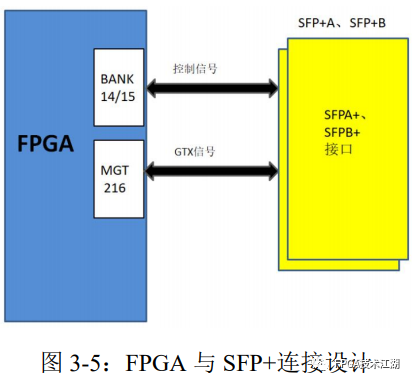

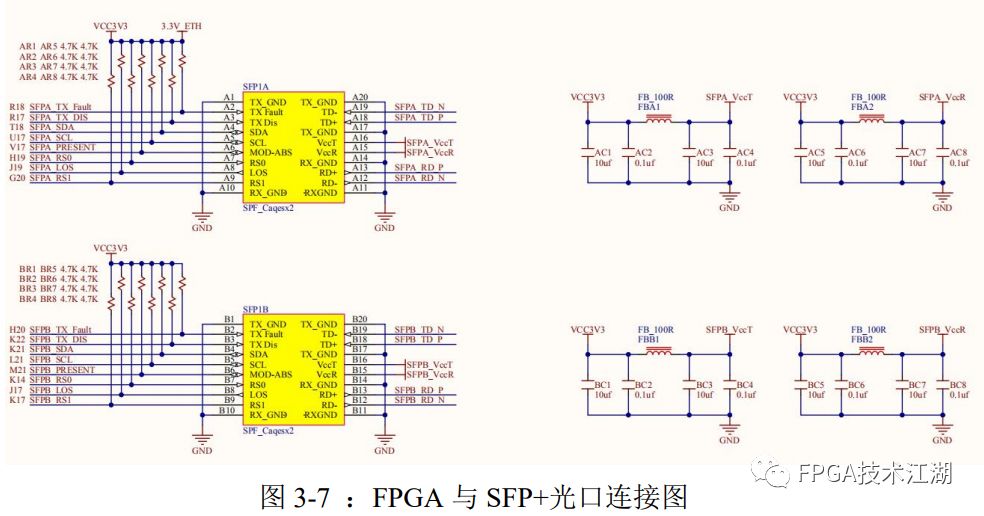

我們硬件電路設(shè)計主要體現(xiàn)在 SFP+光口與 FPGA 板卡之間的設(shè)計。如圖 3-5 所示。

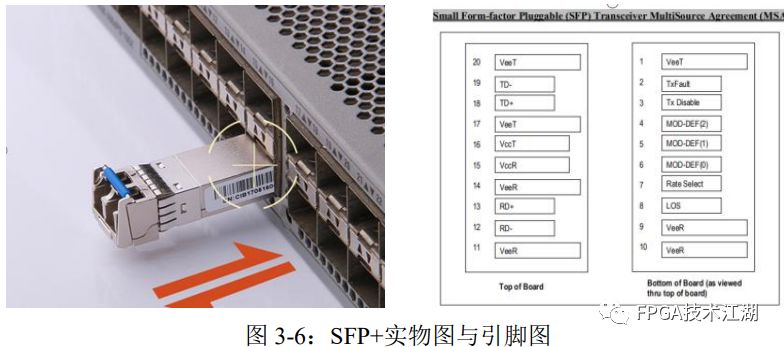

首先我們介紹所使用的光模塊。圖 3-6 所示為我們使用的 SFP 光口實物圖與引腳圖。使用的 SFP+的光模塊支持 8B/10B,也可支持 64B/66B 的長波(1310nm) 的單模光纖(SMF),有效傳輸距離為 2m 到 10km,事實上最高可達到 25km。光 口支持 SFP-MSA 協(xié)議,選用的光模塊支持 10GBase-LR/LW。

FPGA 與 SFP+光口的電路的原理圖設(shè)計如圖 3-7 所示。

作品難點與創(chuàng)新

3.1 AES 加密算法在 FPGA 上的實現(xiàn)

最常用的數(shù)據(jù)加密方式是軟件加密,即在通用微處理器上編程實現(xiàn),但其加 密速度普遍不高,算法實現(xiàn)的效率較低,安全性和可靠性有限,很多時候不能滿足用戶的需求。因此,需要更加快速,更加安全可靠的加密實現(xiàn)方式來滿足人們 在一些場合下的數(shù)據(jù)保密要求。 由于我們傳輸?shù)乃俾蔬_到 5Gbps,這種 GTP 高速接口下若使用 FPGA+ARM 架構(gòu)(如 ZYNQ),通過 ARM 完成加密算法將會使得我們效率大大降低,因此串 行通信實現(xiàn) AES 加密算法已經(jīng)不能滿足我們的需求,故我們采用純 PL 端 FPGA 設(shè)計來實現(xiàn)加密算法。FPGA 設(shè)計加密算法具有安全性高,加密速度快,開發(fā)周期短,開發(fā)成本較低,可重配,可靠性高以及移植性好等優(yōu)點。 3.2 混沌序列密鑰設(shè)計 混沌序列的產(chǎn)生主要有兩類:一類是利用微分方程表示的混沌系統(tǒng),產(chǎn)生時 間連續(xù)的混沌信號,系統(tǒng)由模擬電路來實現(xiàn),它對電路固有參數(shù)及信號再生的誤差很敏感,實際實現(xiàn)較困難。另一類是利用迭代方程(映射)或非線性數(shù)字濾波器結(jié)構(gòu)表示的混沌系統(tǒng),產(chǎn)生時間離散的混沌序列,系統(tǒng)由數(shù)字電路實現(xiàn),更適合在通信中應用。本設(shè)計需要在 FPGA平臺上實現(xiàn),鑒于 FPGA 無法處理連續(xù)時 間系統(tǒng),所以基于迭代方程來產(chǎn)生混沌序列,之后使用定點小數(shù)的方式對方程中的實數(shù)進行了處理,使其能在 FPGA 中進行運算。為了使該輸出混沌密鑰與發(fā)送 的明文產(chǎn)生時序相匹配,在輸出之前還做了部分拼接操作,使整體序列保密性更高。

3.3 AES 算法在光纖鏈路上的算法移植

算法移植通常是通過成熟的庫函數(shù)進行調(diào)用,該串行方式下一個時鐘周期只 能完成一條指令的實現(xiàn),算法移植相對簡單,不會出現(xiàn)異步跨時鐘域處理高速數(shù) 據(jù)等問題。我們選擇純 PL 端完成算法移植,在一個時鐘周期下,既要完成算法的 數(shù)據(jù)輸出,也要考慮到此刻光纖鏈路中傳輸狀態(tài)。因此我們的效率雖然大大提升, 但對我們的設(shè)計是一個巨大的挑戰(zhàn)。 針對速率匹配,數(shù)據(jù)對接,緩沖設(shè)計等問題,我們分別進行了模塊化設(shè)計, 分別對其進行仿真和上板測試。在軟件調(diào)試部分有詳細的分析和設(shè)計介紹。證明 我們的算法移植是成功的。

3.4 針對語音/文字等加密數(shù)據(jù)進行特定幀結(jié)構(gòu)定制

在算法移植過程中,我們針對 AES 算法對光纖協(xié)議進行了幀定制。傳統(tǒng)的幀 傳輸是對數(shù)據(jù)流進行傳輸,對固定長度的數(shù)據(jù)流加上幀頭幀尾進行判斷。一旦丟包,整個幀全部丟棄,造成了極大的浪費。 我們對原始的這種光纖幀協(xié)議進行了定制,在原來每一幀的基礎(chǔ)上,內(nèi)部對 其封裝了四個子幀,每一個子幀由 128 位組成(原因是我們每次加密的數(shù)據(jù)是 128 位)。對于每一個子幀,幀頭為起始的 16 位數(shù)據(jù),具有和其他 112 位數(shù)據(jù)不一樣 的脈寬長度,便于后續(xù)的幀解析。 通過我們的設(shè)計,即使傳輸過程中丟包,只會影響該當次的 128 位數(shù)據(jù),且 該設(shè)計給我們幀解析,加密算法的解碼提供了便利的平臺。

3.5 針對視頻流數(shù)據(jù)進行外流水線設(shè)計

外部循環(huán)流水線結(jié)構(gòu)由循環(huán)展開結(jié)構(gòu)發(fā)展而來。具體方法是在組合電路與每 一輪 加密運算對應的部件之間都插入額外的寄存器。該方法可以在同一時刻處理 多個數(shù)據(jù)分組,提高系統(tǒng)在單位時間內(nèi)處理數(shù)據(jù)的速度。 針對視頻流,采用 AES 內(nèi)外流水線設(shè)計,通過外流水線設(shè)計犧牲邏輯資源使 得加密傳輸速率提高 15 倍,傳輸速率可達 2.85Gbps。

3.6 接收端對幀數(shù)據(jù)恢復

光纖接收端設(shè)計部分除了會面臨數(shù)據(jù)流緩沖,高速率通信中異步跨時鐘域處 理等問題,還要剝離原始子幀結(jié)構(gòu),并且去除光纖本身的幀頭幀尾。除了我們的加密數(shù)據(jù),Aurora 協(xié)議本身還會不定期發(fā)送一些無效數(shù)據(jù),我們要對其進行數(shù)據(jù) 恢復,并且拼接光纖鏈路中的 16 位數(shù)據(jù),封裝成一個個的 128 位加密數(shù)據(jù)。這也是我們設(shè)計的一大難點。

3.7 高速通信中時序約束和信號完整性分析

對于 GTP 高速接口,我們對其做時序約束是非常有必要的。除此之外,還要 要用專業(yè)的軟件對光口進行測速,并對其信號質(zhì)量進行分析和評估。 我們使用 Seiral I/O Analyzer 連接到 IBERT 核,驗證高速串行通道的狀態(tài)。從 眼圖上可以觀察出碼間串擾和噪聲的影響較小,數(shù)字信號整體的特征良好,從而 判斷出系統(tǒng)具有非常良好的性能。 作品的難點與創(chuàng)新點部分設(shè)計,將會在第四部分(軟件設(shè)計與流程)中詳細 的闡述。

完成情況及軟件設(shè)計流程

4.1 AES 算法 IP 核設(shè)計

該部分我們分加密和解密兩塊來詳細說明。 加密: 為了驗證優(yōu)化后 AES 算法功能的正確性,需要選取測試向量進行驗證。我們 從官方的文檔中獲得參考基本功能測試向量。

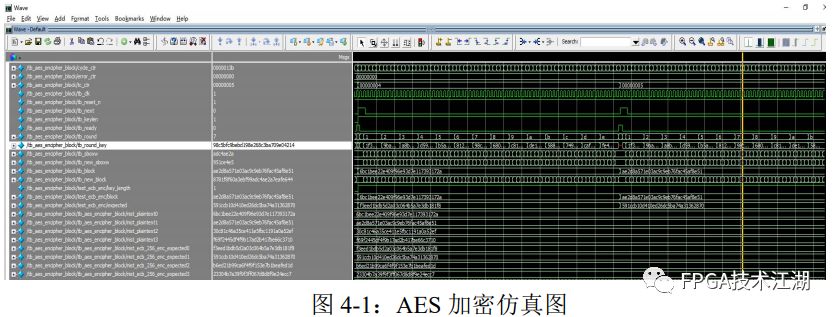

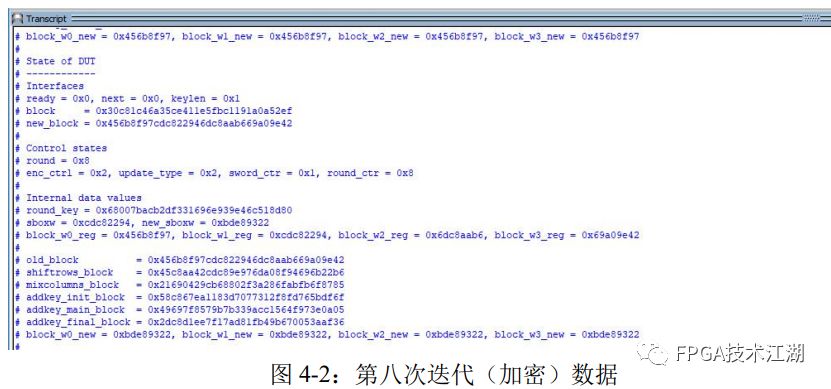

加密過程的 modelsim 仿真圖 4-1 所示:該部分畫面放大后可觀察到有以下重 要數(shù)據(jù): round(當前內(nèi)部循環(huán)的次數(shù)), tb_round_key (測試向量特工的循環(huán)密鑰值) tb_block (送入加密模塊的數(shù)據(jù)) tb_new_block (加密后輸出的數(shù)據(jù)) Sbox (加密所需的 s 盒數(shù)據(jù)) 由于數(shù)據(jù)比較龐大,我們將重要數(shù)據(jù)打印在了 modelsim 仿真的窗口,如圖 4-2 所示為第八次迭代循環(huán)加密過程的部分信息。

?

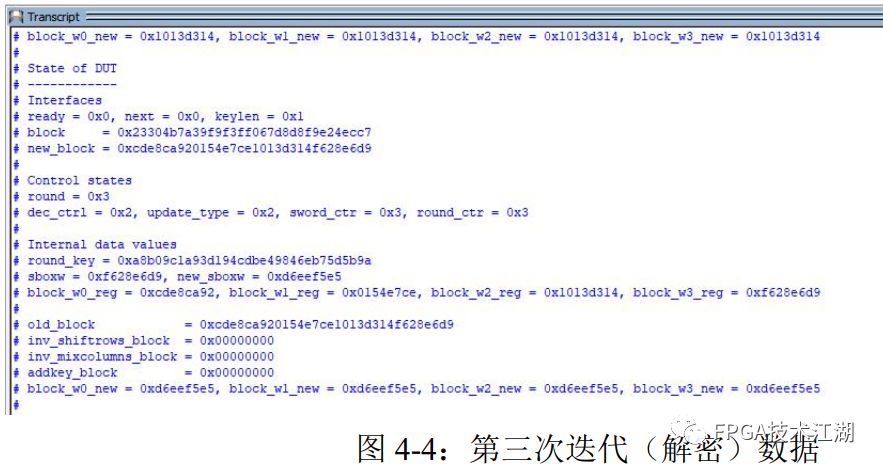

解密過程的 modelsim 仿真圖(如圖 4-3),該部分畫面放大后可觀察到有以下重要數(shù)據(jù):round(當前內(nèi)部循環(huán)的次數(shù)),tb_round_key (測試向量特工的循環(huán)密鑰值),tb_block (送入解密模塊的數(shù)據(jù)),tb_new_block (解密后輸出的數(shù)據(jù))。 由于數(shù)據(jù)比較龐大,我們將重要數(shù)據(jù)打印在了 modelsim 仿真的窗口,如圖 4-4 所示為第三次迭代循環(huán)解密過程的部分信息。

?

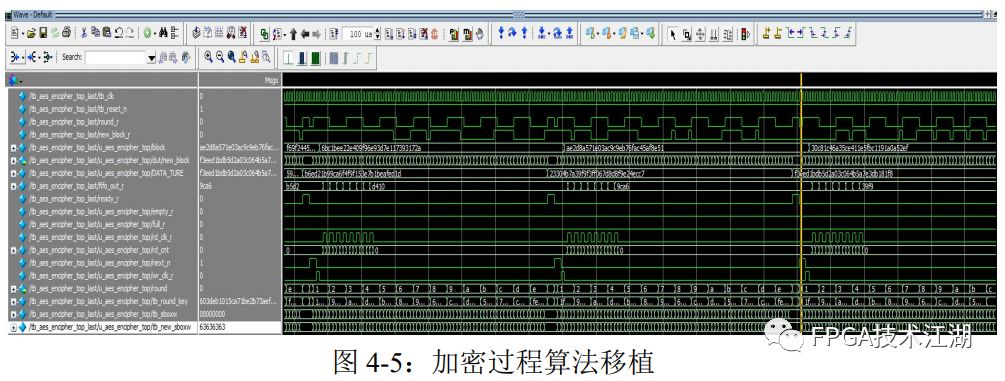

4.2 AES 算法在光纖鏈路上的算法移植

首先我們將 AES 算法分別封裝成加密、解密兩個 IP 核,內(nèi)部產(chǎn)生上述測試向 量、密鑰等數(shù)據(jù)。 加密后數(shù)據(jù)為 128 位位寬,由于光纖中傳輸?shù)臄?shù)據(jù)為 16 位位寬,故需要設(shè)計 一個位寬轉(zhuǎn)換模塊。 AES 加密后輸出速率與光纖傳輸速率不一致,為異步信號。我們設(shè)計了一個 FIFO 控制模塊,并調(diào)用了 IP 核進行設(shè)計。 我們在 vivado 中編譯 IP 核數(shù)據(jù),并調(diào)用 modelsim 觀察我們測試數(shù)據(jù),放大 圖 4-5 后可觀察以下重要數(shù)據(jù): block:送入的帶加密數(shù)據(jù) new_block :加密以后輸出的 128 位數(shù)據(jù)(每次加密迭代循環(huán)都有輸出) DATA_TURE:當加密完成后,根據(jù) ready 信號使能取出當前 128 位加密完成的數(shù)據(jù) fifo_out_r:將 128 位數(shù)據(jù)轉(zhuǎn)化成 16 位數(shù)據(jù),并從 FIFO 端輸出 next:使能拉高時,表示當前加密完成,可送入新的待加密數(shù)據(jù) ready :當前數(shù)據(jù)加密完成,可以讀取該數(shù)據(jù)

4.3 混沌序列密鑰設(shè)計

通過前文的分析,我們選擇了 logistic 模型。在 jupyter notebook IDE 上用 python 調(diào)用 matlab 庫設(shè)計了 logistic 模型,迭代 200 次生成的序列如圖 4-6。

改變不同的 u 值產(chǎn)生的模型仿真圖 4-7 如下(初值 X0=0.5):

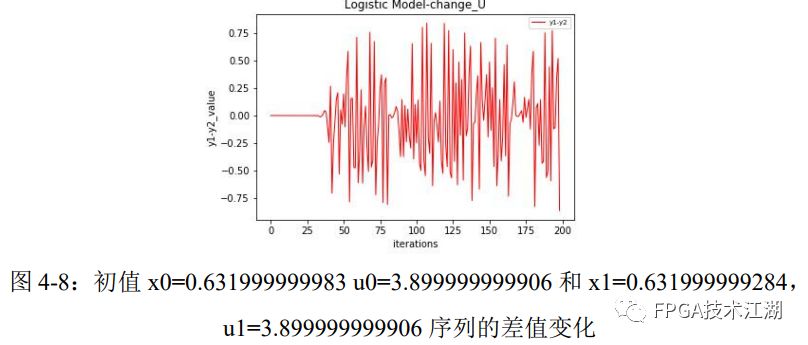

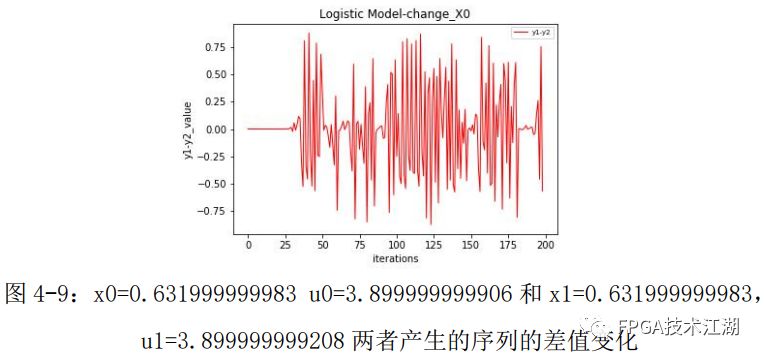

通過觀察當 u 的取值在 3.8~4.0 左右時模型進入混沌現(xiàn)象。 接著測試模型對初值的敏感程度,設(shè)置初值 x0=0.631999999983 u0=3.899999999906 和 x1=0.631999999284,u1=3.899999999906 兩者產(chǎn)生的序列的 差值變化如圖 4-8,設(shè)置初值 x0=0.631999999983 u0=3.899999999906 和 x1=0.631999999983,u1=3.899999999208 兩者產(chǎn)生的序列的差值變化如圖 4-9。

?

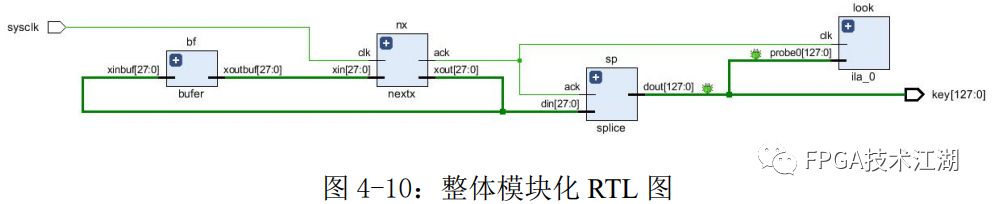

可以看出設(shè)置的初值僅僅只是相差 E-10,最后產(chǎn)生的序列相差很大。 將算法移植到 FPGA 平臺,包括每次迭代循環(huán)的計算模塊。為了避免模塊的 輸出直接又作為輸入引起實現(xiàn)違規(guī),將每次的輸出信號引出,在另一個模塊里緩 存。等待計算模塊計算完成時,將上一次的計算結(jié)果作為新的數(shù)據(jù)作為計算模塊 的輸入。另外為了靈活與加密解密模塊的數(shù)據(jù)位寬對接,設(shè)計了拼接模塊,可以 靈活定制輸出數(shù)據(jù)位寬與時序。整體模塊化 RTL 圖如圖 4-10。

對系統(tǒng)進行仿真結(jié)果如圖 4-11,時序和位寬都滿足要求:

設(shè)計完成后分析系統(tǒng)模型輸出數(shù)據(jù)的 Lyapunov 指數(shù)(簡稱李氏指數(shù)),它刻 畫非線性系統(tǒng)混沌特性的有效方法之一,只要李氏指數(shù)大于零,則系統(tǒng)是混沌的。最終在硬件上生成的數(shù)據(jù),通過軟件分析其李氏指數(shù)為 0.4953767618,驗證了該 模型為混沌系統(tǒng)。

4.4 針對語音/文字加密數(shù)據(jù)進行特定的幀定制

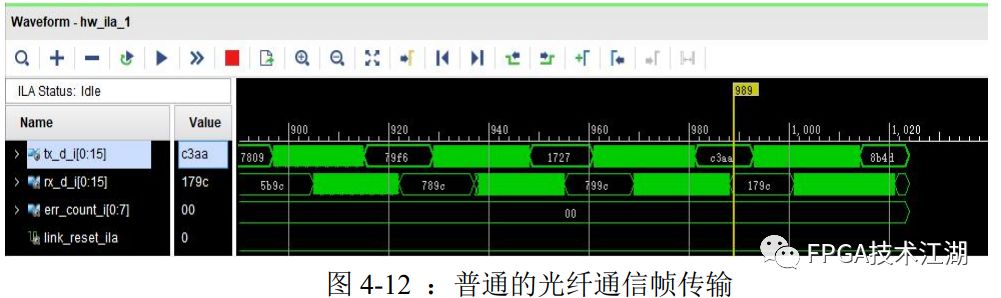

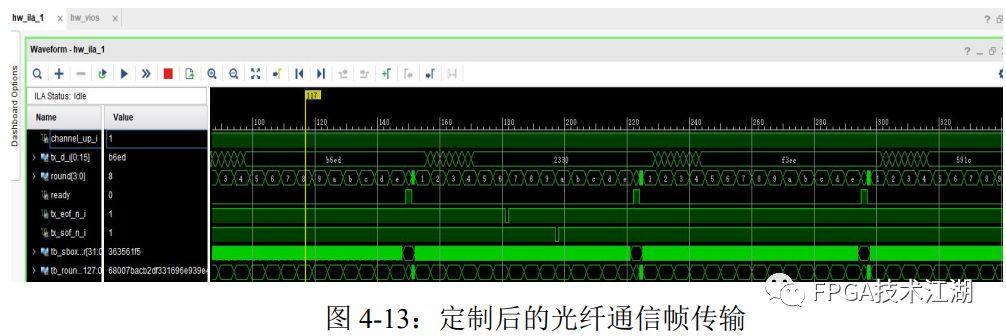

普通光纖傳輸?shù)膫鬏敺绞椒譃榱鱾鬏敽蛶瑐鬏敚鱾鬏斢捎谄洳豢煽啃裕?以及不適合控制和定制的特點,我們選擇了幀傳輸,如圖 4-12 為普通的光纖通信 幀傳輸。 由于加密數(shù)據(jù)為 128 位位寬數(shù)據(jù),而光纖中每次傳輸 16 位位寬數(shù)據(jù),故八次 傳輸周期傳輸一個 128 位的加密數(shù)據(jù)。如果采用普通的數(shù)據(jù)流傳輸?shù)脑挘坏┲?間有丟包,后續(xù)所有的數(shù)據(jù)將會錯誤,這在我們加密通信中是絕不允許的。 為了解決該問題,我們針對 AES 算法定制了一種幀結(jié)構(gòu)(如圖 4-13)。我們 將每一個 128 位加密數(shù)據(jù)作為一次傳輸?shù)膸Y(jié)構(gòu),而每次的前 16 位作為該幀結(jié)構(gòu) 的幀頭,這樣做的好處就是:1.幀結(jié)構(gòu)傳輸不容易產(chǎn)生誤碼和丟包 2.即使丟包 我們也不會影響下一個數(shù)據(jù)的傳輸。 我們在該項目的測試中,測試向量為上述四個 128 位數(shù)據(jù)循環(huán)發(fā)送。我們在 原來的幀結(jié)構(gòu)的基礎(chǔ)上,又封裝了一層光纖鏈路自帶的幀結(jié)構(gòu),以四個 128 位數(shù) 據(jù)為光纖傳輸?shù)囊粋€大幀結(jié)構(gòu)。保證了鏈路傳輸?shù)目煽啃浴?/p>

?

圖 4-13 中的 tx_d_i 信號為我們發(fā)送到鏈路中的數(shù)據(jù)信號,以 b6ed 為例,該 16 位數(shù)據(jù)為加密后的 3 號測試向量起始 16 位數(shù)據(jù),后面緊跟 7 個剩余的 16 位數(shù) 據(jù),組成一個完整的 128 位加密數(shù)據(jù)。通過我們的幀定制操作,極大的提高了我 們加密傳輸?shù)目煽啃浴?/p>

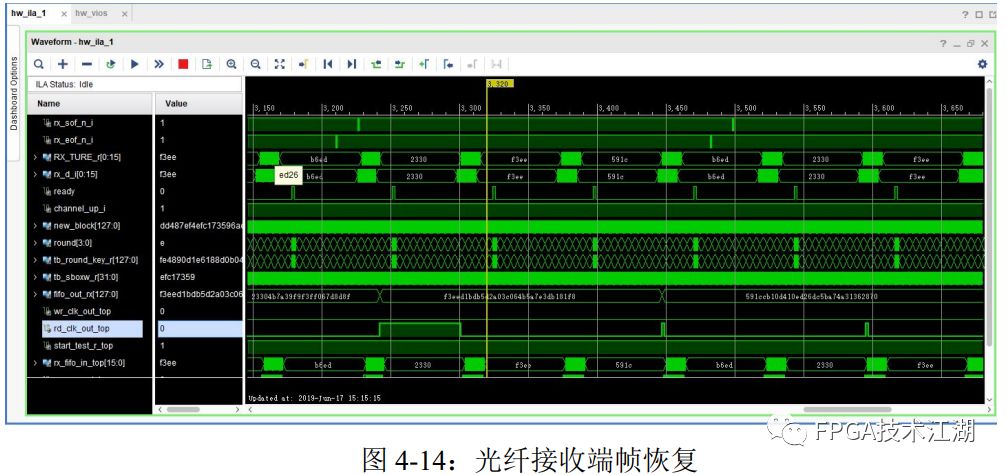

4.5 接收端對語音/文字加密數(shù)據(jù)幀數(shù)據(jù)恢復

接收端對幀數(shù)據(jù)進行恢復,去除定制的幀頭幀尾,并消除原有 Aurora 協(xié)議不 定時發(fā)送的無效數(shù)據(jù)帶來的誤碼。 如圖 4-14 所示,我們將光纖接收端接收到的數(shù)據(jù)(rx_d_i)接收下來,并將 其進行 16 位轉(zhuǎn) 128 位操作,輸出數(shù)據(jù)為 fifo_out_rx,我們對比測試向量的數(shù)據(jù)發(fā) 現(xiàn),我們的數(shù)據(jù)是正確無誤的。

4.6 發(fā)送端對視頻流數(shù)據(jù)進行外流水線設(shè)計

針對視頻流數(shù)據(jù),我們同時使用 15 個加密模塊,分別錯開一個周期進行同時 加密。如圖 4-15 藍色箭頭所指:每個加密模塊完成加密后,將加密數(shù)據(jù)送至寄存 器緩存,使得我們的加密效率提高了 15 倍。

系統(tǒng)綜合測試分析

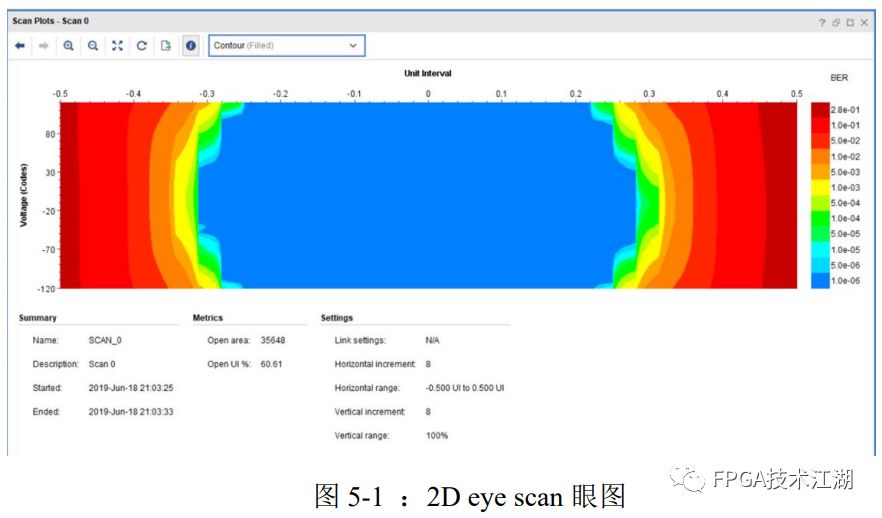

IBERT(Integrated Bit Error Ratio Tester)是 Xilinx 提供的用于調(diào)試 FPGA 芯片 內(nèi)高速串行接口的工具。它通過 JTAG 總線提供了 FPGA 到 Vivado Serial I/O Analyzer 的通道。通過 IBERT 用戶可以定制線速率、參考時鐘速率、參考時鐘來 源,總線寬度。它同時還額外需要一個系統(tǒng)時鐘,這個時鐘可以來自 GTX 收發(fā)器 或者其它 FPGA 管腳。 使用 IBERT 進行 GTP 通道的驗證有以下三個步驟: 1.生成 ibert 核:根據(jù)硬件高速串行總線的需求來定制和生成 iber 核。 2.使用上一步的 ibert 核自動生成 ibert 參考設(shè)計并生成 Bit 文件。 3.使用 Seiral I/O Analyzer 連接到 IBERT 核,并驗證高速串行通道的狀態(tài) 我們在 vivado 中生成該測試工具,對 SFP+光口實際發(fā)出的數(shù)據(jù)進行測速和信 號完整性分析。如圖 5-1 所示。我們可以在圖的正下方觀察到該鏈路的實際速率為 5Gbps,速率完全滿足我們的設(shè)計需求;誤碼率越低,顏色越偏向藍色(深藍色);當誤碼率越高,顏色越偏向紅色,眼圖張開的大小就代表信號質(zhì)量的好壞。我們 通過觀察眼圖可以發(fā)現(xiàn),藍色區(qū)域很大,且角度張開合理。結(jié)合圖 5-2,通過 5Gbps 速率的光纖傳輸 4.557E10 Bit 數(shù)據(jù)后,誤碼率僅為 2.195E-11,遠低于官方規(guī)定的 誤碼率 1.E-10 標準,可以得出結(jié)論:信號完整性分析良好,信號質(zhì)量傳輸可靠。

?

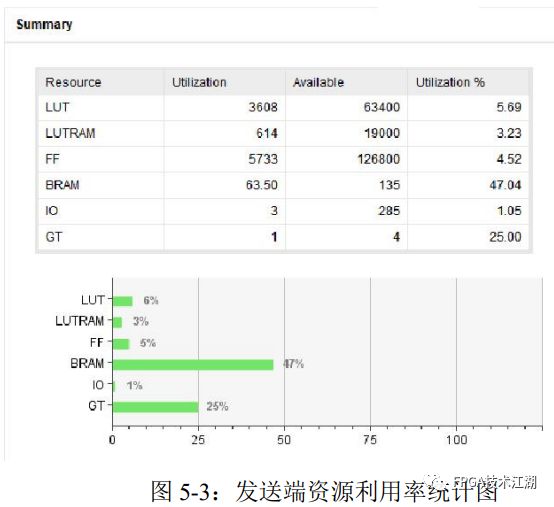

同時我們通過算法在硬件上的優(yōu)化,可以占用很少的資源到達所需要求,如 圖 5-3 和圖 5-4 所示,可以看出很低的資源利用率。

?

總結(jié)

本設(shè)計具有很高的實用價值,在保密通信領(lǐng)域,視頻安防監(jiān)控領(lǐng)域,軍用或 民用視頻/音頻傳輸領(lǐng)域,都有極強的應用場景。本次作品的難點和創(chuàng)新點在于: 1. AES 加密算法在 FPGA 上的實現(xiàn); 2. AES 算法在光纖鏈路上的算法移植; 3.針對 AES 算法在光纖發(fā)送端進行特定的幀定制; 4.針對視頻流做了外流水線設(shè)計,保證視頻數(shù)據(jù)低延遲傳輸; 5.混沌序列的設(shè)計; 6.高速通信中時序約束和信號完整性分析。 ? 參考文獻 [1] 7 Series FPGAs GTX/GTH Transceivers User Guide [2] Vivado Design Suite User Guide [3] Aurora 8B/10B v11.0 LogiCORE IP Product Guide [4] Small Form-factor Pluggable (SFP) Transceiver MultiSource Agreement (MSA) [5] Xilinx.Aurora 8B/10B Protocol Specification.Revision 2.2[M].Xilinx, 2010,10:16-90 [6] L.Henzen and W.Fichtner,"FPGA parallel-pipelined AES-GCM core for 100G Ethernet applications[C]", 2010 Proceedings of ESSCIRC, Seville, 2010, pp. 202-205. [7]趙文虎,王志功,費瑞霞,朱恩,吳微.基于邏輯設(shè)計的光纖通信 8B/10B 編解碼方法 研究[J].電路與系統(tǒng)學報,2003(02):48-53. [8]王志功.光纖通信系統(tǒng)超高速集成電路設(shè)計[J].中國科學,2000(03):35-40. [9]謝郁潔.基于 FPGA 的核間高速接口的設(shè)計與驗證[D].電子科技大學,2014. [10]何少恒.基于 SFP光纖通信接口的高速IQ數(shù)據(jù)傳輸系統(tǒng)設(shè)計與實現(xiàn)[D].中北大 學,2016. [11]王小偉.AES 加密算法的研究與 IP 核設(shè)計實現(xiàn)[D].哈爾濱工業(yè)大學,2013. [12]Yufeng Liu,Xiangyang Xu,Hao Su.AES Algorithm Optimization and FPGA Implementation[J].IOP Conference Series: Earth and Environmental Science,2019,267(4). [13]楊靜.一種 AES 算法加密傳輸系統(tǒng)的設(shè)計與實現(xiàn)[J].電子設(shè)計工 程,2019,27(03):123-126+131. [14]何德彪,胡進,陳建華.基 FPG 的高 AE 實現(xiàn)[J].華中科技大學學報(自然科學 版),2010,02:101-104. ?

審核編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論