引言

時序抖動和時序噪聲屬于人們了解甚少的工程概念,而它們又是模擬設計和數字設計中最重要的參數。尤其是在高速通信系統中,惡劣的抖動性能會導致更高的誤碼率,并限制系統速度。時序抖動一般定義為數字信號在某一重要時刻相對于其理想時間位置的短時間偏離。有若干因素會影響隨機時序抖動,包括寬帶噪聲、相位噪聲、雜散信號、壓擺率、帶寬。相位噪聲和寬帶噪聲都是隨機的,而雜散信號是由串擾和電源耦合等各種可確定的干擾信號導致的確定性響應。如同本文稍后提到的那樣,壓擺率和帶寬也影響抖動。圖1描繪了一條非理想的正弦曲線,它包含了這三種噪聲源。圖2顯示了一個數字信號,伴隨的抖動隨時間而積累。本文旨在解釋和論證時序抖動和這三種噪聲源之間的直接關系。

圖1. 對時序抖動產生影響的三個噪聲源。

圖2. 時鐘信號內的隨機噪聲與雜散信號導致的抖動。抖動會隨時間積累。

寬帶噪聲對時序抖動的影響

正弦波的抖動所有電子元件都產生寬帶噪聲,尤其是放大器和邏輯器件。寬帶噪聲也稱作噪聲底,是散粒噪聲和熱噪聲的結合。散粒噪聲在二極管和晶體管中很常見,是由電荷穿越半導體結的勢壘時的隨機跳躍導致的。另一方面,熱噪聲不受電流的影響。它是由載波的隨機熱運動導致的,例如在MOSFET的柵極和通道阻抗范圍內。熱噪聲功率與阻抗和溫度成正比。

隨著現代元件的工作帶寬進入數千兆赫茲范圍,寬帶噪聲對時序抖動的影響變得相當突出。例如,一個寬帶放大器驅動器的帶寬是40GHz,噪聲系數是10dB,小信號增益是20dB,輸出功率是0dBm,則它產生的噪聲輸出是-38dBm (-174dBm + 10dB + 20dB + 10log10(40GHz))。這導致38dB的信噪比(SNR)。在這個SNR水平,寬帶噪聲就是時序抖動的重要影響因素。總均方根(RMS)噪聲電壓是噪聲底在頻帶內的積分。圖3說明了RMS噪聲是如何轉化為時序抖動的。

圖3. 噪聲電壓y穿越0V,使信號提前t達到閾值,從而產生了抖動。

從數學上來說,可以用下面的公式表示包含寬帶白噪聲的正弦波:

其中A為振幅,是角頻率,vn(t)為時刻t處的噪聲電壓。隨機噪聲vn(t)具有高斯(正態)分布。噪聲電壓(vn)的概率分布(vn)為:

其中(vnRMS)為RMS噪聲電壓。為了理解噪聲電壓是如何轉換為時序抖動的,可考慮把y(t)施加到抖動測量儀器(如帶直方圖功能的采樣示波器)的輸入端。每次y(t)穿越0V閾值時,直方圖上就增加一個數據點。正如圖3所示,在時間t內,存在噪聲信號y達到閾值的可能,因此抖動被加到直方圖中,時間比預期的采樣點早或晚t。概率密度為時序抖動t的函數,是通過在公式2中設置vn = y = Asin(2t)來計算的。結果就是抖動分布函數,如直方圖所示。

假設t相比正弦曲線周期而言很小,那么可以對公式3進行簡化,得到:Asin(2t A(2t = At。

公式3可變為:

把公式4中各項的分子和分母同除以A,得到:

公式5為抖動分布函數,除比例因子1/A外,它與公式2中的高斯分布相似,因此,得到的RMS抖動為:

圖4所示的測試裝置用來驗證公式6。純正弦波信號和寬帶噪聲信號相互疊加,然后輸入采樣示波器,它在零交叉處測量抖動。為了確保測試結果有意義,設置的輸入寬帶噪聲要高于示波器的噪聲底。圖5和圖6顯示了實驗結果。圖5表明在RMS噪聲恒定時,抖動是頻率的函數;圖6表明頻率恒定時,抖動是RMS噪聲的函數。測量得到的抖動曲線和計算得到的抖動曲線之間具有相似性,證明公式6可用來把寬帶噪聲轉化成時序抖動。

圖4. 抖動測試裝置#1:噪聲和純正弦波信號疊加。

圖5. 在RMS噪聲一定的情況下,抖動為頻率的函數。

圖6. 在頻率一定的情況下,抖動為RMS噪聲電壓的函數。

普通波形的抖動

經過稍微修改,公式6還能用于其他波形的抖動轉化。根據定義,公式6中的A項是0V閾值時的壓擺率S。只要已知該閾值處的壓擺率,任何波形都可用于求出t與y之間的關系,這是因為vn = y = St (圖3)。把它代入公式2得到公式7:

把公式7中各項的分子和分母同除以S,得到:

除比例因子1/S外,公式8與公式2中的高斯分布相似,因此,得到的RMS抖動為:

圖4所示的測試裝置再次用于驗證公式9。正弦波曲線用一個壓擺率可變的方波代替。在方波上升沿的50%處測量抖動。圖7所示結果表明公式9是正確的。

圖7. 在方波上升沿的50%處測量抖動。

圖7中給出的信息引出了一個有趣的現象。似乎波形的壓擺率越快,產生的抖動越小。然而,較快的壓擺率要求較高的工作帶寬,這增加了系統中的RMS噪聲。因為RMS噪聲與帶寬成正比,因此系統設計者必須仔細選擇壓擺率和帶寬,來使抖動降到最低程度。

相位噪聲對時序抖動的影響

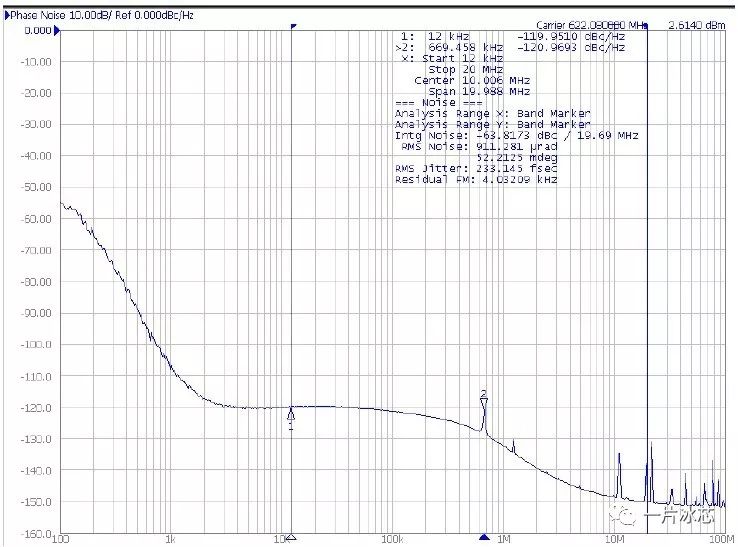

相位噪聲存在于任何有源元件和無源元件中,但它在振蕩器中表現最為嚴重。這些振蕩器包括晶體自激振蕩器和時鐘恢復應用中的鎖相振蕩器。相位噪聲是一種描述頻譜純度的指標。例如,理想情況下,振蕩器輸出應該是一條純正弦曲線,表示為頻域中位于某個單一頻率的垂線。然而,在現實情況中,振蕩器存在一些噪聲源,它們會導致輸出頻率偏離其理想位置,因此在載波(基波)頻率附近,產生了一個其他頻率的“裙邊”效應(圖8)。這些頻率被稱作相位噪聲,是由對振蕩器進行調制的噪聲源引起的。它們的電平通常比噪聲底高,頻率接近載波頻率。相位噪聲通常被指定為偏離載波的某個頻率處的噪聲功率與載波功率之比,在1Hz帶寬之內。由于相位噪聲來自于噪聲源對信號的頻率調制,因此相位噪聲不受壓擺率的影響。

圖8. 由于振蕩器的噪聲頻率調制,輸出頻譜中出現“裙邊”效應。

受大多數抖動測量設備能力所限,與測量低噪聲信號在時域中的抖動相比,通常更容易通過測量它在頻域中的相位噪聲來確定其純度。例如,多數抖動測量示波器只能測量低達1psRMS的抖動。大多數實時示波器的帶寬僅為7GHz。而另一方面,相位噪聲設備能獲得目前最佳的低噪聲示波器的噪聲測量水平(在時域中遠小于1ps),并提供高達40GHz的帶寬。

在早期的文章[1-2]中我們已經探討了相位噪聲和時序抖動的轉換問題。為了得到相位噪聲與抖動的關系式,可以考慮把公式10作為一個帶有相位噪聲的正弦曲線:

其中A是振幅, fo是額定頻率, (t)為相位噪聲。通常在兩個或多個周期之間的0V交越處測量抖動。在0V交越處, 公式10括號內的各項為2N:

其中t1為第一個零交越時刻,t2為第N個零交越時刻。兩個公式相減得出:

兩個交越點之間的時間為周期數量加上抖動:

TO為周期,即1/fO,t是N個周期后積累的抖動。把公式14代入公式13得:

重新整理公式15,并消去2N項,得到抖動:

RMS抖動的平方為:

因為(t)是個穩態過程,所以:

其中S()為(t)的頻譜密度,f為偏移(傅立葉)頻率。公式17的中間項變為:

其中R()是()的自相關函數,是經過 NTo個周期后的時間。經過N個周期后,在時刻RMS抖動的平方為:

利用代數公式1 - cos(2 = 2sin2(),并假設相位噪聲接近載波并且對稱(就是從-fOFFSET到0的積分等于0到+fOFFSET的積分),公式20可以重寫為:

S()近似等于相位噪聲L() [3];也就是說,傅立葉頻偏比載波頻偏小得多: fOFFSET << fO。

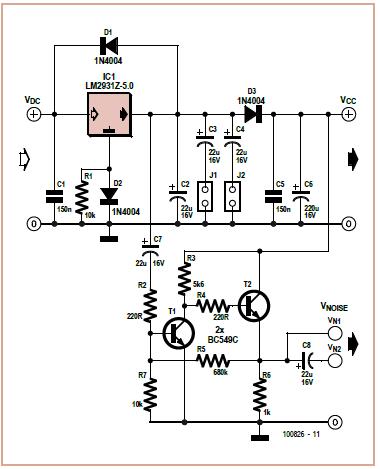

為了驗證公式22,使用了一個相位調制電路[4],它是圖9所示測試裝置的一部分。相位調制電路可以非常方便地產生無雜散、可變相位噪聲信號。首先,利用采樣示波器針對時序抖動測量該電路的輸出,然后用頻譜分析儀(沒有畫出)針對相位噪聲測量其輸出。圖10顯示了該電路的相位噪聲圖。它類似于鎖相振蕩器的噪聲圖,在這種振蕩器中,相位噪聲在環路帶寬內是恒定的,并在帶外滾降。圖11給出了使用數值積分對公式22求積分后得到的相對于周期的累積抖動。圖11中的曲線證實了公式22的正確性。

圖9. 抖動測試裝置#2:使用相位調制器產生相位噪聲和抖動。

圖10. 相位調制電路的相位噪聲圖形。

圖11. 圖形顯示的是相對于周期的累積抖動,證實了公式22的正確性。

雜散噪聲對時序抖動的影響

雜散信號也對時序抖動有影響,尤其是在振蕩器中。雜散信號是由鎖相環基準的雜散信號、電源耦合、相鄰電路的串擾、噪聲源引起的。如圖1所示,這些雜散信號通常表現為載波頻率附近的小尖峰。公式22有助于建立雜散信號和時序抖動的關系。由于雜散只發生在特定頻率,因此公式22中的積分函數可以用總和來代替:

同樣, NTo為經過N個周期的時間。由于公式23未假定雜散信號是對稱的,所以要乘的系數為4而不是8。在計算抖動時,載波兩側的雜散信號都必須包含在內。L(fn)為雜散信號相對于載波(預期信號)的振幅,通常以dBc為單位。fn為n次諧波的頻率偏移。圖12是公式23的波形圖,使用載波兩側的雜散信號,頻偏為100kHz,振幅為-40dBc。參考文獻1中驗證了公式23,方法是用一條正弦波調制一個壓控晶體振蕩器,產生載波兩側的雜散信號(沒有畫出)。

圖12. 公式23的曲線,顯示了載波兩側產生的雜散信號。

總抖動

如前所述,寬帶噪聲、相位噪聲、雜散信號是時序抖動的三個影響因素。寬帶噪聲是純粹隨機和非相干的,因此它產生的抖動不累積。然而,后兩者一般都產生累積抖動。總時序抖動的平方等于三種抖動的平方和。

結束語

實驗數據和計算數據之間的一致性證明了三種主要噪聲源和時序抖動之間的關系。高速系統的設計人員可以利用公式9、22和23把噪聲轉化成時序抖動。附錄:計算RMS噪聲電壓

如果已知某種電子器件的一項或幾項常規噪聲規格,那么可以通過多種方法來確定它的總RMS噪聲電壓。表1列出了一些元件制造商們通常提供的噪聲指標。

| Component | Noise Specification | Unit |

| Amplifier | Residual noise-floor power density | dBm/Hz |

| Noise figure | dB | |

| Input referred noise density | nV/Hz | |

| Oscillator | Phase noise floor | dBc/Hz |

如果給定了噪聲密度,就可以通過在有效帶寬上對噪聲密度進行積分來估算總RMS噪聲,公式如下:

系統的典型負載阻抗ZO為50,PRMS為RMS噪聲功率,BW為帶寬,NOISE-FLOOR是以dBm/Hz為單位的噪聲底密度。例如,一個放大器的帶寬為10GHz,輸出噪聲密度為-150dBm/Hz,則它產生的總RMS噪聲電壓為707μVRMS:

噪聲系數(NF)常用于描述低噪聲放大器和功率放大器噪聲性能。可以從噪聲系數推導出噪聲底密度,方法是把它與50電阻的熱噪聲相加,再加上系統增益,公式如下:

例如,一個噪聲系數為10dB、小信號增益為20dB的放大器的噪聲底密度為-144dBm/Hz。

已知噪聲密度,就可以推出總噪聲電壓。

另一方面,運算放大器噪聲特性的表現形式通常是輸入參考噪聲,單位為nV/Hz。假定噪聲電流可忽略,信號源阻抗遠小于放大器輸入阻抗,那么總RMS噪聲可通過下面公式計算:

例如:一個輸入噪聲密度為8nV/Hz、小信號增益為20dB、帶寬為1GHz的放大器產生的噪聲電壓為800μVRMS:

振蕩器的相位噪聲的單位通常為dBc/Hz。dBc單位表示輸出噪聲對期望信號功率的歸一化。下面的公式可用于計算總RMS噪聲電壓:

其中PSIG為振蕩器的輸出功率。例如,某個振蕩器在50產生的功率為10dBm,輸出相位噪聲底為-150dBc/Hz、有效帶寬為100MHz, 則輸出噪聲電壓為224mVRMS:

參考文獻

- Ali Hajimiri et. al., "Jitter and Phase Noise in Ring Oscillators," IEEE Journal of Solid-State Circuits, Vol. 34, No. 6, pp. 790-804.

- Boris Drakhlis, "Calculate Oscillator Jitter By Using Phase-Noise Analysis," Microwaves & RF, Jan. 2001 pp. 82-90 and p. 157.

- W. F. Egan, Frequency Synthesis by Phase Lock. New York: Wilen, 1981.

- Enrico Rubiola et. al., "The ±45° Correlation Interferometer as a Means to Measure Phase Noise of Parametric Origin" IEEE Transactions On Instrumentation and Measurement, Vol. 52, No. 1, pp. 182-188.

電子發燒友App

電子發燒友App

評論