當需要增加網絡保護元件,或者需要信號穿過連接器,或者有其他的PCB要求時,常常需要調整發送波形。

T1和E1發送波形的可編程區段

通過DS26334和DS26324的內部寄存器,我們可以對發送脈沖的兩個主要屬性進行控制:幅度和定時。T1和E1發送脈沖被劃分為多個區段,各個區段都可分別控制以提供滿足要求的波形。 圖1顯示了T1脈沖是如何分段的,以及控制每一區段的寄存器。圖2是E1脈沖的類似信息。

T1和E1發送波形的幅度控制

DS26334和DS26324發送脈沖的幅度可通過以下兩種方法進行控制。- 調整DAC增益

利用LITXLAE寄存器位DAC[3:0],可同時對所有T1或者E1電平進行正向和負向調整。 - 局部波形電平調整

通過電平調整寄存器中的WLA[3:0]位,可以對波形的特定區段進行細調。電平調整的步長與所設的DAC增益成正比。如果DAC增益增加10%,步長也相應增加10%。

T1和E1發送波形定時控制

DS26334和DS26324發送脈沖電平的定時受控于電平調整寄存器中的CEA[2:0]位。可以正向和負向調整每一邊沿,增量為TCLK的1/32。

一般性建議

調整DAC增益是控制發送脈沖幅度的最簡單的方法,因為只修改一個寄存器便可以控制整個波形。在進行波形調整時首先調整DAC增益,然后再調整各個獨立的電平調整寄存器(如果需要的話)以獲得滿足要求的波形,這樣可以使總的調整量最少。VDD影響DAC的最大輸出。VDD電平較低時,可能達不到最大DAC增益設置。調整VDD也會影響線路驅動輸出級的最大電壓。

負數不使用帶符號整數表示。最高位是符號位,低位代表幅度,與符號無關。例如,-3在WLA[3:0]寄存器中表示為1011b (bit 3為1代表負數,后面三個比特011是數值大小3),而不是1101b (4比特帶符號整數)。

圖1. T1脈沖分段控制

T1脈沖分段控制

- 過沖(1)

寄存器LTXLAA WLA[4:0] - 時鐘沿(1CE)

寄存器LTXLAA CEA[2:0]

(1CE) = 從過沖至平臺時鐘沿 - 平臺(2)

寄存器LTXLAB WLA[4:0] - 時鐘沿(2CE)

寄存器LTXLAB CEA[2:0]

(2CE) = 從平臺至下降時鐘沿 - 下沖(3)

寄存器LITXLAC WLA[4:0] - 時鐘沿(3CE)

寄存器LITXLAC CEA[2:0]

(3CE) = 下降沿至下沖(3)結束的時鐘沿 - 下沖(4)

寄存器LITXLAD WLA[4:0] - 時鐘沿(4CE)

寄存器LITXLAD CEA[2:0]

(4CE) = 下沖(3)結束至下沖(4)結束的時鐘沿 - 下沖(5)

寄存器LITXLAC WLA[4:0]

圖2. E1脈沖分段控制

E1脈沖分段控制

- 過沖(1)

寄存器LTXLAA WLA[4:0] - 時鐘沿(1CE)

寄存器LTXLAA CEA[2:0]

(1CE) = 過沖至平臺的時鐘沿 - 平臺(2)

寄存器LTXLAB WLA[4:0]

- 時鐘沿(2CE)

寄存器LTXLAB CEA[2:0]

(2CE) = 平臺至下降沿的時鐘沿

注: 在E1模式中,沒有使用寄存器LITXAC、LITXAD和LITXAE。

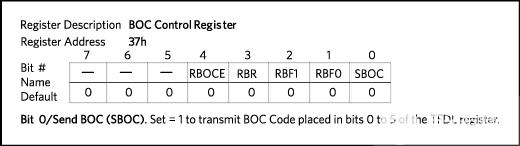

LIU測試寄存器說明

寄存器名稱:ADDP寄存器說明:地址指針

寄存器地址:1Fh, 3Fh

| Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Name | ADDP7 | ADDP6 | ADDP5 | ADDP4 | ADDP3 | ADDP2 | ADDP1 | ADDP0 |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Bit 7至0: 地址指針(ADDP)。該指針用于切換到主寄存器、第二寄存器、個體寄存器、BERT寄存器和所有測試寄存器的指向。(參見表1分區選擇和表2 LIU測試分區寄存器。)

表1. 地址指針分區選擇

| ADDP @ 1Fh ADDP7 to ADDP0 (Hex) |

LIU 1-8 Bank Name |

| 00 | Primary bank |

| AA | Secondary bank |

| 01 | Individual LIU bank |

| 02 | BERT bank |

| 03 | Reserved |

| 04 | LIU1 test bank |

| 05 | LIU2 test bank |

| 06 | LIU3 test bank |

| 07 | LIU4 test bank |

| 08 | LIU5 test bank |

| 09 | LIU6 test bank |

| 0A | LIU7 test bank |

| 0B | LIU8 test bank |

| ADDP @ 3Fh ADDP7 to ADDP0 (Hex) |

LIU 9-16 Bank Name |

| 00 | Primary bank |

| AA | Secondary bank |

| 01 | Individual LIU bank |

| 02 | BERT bank |

| 03 | Reserved |

| 04 | LIU9 test bank |

| 05 | LIU10 test bank |

| 06 | LIU11 test bank |

| 07 | LIU12 test bank |

| 08 | LIU13 test bank |

| 09 | LIU14 test bank |

| 0A | LIU15 test bank |

| 0B | LIU16 test bank |

表2. LIU 1測試分區(各LIU相同)

| Addr | Abbr | Description |

| 00 | L1TXLAA | LIU 1 Tx level adjust A (test register) |

| 01 | L1TXLAB | LIU 1 Tx level adjust B (test register) |

| 02 | L1TXLAC | LIU 1 Tx level adjust C (test register) |

| 03 | L1TXLAD | LIU 1 Tx level adjust D (test register) |

| 04 | L1TXLAE | LIU 1 Tx level adjust E (test register) |

LIU測試寄存器文檔詳細說明

每個LIU的這些寄存器在一個分區中。寄存器名稱:LTXLAA

寄存器說明:LIU Tx電平調整A (過沖電壓)

寄存器地址:00H

讀/寫功能:R/W

| Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Name | WLA4 | WLA3 | WLA2 | WLA1 | WLA0 | CEA2 | CEA1 | CEA0 |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Bit 7至3: 發送波形輸出電平1調整(WLA[4:0])。在±360mV范圍內調整默認幅度。

Bit 7 = 符號位("1"表示負)

Bit 6至3 = 數值(無符號)

LSB步長為24mV

Bit 2至0: 時鐘沿調整(CEA[2:0])。在±3 32x-clks范圍內移動默認時鐘沿。

<2> = 符號位("1"表示負)

<1:0> = 移動時鐘沿32x-clks的數量(無符號)

寄存器名稱:LTXLAB

寄存器說明:LIU Tx電平調整B (平臺電壓)

寄存器地址:01H

讀/寫功能:R/W

| Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Name | WLA4 | WLA3 | WLA2 | WLA1 | WLA0 | CEA2 | CEA1 | CEA0 |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Bit 7至3: 發送波形輸出電平2調整(WLA[4:0])。在±360mV范圍內調整默認幅度。

Bit 7 = 符號位("1"表示負)

Bit 6至3 = 數值(無符號)LSB步長為24mV

Bit 2至0: 時鐘沿調整(CEA[2:0])。在±3 32x-clks范圍內移動默認時鐘沿。

<2> = 符號位("1"表示負)

<1:0> =移動時鐘沿32x-clks的數量(無符號)

寄存器名稱:LITXLAC

寄存器說明:LIU Tx電平調整C (下沖電壓#1)

寄存器地址:02H

讀/寫功能:R/W

| Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Name | WLA4 | WLA3 | WLA2 | WLA1 | WLA0 | CEA2 | CEA1 | CEA0 |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Bit 7至3: 發送波形輸出電平3調整(WLA[4:0])。在±360mV范圍內調整默認幅度。

Bit 7 = 符號位("1"表示負)

Bit 6至3 = 數值(無符號)

LSB步長為24mV

Bit 2至0: 時鐘沿調整(CEA[2:0])。在±3 32x-clks范圍內移動默認時鐘沿。

<2> = 符號位("1"表示負)

<1:0> = 移動時鐘沿32x-clks的數量(無符號)

寄存器名稱:LITXLAD

寄存器說明:LIU Tx電平調整D (下沖電壓#2)

寄存器地址:03H

讀/寫功能:R/W

| Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Name | WLA4 | WLA3 | WLA2 | WLA1 | WLA0 | CEA2 | CEA1 | CEA0 |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Bit 7至3: 發送波形輸出電平4調整(WLA[4:0])。在±360mV范圍內調整默認幅度。

Bit 7 = 符號位("1"為負)

Bit 6至3 = 數值大小(無符號)LSB步長為24mV

Bit 2至0: 時鐘沿調整(CEA[2:0])。在±3 32x-clks范圍內移動默認時鐘沿。

<2> = 符號位("1"表示負)

<1:0> = 移動時鐘沿32x-clks的數量(無符號)

寄存器名稱:LITXLAE

寄存器說明:LIU Tx電平調整E (下沖電壓#3)

寄存器地址:04H

讀/寫功能:R/W

| Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Name | WLA4 | WLA3 | WLA2 | WLA1 | WLA0 | CEA2 | CEA1 | CEA0 |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Bit 7至4: 輸出波形電平5調整(WLA[3:0])。在±180mV范圍內調整默認幅度。

Bit 7 = 符號位("1"表示負)

Bit 6至4 = 數值(無符號)

LSB步長為24mV

Bit 3至0: DAC增益調整(DAC[3:0])。

以下設置修改DAC增益。

0000 - 正常DAC增益(默認)

0001 - DAC增益+2.6%

0010 - DAC增益+5.3%

0011 - DAC增益+8%

0100 - DAC增益+11.1%

0101 - DAC增益+14.2%

0110 - DAC增益+17.7%

0111 - DAC增益+21.3%

1000 - DAC增益-2.2%

1001 - DAC增益-4.88%

1010 - DAC增益-7.11%

1011 - DAC增益-8.88%

1100 - DAC增益-11.11%

1101 - DAC增益-12%

1110 - DAC增益-15.1%

1111 - DAC增益-16.4%

T1和E1發送波形數據

以下數據由DS26324DK獲得,能夠代表DS26334和DS26324的預期結果。提供這些數據是為了作為一個參考,幫助設計者了解如何利用電平調整寄存器控制T1和E1發送脈沖的幅度和定時,以及能夠控制的范圍。這些數據在室溫以及3.3V VDD條件下獲得。

圖3. 正常工作時的T1.

圖4. 正常工作時的120 E1.

圖5. 正常工作時的75 E1.

電子發燒友App

電子發燒友App

評論