void SPI_Init(){M_CS_out;M_SCK_out;M_SDO_out;M_SDI_in;}//向從機(jī)寫一個(gè)8位的數(shù)據(jù),同時(shí)讀出30個(gè)bit位,前兩個(gè)bit位不讀。long

2019-04-19 01:27:13

8位/16位/32-BIT系列單片機(jī)的區(qū)別是什么?有什么特點(diǎn)?

2021-09-24 07:15:36

有誰知道擾碼器和解擾碼器的VHDL編程,各位大哥們教教小弟,小弟菜鳥一個(gè),老師布置的課程設(shè)計(jì),后天就要教了!!!{:soso_e109:}{:soso_e109:}

2012-11-24 19:23:33

如果一個(gè)擾碼器現(xiàn)在做并行化,例如要求輸入位寬為32位,那么本原多項(xiàng)式如何確定?在實(shí)現(xiàn)的過程中,如果想使用并行,是不是需要將同移位寄存器長一致的周期后狀態(tài)機(jī)算出來呢?不很明白為什么可以實(shí)現(xiàn)并行化,輸出不是還是一位一位的數(shù)據(jù)的嗎?是不是將對應(yīng)的周期數(shù)計(jì)算出結(jié)果嗎?

2019-05-07 16:53:54

AD5544的18位數(shù)據(jù)由2bit地址位和16位數(shù)據(jù)位組成,采用標(biāo)準(zhǔn)SPI的時(shí)候一次傳輸8位數(shù)據(jù)該如何傳輸呢?是從17-0位放置數(shù)據(jù)還是23-6位放置數(shù)據(jù)呢。datasheet上說最后18位被保留不知道什么意思

2023-12-19 08:08:15

AD9826串行接口的通過SDATA、SCLK和SLOAD實(shí)現(xiàn)寫入四個(gè)寄存器

但是在進(jìn)行讀操作的時(shí)候,我不知道在什么bit位實(shí)現(xiàn)SDATA的輸入輸出方向切換?

每次讀寫都是16個(gè)bit,請問是在寫完高4位地址后進(jìn)行讀操作呢?還是在寫完高8位后進(jìn)行讀數(shù)據(jù)操作

2023-12-04 06:06:26

是ADI的SAR型 18位單通道全差分輸入的ADC。ADC的后端是MCU,MCU將數(shù)字信號處理之后再畫到顯示屏上顯示實(shí)時(shí)波形。

調(diào)試發(fā)現(xiàn)顯示的信號有串擾,表現(xiàn)為某一路信號懸空之后,相鄰的那一路信號

2023-12-18 08:27:39

是ADI的SAR型 18位單通道全差分輸入的ADC。ADC的后端是MCU,MCU將數(shù)字信號處理之后再畫到顯示屏上顯示實(shí)時(shí)波形。 調(diào)試發(fā)現(xiàn)顯示的信號有串擾,表現(xiàn)為某一路信號懸空之后,相鄰的那一路信號上

2018-09-06 14:32:00

BCD碼的硬件實(shí)現(xiàn),采用左移加3的算法,具體描述如下:(此處以8-bit 二進(jìn)制碼為例) 1、左移要轉(zhuǎn)換的二進(jìn)制碼1位2、左移之后,BCD碼分別置于百位、十位、個(gè)位3、如果移位后所在的BCD碼列大于或

2017-05-11 16:21:02

我想問一下CYUSB3014位寬為8bit、16bit和32bit時(shí),最大傳輸速率是不是一樣的?

2024-02-28 07:08:20

DVB通用加擾算法代理協(xié)議藍(lán)皮書

2009-05-08 09:02:30

串擾是由于線路之間的耦合引發(fā)的信號和噪聲等的傳播,也稱為“串音干擾”。特別是“串音”在模擬通訊時(shí)代是字如其意、一目了然的表達(dá)。兩根線(也包括PCB的薄膜布線)獨(dú)立的情況下,相互間應(yīng)該不會(huì)有電氣信號

2019-08-08 06:21:47

各位大神:根據(jù)FPGA bit位流文件,對其配置內(nèi)容進(jìn)行解析,以及反解,有高手請指教!感謝!

2019-05-23 15:48:48

樓主理解串口的不是很透徹,串口程序是用 小墨哥 的 串口程序修改的,現(xiàn)在要做的是把 16位的bit 用串口發(fā)送到上位機(jī),可是,我也試圖去分立 高8位,低8位,試驗(yàn)還是不通過,總是發(fā)送的不對有沒有那個(gè)

2015-09-04 21:03:03

作者:一博科技SI工程師陳德恒摘要:隨著電子設(shè)計(jì)領(lǐng)域的高速發(fā)展,產(chǎn)品越來越小,速率越來越高,信號完整性越來越成為一個(gè)硬件工程師需要考慮的問題。串擾,阻抗匹配等詞匯也成為了硬件工程師的口頭禪。電路板

2014-10-21 09:53:31

作者:一博科技SI工程師陳德恒3. 仿真實(shí)例在ADS軟件中構(gòu)建如下電路: 圖2圖2為微帶線的近端串擾仿真圖,經(jīng)過Allegro中的Transmission line Calculators軟件對其疊

2014-10-21 09:52:58

PCB設(shè)計(jì)中如何處理串擾問題 變化的信號(例如階躍信號)沿

2009-03-20 14:04:47

變化的信號(例如階躍信號)沿傳輸線由A到B傳播,傳輸線C-D上會(huì)產(chǎn)生耦合信號,變化的信號一旦結(jié)束也就是信號恢復(fù)到穩(wěn)定的直流電平時(shí),耦合信號也就不存在了,因此串擾僅發(fā)生在信號跳變的過程當(dāng)中,并且

2018-08-29 10:28:17

變化的信號(例如階躍信號)沿傳輸線由A到B傳播,傳輸線C-D上會(huì)產(chǎn)生耦合信號,變化的信號一旦結(jié)束也就是信號恢復(fù)到穩(wěn)定的直流電平時(shí),耦合信號也就不存在了,因此串擾僅發(fā)生在信號跳變的過程當(dāng)中,并且信號

2020-06-13 11:59:57

[table][tr][td] 一、 什么是位段和別名區(qū)是這樣的,記得MCS51嗎? MCS51就是有位操作,以一位(BIT)為數(shù)據(jù)對象的操作,MCS51可以簡單的將P1口的第2位獨(dú)立操作:P1.2

2018-07-09 00:22:05

[table][tr][td] 一、 什么是位段和別名區(qū)是這樣的,記得MCS51嗎? MCS51就是有位操作,以一位(BIT)為數(shù)據(jù)對象的操作,MCS51可以簡單的將P1口的第2位獨(dú)立操作:P1.2

2018-07-04 09:34:17

USB Audio方案(192KHZ采樣,24bit位寬)Mike Meng 孟凡忠 email:mike@rti.com.hkmsn:mfz118@hotmail.com; Skype:mfz118; QQ:15958574

2011-05-08 18:12:20

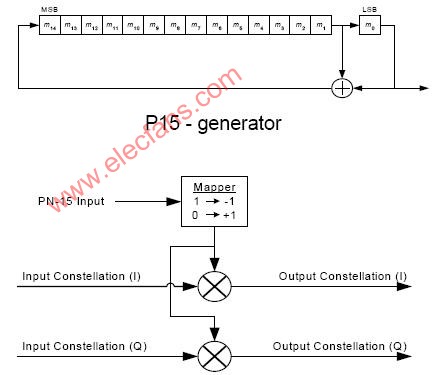

”與“1”的出現(xiàn)概率都接近50%。擾亂雖然改變了原始傳送碼流,但這種擾亂是有規(guī)律的,可以在接收端解除。將待發(fā)送的信息序列與發(fā)端產(chǎn)生的m序列進(jìn)行模二加(擾碼),擾碼序列通過傳輸信道傳送到接收端,接收端接

2019-12-18 09:37:35

塊中, SRC_CRC_EN=3 時(shí),可以在 WiMAX 標(biāo)準(zhǔn)下為編碼進(jìn)行加擾,對應(yīng)的,在上行就需要對加擾的信號進(jìn)行解擾,利用 TCP3D 可進(jìn)行解擾操作,但是,現(xiàn)在不知道 BCP 的加擾是以何種算法實(shí)施的,在 TCP3D 中該怎樣布置解擾算法呢?

希望各位老師給予幫助,十分感謝!

2018-06-21 12:21:49

串擾串擾的途徑:容性耦合和感性耦合。串擾發(fā)生在兩種不同情況:互連性為均勻傳輸線(電路板上大多數(shù)線)非均勻線(接插件和封裝)近端遠(yuǎn)端串擾各不同。返回路徑是均勻平面時(shí)是實(shí)現(xiàn)最低串擾的結(jié)構(gòu)。通常發(fā)生這種

2017-11-27 09:02:56

串擾是信號完整性中最基本的現(xiàn)象之一,在板上走線密度很高時(shí)串擾的影響尤其嚴(yán)重。我們知道,線性無緣系統(tǒng)滿足疊加定理,如果受害線上有信號的傳輸,串擾引起的噪聲會(huì)疊加在受害線上的信號,從而使其信號產(chǎn)生畸變

2019-05-31 06:03:14

繼上一篇“差模(常模)噪聲與共模噪聲”之后,本文將對“串擾”進(jìn)行介紹。串擾串擾是由于線路之間的耦合引發(fā)的信號和噪聲等的傳播,也稱為“串音干擾”。特別是“串音”在模擬通訊時(shí)代是字如其意、一目了然的表達(dá)

2018-11-29 14:29:12

串擾的基本原理

2021-03-18 06:26:37

所謂串擾,是指有害信號從一個(gè)傳輸線耦合到毗鄰傳輸線的現(xiàn)象,噪聲源(攻擊信號)所在的信號網(wǎng)絡(luò)稱為動(dòng)態(tài)線,***擾的信號網(wǎng)絡(luò)稱為靜態(tài)線。串擾產(chǎn)生的過程,從電路的角度分析,是由相鄰傳輸線之間的電場(容性)耦合和磁場(感性)耦合引起,需要注意的是串擾不僅僅存在于信號路徑,還與返回路徑密切相關(guān)。

2019-08-02 08:28:35

在選擇模數(shù)轉(zhuǎn)換器時(shí),是否應(yīng)該考慮串擾問題?ADI高級系統(tǒng)應(yīng)用工程師Rob Reeder:“當(dāng)然,這是必須考慮的”。串擾可能來自幾種途徑從印刷電路板(PCB)的一條信號鏈到另一條信號鏈,從IC中的一個(gè)

2019-02-28 13:32:18

怎么發(fā)送16位bit到 串口,串口只能發(fā)8位? 或者誰有編好的模塊,借來看看啊。。。。腦袋已經(jīng)大啦!!!

2016-07-28 10:10:21

為什么CC1101信道出現(xiàn)串擾現(xiàn)象?各位大神,我在使用CC1101的時(shí)候,遇到如下問題,我購買的是模塊,并非自己設(shè)計(jì),所有參數(shù),使用smart rf生成,參數(shù)如下:base frequency

2016-03-11 10:01:10

多了,這樣我想有個(gè)問題就是,在正常采集時(shí),這幾個(gè)通道間會(huì)不會(huì)有互相串擾的問題。謝謝。

另外我想知道互相串擾產(chǎn)生原因,如果能成放大器內(nèi)部解釋更好

2023-11-21 08:15:40

繼上一篇“差模(常模)噪聲與共模噪聲”之后,本文將對“串擾”進(jìn)行介紹。串擾串擾是由于線路之間的耦合引發(fā)的信號和噪聲等的傳播,也稱為“串音干擾”。特別是“串音”在模擬通訊時(shí)代是字如其意、一目了然的表達(dá)

2019-03-21 06:20:15

串擾的概念是什么?到底什么是串擾?

2021-03-05 07:54:17

什么是串擾?互感和互容電感和電容矩陣串擾引起的噪聲

2021-02-05 07:18:27

航空通信系統(tǒng)變得日益復(fù)雜,我們通常需要在同一架飛機(jī)上安裝多條天線,這樣可能會(huì)在天線間造成串擾,或稱同址干擾,影響飛機(jī)運(yùn)行。在本教程模型中,我們利用COMSOL Multiphysics 5.1 版本模擬了飛機(jī)機(jī)身上兩個(gè)完全相同的天線之間的干擾,其中一個(gè)負(fù)責(zé)發(fā)射,另一個(gè)負(fù)責(zé)接收,以此來分析串擾的影響。

2019-08-26 06:36:54

什么是有擾射頻?怎么消除有擾射頻?

2021-05-25 06:51:47

串擾信號產(chǎn)生的機(jī)理是什么串擾的幾個(gè)重要特性分析線間距P與兩線平行長度L對串擾大小的影響如何將串擾控制在可以容忍的范圍

2021-04-27 06:07:54

看了郭天祥的51單片機(jī)24c02的程序,其中BIT write=0;這句話是什么意思?上邊說是標(biāo)志位,但我不明白標(biāo)志位在這里是什么意思?標(biāo)志位怎么使用的?什么時(shí)候用到。

2013-02-25 10:36:18

面對串擾,包地是萬能的嗎?請看不一樣的解答

2016-12-30 16:29:07

原創(chuàng)|高速SI培訓(xùn)1.信號串擾的成因串擾(Crosstalk),顧名思義、是指不同信號互連鏈路之間的相互干擾。對于傳輸線而言,即能量從一條傳輸線耦合到另一條傳輸線上,當(dāng)不同傳輸線產(chǎn)生的電磁場發(fā)生

2016-10-10 18:00:41

如果您給某個(gè)傳輸線的一端輸入信號,該信號的一部分會(huì)出現(xiàn)在相鄰傳輸線上,即使它們之間沒有任何連接。信號通過周邊電磁場相互耦合會(huì)產(chǎn)生噪聲,這就是串擾的來源,它將引起數(shù)字系統(tǒng)的誤碼。一旦這種噪聲在相鄰

2019-07-08 08:19:27

為16位還是8位?請舉例說明如何使用Pix1Exchange 8BIT傳輸數(shù)據(jù)。在上面的場景中,我可以這樣配置用于將16位數(shù)據(jù)寫入8位寄存器:SPI1_Exchange8bit

2019-07-08 08:33:53

靜態(tài)存儲器SRAM是一款不需要刷新電路即能保存它內(nèi)部存儲數(shù)據(jù)的存儲器。在SRAM 存儲陣列的設(shè)計(jì)中,經(jīng)常會(huì)出現(xiàn)串擾問題發(fā)生。那么要如何減小如何減小SRAM讀寫操作時(shí)的串擾,以及提高SRAM的可靠性呢

2020-05-20 15:24:34

下行擾碼的生成過程是怎樣的?如何用FPGA去實(shí)現(xiàn)下行擾碼?

2021-04-30 07:24:05

在嵌入式系統(tǒng)硬件設(shè)計(jì)中,串擾是硬件工程師必須面對的問題。特別是在高速數(shù)字電路中,由于信號沿時(shí)間短、布線密度大、信號完整性差,串擾的問題也就更為突出。設(shè)計(jì)者必須了解串擾產(chǎn)生的原理,并且在設(shè)計(jì)時(shí)應(yīng)用恰當(dāng)?shù)姆椒ǎ勾?b class="flag-6" style="color: red">擾產(chǎn)生的負(fù)面影響降到最小。

2019-11-05 08:07:57

是有規(guī)律的,可以在接收端解除。將待發(fā)送的信息序列與發(fā)端產(chǎn)生的m序列進(jìn)行模二加(擾碼),擾碼序列通過傳輸信道傳送到接收端,接收端接收到擾碼序列,使用同樣的m序列進(jìn)行模二加,即可恢復(fù)原來的信息。

三

2023-09-21 10:42:02

加奇校驗(yàn)位

2017-05-19 10:23:29

求一位大神做老師,加QQ3279828860其他的詳談

2018-05-20 02:07:42

示波器通道間串擾的影響 目前幾乎所有通用品牌的主流示波器通道都不是隔離的,那么在進(jìn)行多通道測試的時(shí)候,通道與通道之間會(huì)一定程度互相干擾,因此通道隔離度指標(biāo)非常重要,隔離度越高的示波器測量就越精確

2020-03-23 18:53:35

雙絞線的性能在一直不斷的提高,但有一個(gè)參數(shù)一直伴隨著雙絞線,并且伴隨著雙絞線的發(fā)展,這個(gè)參數(shù)也越來越重要,它就是串擾 (Crosstalk)。串擾是影響數(shù)據(jù)傳輸最嚴(yán)重的因素之一。它是一個(gè)信號對另外一個(gè)

2018-01-19 11:15:04

有沒有人在學(xué)習(xí)自抗擾技術(shù)的,能請教一下嗎,剛開始學(xué)有很多不會(huì)的地!

2015-11-16 11:31:08

在PCB電路設(shè)計(jì)中有很多知識技巧,之前我們講過高速PCB如何布局,以及電路板設(shè)計(jì)最常用的軟件等問題,本文我們講一下關(guān)于怎么解決PCB設(shè)計(jì)中消除串擾的問題,快跟隨小編一起趕緊學(xué)習(xí)下。 串擾是指在一根

2020-11-02 09:19:31

的bit位寬都定義為8疑問:這是為什么呢?Int ColorSpace_getBpp(ColorSpace_Type colorSpace)[ Int bpp;switch (colorSpace

2018-07-27 08:15:46

請教AD9945 寄存器配置關(guān)于9945寄存器的配置和版本:查看相關(guān)資料說四個(gè)寄存器需要一起配置,即每次需要發(fā)送4bit(3bit地址+1bit測試位)+48bit數(shù)據(jù)(12bit*4),查看手上

2018-08-15 08:04:07

是SAR型 18位單通道全差分輸入的ADC。ADC的后端是MCU,MCU將數(shù)字信號處理之后再畫到顯示屏上顯示實(shí)時(shí)波形。 調(diào)試發(fā)現(xiàn)顯示的信號有串擾,表現(xiàn)為某一路信號懸空之后,相鄰的那一路信號上就會(huì)出現(xiàn)噪聲。將采樣的時(shí)間延長也無法消除串擾。想請教一下各路專家,造成串擾的原因和如何消除串擾,謝謝。

2019-05-14 14:17:00

[size=18.6667px]各位大俠:請問ADXL345:16位bit ,13位數(shù)據(jù)(16g)第一個(gè)為符號位 余下的是啥?誰有補(bǔ)碼數(shù)據(jù)處理c語言?

2018-08-20 07:32:25

“28-Bit Shift In”三個(gè)功能,我想使用“16-Bit Parallel Capture”功能,因?yàn)樗茉跁r(shí)鐘上升沿時(shí)捕捉電平,比較高速,但我只用到其中一位(1個(gè)管腳),其他位的管腳作為ARM的其他

2018-06-21 02:27:33

請問一下51單片機(jī)bit定義標(biāo)志位無效原因是什么?

2021-10-15 08:13:41

高頻數(shù)字信號串擾的產(chǎn)生及變化趨勢串擾導(dǎo)致的影響是什么怎么解決高速高密度電路設(shè)計(jì)中的串擾問題?

2021-04-27 06:13:27

電路上的開關(guān)檢測電路,外部DI1開路的時(shí)候,光耦不發(fā)光,DIB1輸入mcu高電平;外部DI1合閘接地GND-E的時(shí)候,光耦發(fā)光,DIB1低電平。在平常應(yīng)用沒問題,但是做抗擾度試驗(yàn)就不行了,DI1和GND-E加差模2.5kV,100KHz的阻尼振蕩干擾信號,整個(gè)設(shè)備就死機(jī)了,請問哪里改進(jìn),增加抗擾度。

2020-03-25 09:16:20

本帖最后由 逸興遄飛 于 2016-4-15 14:08 編輯

輻射抗擾:10V 有點(diǎn)不明白

2016-04-15 09:24:44

一一闡述了。如果要想做擾碼器,首先要知道自己的擾碼器最長周期是多少位的。例如在我們的工程中,由于擾碼只是其中的一個(gè)部分,他需要承接上面發(fā)送數(shù)據(jù)的格式,這樣一來,根據(jù)相關(guān)標(biāo)準(zhǔn)中指定的擾碼多項(xiàng)式選擇這樣的一

2019-07-31 16:30:47

求各位大神做靜電抗擾度試驗(yàn)的方法,以及相關(guān)的利弊。是不是都是按照國標(biāo)做的,產(chǎn)品是按照什么標(biāo)準(zhǔn)做的實(shí)驗(yàn)?

2016-04-21 13:04:47

系數(shù)設(shè)置為4.3。圖中分別在A0、B1、C1處加上了示波器探頭,可利用示波器觀看波形,B1的10MW電阻也是為了加探頭而設(shè)置的。仿真結(jié)果如圖5所示。

??

???? 從圖5中可以看出串擾的幅度比較

2018-08-28 11:58:32

高速數(shù)字設(shè)計(jì)領(lǐng)域里,信號完整性已經(jīng)成了一個(gè)關(guān)鍵的問題,給設(shè)計(jì)工程師帶來越來越嚴(yán)峻的考驗(yàn)。信號完整性問題主要為反射、串擾、延遲、振鈴和同步開關(guān)噪聲等。本文基于高速電路設(shè)計(jì)的信號完整性基本理論,通過近端

2010-05-13 09:10:07

在硬件系統(tǒng)設(shè)計(jì)中,通常我們關(guān)注的串擾主要發(fā)生在連接器、芯片封裝和間距比較近的平行走線之間。但在某些設(shè)計(jì)中,高速差分過孔之間也會(huì)產(chǎn)生較大的串擾,本文對高速差分過孔之間的產(chǎn)生串擾的情況提供了實(shí)例仿真分析

2018-09-04 14:48:28

串擾問題產(chǎn)生的機(jī)理是什么高速數(shù)字系統(tǒng)的串擾問題怎么解決?

2021-04-25 08:56:13

DVB COMMON SCRAMBLING ALGORITHMINTRODUCTIONThis document contains the forms of the distribution

2009-05-07 21:36:40 35

35 一、簡要概述: 在芯片設(shè)計(jì)過程中,一個(gè)系統(tǒng)通常是同步電路和異步電路并存,這里經(jīng)常會(huì)遇到CDC也就是跨時(shí)鐘域處理的問題,常見的處理方法,可能大家也已經(jīng)比較熟悉了,主要有單bit跨時(shí)鐘處理、多bit

2021-03-22 10:28:12 6257

6257 以 32-bit 英飛凌 TC377 為例右下圖可見,雖然是32-bit MCU,但是每個(gè)地址對應(yīng)的是一個(gè)byte【8-bit】左上圖是通過 Trace32 查看單片機(jī)memory, 可見

2021-10-25 16:36:01 11

11

電子發(fā)燒友App

電子發(fā)燒友App

評論