micrf500是用于ism(工業、科學和醫藥)和srdc(短距離設備)的專用發射和接收芯片,其頻率范圍為700mhz~1ghz,采用fsk(頻移鍵控)調制時的數據速率達128 kbauds,rf輸出功率為10dbm,靈敏度為-104dbm,接收模式電流消耗為12ma,發射模式電流消耗為50ma,低功耗模式電流消耗2μa。可廣泛應用于遙測、無線控制、無線數據中繼、無線控制系統、無線調制解調器和無線安全等系統中。

2芯片封裝與引腳功能

micrf500采用44-lqfp(blq)封裝,各引腳功能如表1所列。

3內部結構與工作原理

3內部結構與工作原理

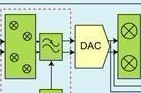

micrf500的內部結構如圖1所示。該芯片內含接收、發射和控制接口(controlinterface)三部分。其中接收部分由低噪聲放大器(lna)、混頻器、rc濾波器(rcfilters)、解調器(demod)、rssi等電路組成。發射部分由功率放大器(pa)、預置比例分頻器(prescaler)、a計數器(acounter)、n計數器(ncounter)、m計數器(mcounter)、壓控振蕩器(vco)、相位檢波器(phase detector)、充電泵(charge pump)、晶體振蕩器(xco)等電路組成。

當micrf500處在接收模式時,pll合成器產生本振振蕩(lo)信號。n、m和a計數器給出的本振振蕩頻率被分別存儲在no、mo和ao寄存器中。由于接收器是零中頻結構,因而用低功耗的集成低通濾波器作為通道濾波器。接收裝置中的低噪聲放大器(lna)用于驅動正交混頻器對。混頻器輸出饋送至兩路相同的相位積分信道。每條信道包括前置放大器、三階sallet-key rc低通濾波器和限幅器。主要信道的濾波器必須滿足電路的選擇性和動態范圍。

sallen-key rc濾波器能通過編程劃分成四個不同的截止頻率:10khz、30khz、60khz和200khz。通過外圍電阻可以調整濾波器的截止頻率。解調器可解調i和q信道的輸出并同時輸出一個數字信號。當檢測i和q信道信號的相對相位時,如果i信道落后于q信道,fsk調制頻率將位于本振振蕩頻率之上(數據“1”)。如果i信道信號超前q信道信號,fsk調制頻率則位于本振振蕩頻率之下(數據“0”)。dataixo腳為接收器輸出。rssi(接收信號強度指示器)電路可用來顯示收到信號的強度級別。兩端的串行接口可用于對電路進行編程。vco諧振電路、晶體、反饋電容和vco的fsk調制元件、回路濾波器、功放和濾波器的偏置電阻等外圍元器可用于rf輸入輸出的阻抗匹配和功率衰減。tx/rx的轉換則可通過二極管來實現。

4應用電路設計

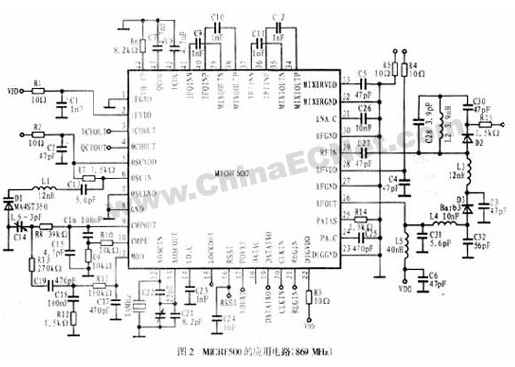

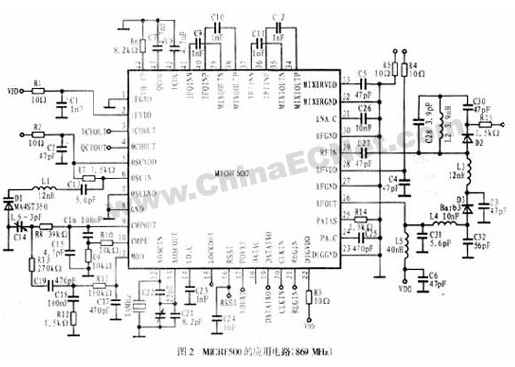

micrf500的應用電路如圖2所示,該電路的工作頻率為869mhz。電路中,收發器的調制信號加到vco,vco和外圍元件工作于869mhz。ma4st-350-1141是macon制造的一個專用變容二極管,而bar63則是西門子公司生產的二極管。

由于vco是一個基本的colpitts振蕩器,因而應有一個外部諧振器和一個可變電感,諧振器可由電感l1和線性電容c13組成。

由于vco是一個基本的colpitts振蕩器,因而應有一個外部諧振器和一個可變電感,諧振器可由電感l1和線性電容c13組成。

晶體振蕩器的晶振是rf輸出頻率的基準,因而要求具有很好的相位和頻率穩定性。晶體振蕩器通過調節可變電容c20可改變諧振頻率。要獲得小的頻偏,晶體要預老化且要有小的溫度系數。本設計采用10mhz晶振。

相位檢測輸出被轉換成電壓并經14腳(ldc)外電容c23的濾波后,產生的直流電壓與位ref0-ref5設置的基準窗口相比較。ref0~ref5為1時,基準窗口在0v;ref0~ref5為0時,其基準窗口的直流電壓最大。另外,基準窗口能在兩者之間線性步進地上升或下降。窗口的大小可等效為2個(ref6=1)基準臺階或4個(ref6=0)基準臺階。

實現fsk有三種方法:第一種是使用vco實現fsk調制,其對應的發射頻率將被編程在分頻器a1、n1和m1中。在tx模式,dataixo端保持在三態,直到開始發射數據;第二種是通過開關在a、n和m分頻器兩組之間實現,a、n和m值對應到接收頻率和兩發射頻率。發射數據“0”時,將對分頻器a0、n0和m0進行編程;發射數據“1”時,將對分頻器a1、n1和m1進行編程;第三種則可通過加/減1到分配器a1來實現,其頻偏與比較頻率相等,發射頻率的校準可通過對a1、n1和m1進行編程來實現。所有類型的fsk調制數據都從引腳端dataixo輸入。

回路濾波的設計對優化參數是很重要的,如調制速率、pll鎖定時間、帶寬和相位噪聲等。低位率通常可調制在pll內,而將回路鎖定在不同的頻率上則可通過開關分頻器(m、n和a)來實現。高調制率(超過2400bps)一般靠pll外調制來實現,設計時通常直接加到vco。此時,回路濾波器的值可通過軟件進行編程確定。

發射功率放大器是基本的ab類,最后一級是開集電極(oc)電路,因此應外接一負載電感(l2)。放大器的直流電流通過外接偏置電阻r14來調整。當偏置電阻值為1.5kω時,偏置電流為50μa。最后一級電路的偏置電流大約為15ma。

阻抗匹配與天線的類型也有很大關系,設計時可采用最大輸出功率,并在功率放大器上接一約100ω的阻抗。輸出功率可編程為8級,每級大約相差3db,可以通過控制字pa2-pa0來進行控制。

為了預防干擾信號干擾功放,功放應當緩慢的導通和截止。通過連接到24腳的電容c25可使偏置電流在限定范圍內上升或下降。上升/下降電流典型值為1.1μa,當電源為3v時,開關速率為2.6μs/pf。由于轉換功放開關會影響pll,所以開關速率必須與pll帶寬相對應。

緩沖放大器通常連接到vco和功率放大器之間。功率放大器的輸入信號可以放大到期望的輸出功率。通過設置位gc為“0”可以旁路緩沖級。

rf接收器的低干擾放大器可利用提升輸入信號來優化頻率轉變過程。其主要目的是為了預防混頻器干擾。lan是一個兩級放大器,正常時,在900mhz處可以獲得23db的增益,lan具有一個直流外饋環,可為lan提供偏置。外接電容c26對所有的直流反饋環路均可起到退耦和穩定作用。

通過設置bylan位為“1”可以旁路lan,這對強信號是非常有用的。

混頻器在900mhz有12db增益,在34、35和38、39腳中,每一路混頻器的輸出阻抗約為15kω。

解調器解調出來的信號的頻偏必須永遠比頻漂大,且至少等于波特率加上頻漂。

限幅器是一個零點檢波器,其輸出為與i-q相位差相對應的值,波形是邊緣陡峭的方波。

解調器的作用是解調i和q信道輸出并產生數字量輸出,同時可用來檢測i和q信道信號之間的相位差。對于i信道,在限幅器輸出的每一個邊沿(上升沿和下降沿),q信道限幅器輸出的振幅均被采樣,反之也如此。解調器的輸出通過dataixo引腳來實現。數據輸出被if信號每周期更新四次。如果i信道信號滯后于q信道,fsk調制頻率將位于lo頻率上方(數據“1”),而如果i信道超前q信道,則fsk調制頻率將位于lo頻率下方(數據“0”)。

解調器的輸入和輸出通過一階rc低通濾波器濾波并經過斯密特觸發器放大來產生方波。在低位率時,增加引腳18的電容(datac)可以減少rx數據信號濾波器的帶寬。濾波器的帶寬必須根據位率來進行調整,這個功能一般通過rxfilt位來控制。

rssi(接收信號強度指示)電路的輸出與代表rf輸入信號強弱的直流電壓相對應。當接收到的rf輸入信號使rssi輸出增加時,rssi將作為信號的有無指示器而用于喚醒電路。無信號時,電路將處于睡眠模式以長電池壽命。

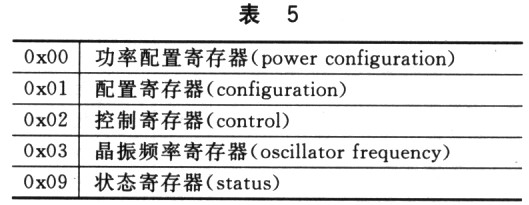

在編程時,可用兩線(clkin和regin)式總線來編程電路,兩線串行總線接口可以控制分頻器、選擇tx的功率和rx以及合成器電路功能塊,其接口由一個80位編程寄存器組成。數據和第一有效位從regin線進入,第一位輸入為p1,最后一位輸入為p80。程序寄存器中的位安排如表2所列。

當clkin信號為高電平時,80位控制字首先讀入移位寄存器,然后通過regin信號(正的或負的)裝入并行寄存器。其接收和發射模式可由電路直接指定。圖3所示是micrf500中clkin、regin、內部load、int和pa-c信號的時序圖。

當clkin信號為高電平時,80位控制字首先讀入移位寄存器,然后通過regin信號(正的或負的)裝入并行寄存器。其接收和發射模式可由電路直接指定。圖3所示是micrf500中clkin、regin、內部load、int和pa-c信號的時序圖。

圖3中,在時序1時,倒數第二位數據被時鐘信號裝入移位寄存器(‘1’);在時序2時,最后一位數據被時鐘信號裝入移位寄存器(‘1’);時序3時,通過regin信號的轉換可產生一內部裝入脈沖,并將控制字裝入并行寄存器,從而使電路進入新的模式(tx模式),并穩定在這種新模式。在時序4時,如果時鐘信號變低,功放將慢慢開啟以使rf輸出信號最小。在pa開啟前,pll處于可靠的鎖定狀態。而在lockdet被設置后,pa開啟。時序5時,功率放大器將滿負荷開啟。時序6時,一個新的控制字進入移位寄存器。當clkin為高時,regin信號發生跳變以關閉功率放大器。時序7時,功放關閉以產生內部裝入脈沖,并將新控制字裝入并行寄存器,從而使電路進入一個新的模式(節電模式),但clkin必須在產生內部裝入脈沖后變低。當clkin為高時,regin上將不會出現跳變,此時,新的控制字在任何時間內,都不影響收發器操作,它將按照自己的方式按時進 入移位寄存器。

2芯片封裝與引腳功能

micrf500采用44-lqfp(blq)封裝,各引腳功能如表1所列。

3內部結構與工作原理

3內部結構與工作原理micrf500的內部結構如圖1所示。該芯片內含接收、發射和控制接口(controlinterface)三部分。其中接收部分由低噪聲放大器(lna)、混頻器、rc濾波器(rcfilters)、解調器(demod)、rssi等電路組成。發射部分由功率放大器(pa)、預置比例分頻器(prescaler)、a計數器(acounter)、n計數器(ncounter)、m計數器(mcounter)、壓控振蕩器(vco)、相位檢波器(phase detector)、充電泵(charge pump)、晶體振蕩器(xco)等電路組成。

當micrf500處在接收模式時,pll合成器產生本振振蕩(lo)信號。n、m和a計數器給出的本振振蕩頻率被分別存儲在no、mo和ao寄存器中。由于接收器是零中頻結構,因而用低功耗的集成低通濾波器作為通道濾波器。接收裝置中的低噪聲放大器(lna)用于驅動正交混頻器對。混頻器輸出饋送至兩路相同的相位積分信道。每條信道包括前置放大器、三階sallet-key rc低通濾波器和限幅器。主要信道的濾波器必須滿足電路的選擇性和動態范圍。

sallen-key rc濾波器能通過編程劃分成四個不同的截止頻率:10khz、30khz、60khz和200khz。通過外圍電阻可以調整濾波器的截止頻率。解調器可解調i和q信道的輸出并同時輸出一個數字信號。當檢測i和q信道信號的相對相位時,如果i信道落后于q信道,fsk調制頻率將位于本振振蕩頻率之上(數據“1”)。如果i信道信號超前q信道信號,fsk調制頻率則位于本振振蕩頻率之下(數據“0”)。dataixo腳為接收器輸出。rssi(接收信號強度指示器)電路可用來顯示收到信號的強度級別。兩端的串行接口可用于對電路進行編程。vco諧振電路、晶體、反饋電容和vco的fsk調制元件、回路濾波器、功放和濾波器的偏置電阻等外圍元器可用于rf輸入輸出的阻抗匹配和功率衰減。tx/rx的轉換則可通過二極管來實現。

4應用電路設計

micrf500的應用電路如圖2所示,該電路的工作頻率為869mhz。電路中,收發器的調制信號加到vco,vco和外圍元件工作于869mhz。ma4st-350-1141是macon制造的一個專用變容二極管,而bar63則是西門子公司生產的二極管。

由于vco是一個基本的colpitts振蕩器,因而應有一個外部諧振器和一個可變電感,諧振器可由電感l1和線性電容c13組成。

由于vco是一個基本的colpitts振蕩器,因而應有一個外部諧振器和一個可變電感,諧振器可由電感l1和線性電容c13組成。晶體振蕩器的晶振是rf輸出頻率的基準,因而要求具有很好的相位和頻率穩定性。晶體振蕩器通過調節可變電容c20可改變諧振頻率。要獲得小的頻偏,晶體要預老化且要有小的溫度系數。本設計采用10mhz晶振。

相位檢測輸出被轉換成電壓并經14腳(ldc)外電容c23的濾波后,產生的直流電壓與位ref0-ref5設置的基準窗口相比較。ref0~ref5為1時,基準窗口在0v;ref0~ref5為0時,其基準窗口的直流電壓最大。另外,基準窗口能在兩者之間線性步進地上升或下降。窗口的大小可等效為2個(ref6=1)基準臺階或4個(ref6=0)基準臺階。

實現fsk有三種方法:第一種是使用vco實現fsk調制,其對應的發射頻率將被編程在分頻器a1、n1和m1中。在tx模式,dataixo端保持在三態,直到開始發射數據;第二種是通過開關在a、n和m分頻器兩組之間實現,a、n和m值對應到接收頻率和兩發射頻率。發射數據“0”時,將對分頻器a0、n0和m0進行編程;發射數據“1”時,將對分頻器a1、n1和m1進行編程;第三種則可通過加/減1到分配器a1來實現,其頻偏與比較頻率相等,發射頻率的校準可通過對a1、n1和m1進行編程來實現。所有類型的fsk調制數據都從引腳端dataixo輸入。

回路濾波的設計對優化參數是很重要的,如調制速率、pll鎖定時間、帶寬和相位噪聲等。低位率通常可調制在pll內,而將回路鎖定在不同的頻率上則可通過開關分頻器(m、n和a)來實現。高調制率(超過2400bps)一般靠pll外調制來實現,設計時通常直接加到vco。此時,回路濾波器的值可通過軟件進行編程確定。

發射功率放大器是基本的ab類,最后一級是開集電極(oc)電路,因此應外接一負載電感(l2)。放大器的直流電流通過外接偏置電阻r14來調整。當偏置電阻值為1.5kω時,偏置電流為50μa。最后一級電路的偏置電流大約為15ma。

阻抗匹配與天線的類型也有很大關系,設計時可采用最大輸出功率,并在功率放大器上接一約100ω的阻抗。輸出功率可編程為8級,每級大約相差3db,可以通過控制字pa2-pa0來進行控制。

為了預防干擾信號干擾功放,功放應當緩慢的導通和截止。通過連接到24腳的電容c25可使偏置電流在限定范圍內上升或下降。上升/下降電流典型值為1.1μa,當電源為3v時,開關速率為2.6μs/pf。由于轉換功放開關會影響pll,所以開關速率必須與pll帶寬相對應。

緩沖放大器通常連接到vco和功率放大器之間。功率放大器的輸入信號可以放大到期望的輸出功率。通過設置位gc為“0”可以旁路緩沖級。

rf接收器的低干擾放大器可利用提升輸入信號來優化頻率轉變過程。其主要目的是為了預防混頻器干擾。lan是一個兩級放大器,正常時,在900mhz處可以獲得23db的增益,lan具有一個直流外饋環,可為lan提供偏置。外接電容c26對所有的直流反饋環路均可起到退耦和穩定作用。

通過設置bylan位為“1”可以旁路lan,這對強信號是非常有用的。

混頻器在900mhz有12db增益,在34、35和38、39腳中,每一路混頻器的輸出阻抗約為15kω。

解調器解調出來的信號的頻偏必須永遠比頻漂大,且至少等于波特率加上頻漂。

限幅器是一個零點檢波器,其輸出為與i-q相位差相對應的值,波形是邊緣陡峭的方波。

解調器的作用是解調i和q信道輸出并產生數字量輸出,同時可用來檢測i和q信道信號之間的相位差。對于i信道,在限幅器輸出的每一個邊沿(上升沿和下降沿),q信道限幅器輸出的振幅均被采樣,反之也如此。解調器的輸出通過dataixo引腳來實現。數據輸出被if信號每周期更新四次。如果i信道信號滯后于q信道,fsk調制頻率將位于lo頻率上方(數據“1”),而如果i信道超前q信道,則fsk調制頻率將位于lo頻率下方(數據“0”)。

解調器的輸入和輸出通過一階rc低通濾波器濾波并經過斯密特觸發器放大來產生方波。在低位率時,增加引腳18的電容(datac)可以減少rx數據信號濾波器的帶寬。濾波器的帶寬必須根據位率來進行調整,這個功能一般通過rxfilt位來控制。

rssi(接收信號強度指示)電路的輸出與代表rf輸入信號強弱的直流電壓相對應。當接收到的rf輸入信號使rssi輸出增加時,rssi將作為信號的有無指示器而用于喚醒電路。無信號時,電路將處于睡眠模式以長電池壽命。

在編程時,可用兩線(clkin和regin)式總線來編程電路,兩線串行總線接口可以控制分頻器、選擇tx的功率和rx以及合成器電路功能塊,其接口由一個80位編程寄存器組成。數據和第一有效位從regin線進入,第一位輸入為p1,最后一位輸入為p80。程序寄存器中的位安排如表2所列。

當clkin信號為高電平時,80位控制字首先讀入移位寄存器,然后通過regin信號(正的或負的)裝入并行寄存器。其接收和發射模式可由電路直接指定。圖3所示是micrf500中clkin、regin、內部load、int和pa-c信號的時序圖。

當clkin信號為高電平時,80位控制字首先讀入移位寄存器,然后通過regin信號(正的或負的)裝入并行寄存器。其接收和發射模式可由電路直接指定。圖3所示是micrf500中clkin、regin、內部load、int和pa-c信號的時序圖。圖3中,在時序1時,倒數第二位數據被時鐘信號裝入移位寄存器(‘1’);在時序2時,最后一位數據被時鐘信號裝入移位寄存器(‘1’);時序3時,通過regin信號的轉換可產生一內部裝入脈沖,并將控制字裝入并行寄存器,從而使電路進入新的模式(tx模式),并穩定在這種新模式。在時序4時,如果時鐘信號變低,功放將慢慢開啟以使rf輸出信號最小。在pa開啟前,pll處于可靠的鎖定狀態。而在lockdet被設置后,pa開啟。時序5時,功率放大器將滿負荷開啟。時序6時,一個新的控制字進入移位寄存器。當clkin為高時,regin信號發生跳變以關閉功率放大器。時序7時,功放關閉以產生內部裝入脈沖,并將新控制字裝入并行寄存器,從而使電路進入一個新的模式(節電模式),但clkin必須在產生內部裝入脈沖后變低。當clkin為高時,regin上將不會出現跳變,此時,新的控制字在任何時間內,都不影響收發器操作,它將按照自己的方式按時進 入移位寄存器。

電子發燒友App

電子發燒友App

評論