近年來,有關將CMOS工藝在射頻(RF)技術中應用的可能性的研究大量增多。深亞微米技術允許CMOS電路的工作頻率超過1GHz,這無疑推動了集成CMOS射頻電路的發展。目前,幾個研究組已利用標準的CMOS工藝開發出高性能的下變頻器、低相位噪聲壓控振蕩器(VCO)和雙模數預分頻器(prescaler)。這些研究表明,在無須增加額外器件或進行調整的條件下,可以設計出完全集成的接收器和VCO電路。低噪聲放大器、上行轉換器、合成器和功率放大器的深入研究,將可能設計出電信應用的完全集成收發器CMOS 射頻電路。

無線通信及其應用技術的迅猛發展,很大程度上得益于無線通信中的數字編碼和數字信號處理技術的引入。數字技術發展是高性能低成本CMOS技術發展的結果,因為CMOS技術使得在單塊裸片上集成大量的數字功能成為可能。這樣,利用先進的調制技術、復雜的解調算法,以及高質量的錯誤檢測和糾錯系統,其結果是產生了高性能無損耗的數字通信信道。

目前,數字技術發展以及無線市場的高速增長已經極大地改變了模擬收發器前端設備。前端設備是天線與無線收發器的數字調制解調器之間的接口,前端設備必須檢測頻率高達1GHz至2GHz微伏級的微弱信號。同時,還必須以相同的高頻率發射功率在2W左右的信號。因此,這需要能在天線和A/D轉換以及數字信號處理之間轉換頻帶的高性能模擬電路,如濾波器、放大器和混頻器。低成本和低功耗要求使得模擬前端設備成為未來射頻設計的瓶頸,集成度的進一步提高將顯著降低裸片大小、成本和功耗。在過去幾年中,已經提出了許多進一步增強接收器、發送器和合成器集成度的不同技術。

在進一步提升集成度的同時,研究人員也力圖采用CMOS工藝集成射頻電路。雖然CMOS技術主要應用于數字電路的集成,但如果能在高性能模擬電路中應用CMOS技術,將使性能得到很大提高,其優勢將更為明顯:可在單塊芯片上集成完整的收發器系統,即同一裸片上既集成模擬前端器件,又集成數字解調器。這種需求只能利用CMOS或BiCMOS工藝實現,BiCMOS工藝能提高模擬設計的性能,但成本也相應提高,這不僅因為單位面積的成本增加,而且需要為數字電路部分預留更大的芯片空間。隨著在CMOS工藝上的投資遠遠超出雙極性器件,普通CMOS工藝將逐步消除BiCMOS器件與采用深亞微米 CMOS工藝的NMOS器件,甚至消除采用相同BiCMOS工藝的NMOS器件之間的性能差異。NMOS器件的ft參數將逐漸接近NPN器件的ft。

盡管多年前就展開了一些有關采用CMOS工藝的射頻設計研究,但直到最近幾年人們才真正關注實現該技術的可能性。目前,業界有幾個研究組正從事該主題的研究。由于雙極性器件固有的特性優于CMOS器件,因此一些研究人員認為射頻CMOS只適用于具有較低性能標準,如ISM等低性能系統,或者可以通過改進CMOS工藝,如蝕刻電感器下面的基底來提高其性能。射頻CMOS技術將可能采用普通的深亞微米工藝對高性能應用,如GSM、DECT和 DCS1800中的收發器進行完全集成。

CMOS技術

出于對技術標準的不斷提高以及實現更高集成度DSP電路的考慮,亞微米技術目前已被視為標準的CMOS技術。該技術的發展趨勢甚至向深亞微米技術發展,如規格為0.1微米或更小的晶體管。而Ft接近100GHz的晶體管最近也出現在0.1微米的深亞微米工藝中。

然而,晶體管中的寄生電容,包括柵極-漏極交迭電容(gate-drain overlap capacitance)和漏極-體結電容(drain-bulk junction capacitance)延緩了深亞微米技術的發展。圖1比較了不同技術的ft和fmax值,這清晰地說明了上述結論。與ft相比,fmax更為重要,因為fmax反映了實際配置中晶體管的速率極限。如圖中所示,雖然ft快速增加,但對于實際的電路設計(fmax),速度的提高卻并不大。

最后,在最近的集成CMOS射頻電路中很清晰地看到,不僅CMOS技術本身成為了制約因素,封裝也同樣如此。由于射頻信號最終將來源于芯片,而且由于射頻天線信號必須進入芯片,因此任何與ESD保護網絡相連的PCB、封裝引腳寄生電容將極大地影響,或使射頻信號惡化。

接收器拓撲結構

超外差(heterodyne)或中頻接收器是最常用的接收器拓撲結構。在中頻接收器中,期望信號將下變頻到相對較高的中頻頻率。采用高質量的無源帶通濾波器可防止鏡像信號在中頻頻率上與期望信號發生交迭。通過利用中頻接收器拓撲結構,尤其是當采用多個中頻級時可以實現極高的接收器性能。

由于每一級濾波都需要在芯片外實現,并采用分立的帶通濾波器,因此中頻接收器設計的主要問題是不能滿足更高的集成度要求。這些分立的濾波器和帶有大量引腳的接收器芯片提高了成本,而且功耗也很大(通常分立濾波器需要50Ω的驅動信號源驅動)。此外,在CMOS射頻電路設計中,在1GHz的頻率范圍上輸入/輸出的問題也很嚴重。

作為中頻接收器的替代方案,零差(homodyne)或零中頻接收器可以實現極高的集成度。零中頻接收器對通往基帶的信號進行了直接、正交的下變頻轉換。期望信號將自身作為鏡像信號,因此可以實現充分的鏡像信號抑制,盡管信號抑制的正交精度有限。在理論上,零中頻接收器中根本不需要分立的高頻帶通濾波器,可以實現完全集成的接收器,尤其是當下變頻在單級中執行時。例如,直接從900MHz變換到基帶信號。

與中頻接收器相比,零中頻接收器的缺點在于其較低的性能。零中頻接收器對寄生基帶信號非常敏感,如DC偏移電壓以及由射頻和LO自混頻產生的串擾分量。這些缺點限制了零中頻接收器在無線應用系統中的廣泛使用,因此零中頻接收器常用在低性能要求的應用中,如尋呼機和ISM中。在這些應用中,可以對編碼進行擾碼處理,因此可以插入高通濾波器,從而避免DC偏移問題。零中頻接收器的另一個應用是用作中頻-零中頻混合接收器拓撲結構的第二級。通過采用由DSP實現的動態非線性DC糾錯算法,零中頻拓撲結構還可應用于高性能應用系統,如GSM和數字增強型無繩電話(DECT)中。

近年來,高性能要求的應用中也引入了新的接收器拓撲結構,如準中頻(quasi-IF)或寬帶中頻接收器,以及低中頻接收器。寬帶中頻接收器首先對中頻頻率進行正交下變頻,接著再對基帶進行正交下變頻。信道選擇則由中頻頻率處的第二級本地振蕩器實現,這樣有利于第一級本地振蕩器保持固定的頻率。然而,必須注意第一級正交下變頻器的精度,因為任何相位誤差都將導致鏡像信號的抑制能力下降,這時就必須利用高頻濾波器提高鏡像信號抑制。此外,還需要較高的中頻頻率,以使中頻頻率與整個頻帶的比例足夠高。否則,第二級VCO的可調節能力就必須非常大。另一方面,混頻器第一級也不可能是真正的下變頻混頻器,因為下變頻混頻器仍然需要寬帶輸出帶寬,而這正是產生系統噪聲的一個缺點。另外,多級拓撲結構本身將產生更大的功耗。

顧名思義,低中頻接收器將天線頻率直接下變頻為較低的中頻,即在若干100kHz的頻率范圍內。下變頻采用正交方式,而鏡像信號抑制通常在下變頻之后,在DSP中以較低的頻率完成。因此,低中頻與零中頻接收器緊密相關,低中頻可完全集成并采用單級直接下變頻,不需要高頻鏡像信號抑制濾波器。低中頻和零中頻兩者的主要差別在于:低中頻不用基帶處理,因此完全不受寄生基帶信號的影響,這樣就克服了零中頻接收器的主要缺點;零中頻的缺點在于鏡像信號完全不同于低中頻接收器拓撲結構中的期望信號,但通過慎重選擇中頻頻率,就足以利用帶有低信號電平的鄰近信道進行鏡像信號抑制,可以達到3°的相位精度。

完全集成的CMOS下變頻器

倍頻器中最常用的一種拓撲結構就是帶有交叉聯結可變跨導差動級的倍頻器。在CMOS工藝中,采用該拓撲結構及其相關結構,例如基于平方律的拓撲,只適用于高頻系統。為避免產生畸變問題,拓撲結構必須具有較大的VGS-VT值或較大的源極衰減阻抗,但這將產生更大的功耗并引發噪聲問題。可以通過在線性區域中,將帶MOS晶體管的偽差分拓撲結構取代底端差分對結構來避免這一問題。CMOS下變頻處理中經常用到對開關電容放大器進行二次采樣的技術。在這里,MOS晶體管用作帶有高輸入帶寬的開關,期望信號就通過這些開關進行通信。通過采用二次采樣可以用較低頻率的運算放大器實現這些結構。與中頻頻率相比,開關和開關電容電路的工作頻率要低很多。此外,時鐘抖動必須非常低,這樣高頻信號才能以足夠高的精度進行采樣。二次采樣的缺點是,在采樣頻率處倍頻器上的所有信號和噪聲將與期望信號發生交迭。因此,有必要將高質量的高頻濾波器與開關電容二次采樣拓撲結構結合使用。

圖2顯示了以0.7微米CMOS工藝實現的完全集成正交下變頻器的方框圖。該變頻器采用新開發的雙正交結構,可以得到極高的正交精度,在很大的通頻帶中具有小于0.3°的相位精度,并不需要任何外部器件,也不需要對器件進行調整。應用于下變頻器的拓撲結構建立在線性區域的NMOS晶體管基礎之上。由于下變頻器與虛地上的電容相結合,因而只需要低頻率的運算放大器。在線性區域中采用MOS晶體管,能使RF和LO輸入的線性度得到很大的提高,混頻器的輸入IP3將超過+45dBm。RF和LO輸入的高線性度將有助于混頻器處理非常高的IMFDR3電平,這樣就不再需要任何高頻濾波器。

合成器

本地振蕩器負責在上變頻和下變頻器中進行正確的頻率選擇。由于目前的無線通信系統必須盡可能高效地利用頻譜,因此信道總是排列得非常緊密。接收信道的期望信號電平可能非常小,而相鄰的信道則可能具有非常大的信號電平,因此LO信號的相位噪聲指標將非常高,因而頻率合成器的設計非常關鍵。

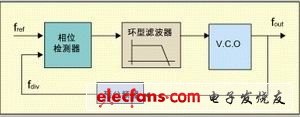

同時,移動通信還要求器件的功耗低、成本低和重量輕。完全集成的合成器將能滿足這些要求,而完全集成意味著采用標準的CMOS技術,并無需增加任何外部器件或工藝流程。通常,LO通過如圖3所示的鎖相環實現。其中壓控振蕩器和雙模數預分頻器(DMP)的設計必須滿足嚴格的指標。

在以亞微米CMOS技術實現GHz VCO過程中,可有兩種選擇方案:環形振蕩器或基于LC振蕩回路諧振頻率的振蕩器。在該LC振蕩回路中的電感器可以用有源電感或無源電感方式實現。研究表明,環形振蕩器和有源LC振蕩器的相位噪聲與功耗成反比:

因此,對于低功率、低相位噪聲的VCO,唯一的可行解決方案就是帶無源電感的LC振蕩器。在此條件下,相位噪聲將與功耗成正比:

該振蕩器唯一的缺點就是集成的無源電感。等式(2)表明,對于較低的相位噪聲,即LC環路的等效串聯阻抗R必須盡可能小。較低的阻抗也意味著較低的電路損耗,只需較低的功率即可補償這些損耗。在大多數技術中,電容可以輕易獲得,但由于阻抗R通常由電感的串聯阻抗決定,因此電感的設計就尤為重要。電感的設計目前存在3種解決方案。

硅基底上的螺旋電感通常要承擔由于基底而產生的大量損耗,這限制了可獲取的Q值大小。最近,新開發的技術在后處理過程中能將螺旋線圈之下的基底蝕刻掉。但是,由于在IC的正常工藝之后需要引入額外的蝕刻過程,該技術并不適用于大規模生產。

為滿足極低的相位噪聲要求,需要對邦定線電感進行深入研究。由于邦定線的寄生感應系數約為1nH/mm,且串聯阻抗極低,因此可以得到Q值很高的電感。IC技術總離不開邦定線,因此邦定線完全可被視為標準的CMOS技術的一部分。由4條接合線形成兩個電感可與增強的LC振蕩回路一起,實現噪聲和功率的有效折衷。對于1.8GHz的載波,當頻率偏移量為200kHz時,測量的相位噪聲可低至-115dBc/Hz。在電源電壓為3V時,功耗僅為 24mW。但是,由于這種實現方案的性能并不能滿足批量生產要求,因此業界很少采用這種解決方案。

最佳的解決方案是不做任何調整,直接在標準硅基底上采用螺旋線圈。當采用雙極工藝實現時,將不會產生基底損耗,因為這種實現方法中,基底通常具有很高的阻值。大多數亞微米CMOS技術均采用高度摻雜的基底,因而基底具有很大的感應電流,這是導致高損耗的根源。通過有限元仿真研究這些低阻值基底的作用效果,這種分析在螺旋電感LC振蕩器應用中,有助于得到優化的線圈設計。這種方案只有兩層金屬層可用,基底采用了高度摻雜工藝,產生的功耗僅為 6mW,對于1.8GHz的載波,當頻率偏移量為600kHz時,可獲得-116dBc/Hz的相位噪聲。

為設計高速雙模數預分頻器,目前業界已經開發出了可基于M/S觸發器主輸出和從輸出之間90°的相位關系的新架構。該架構如圖5所示。采用該架構,在24mW功耗和一個3V電源條件下,可以得到1.75GHz的輸入頻率,甚至還可以利用5V的電源得到2.5GHz的輸入頻率。

完全集成的VCO和雙模數預分頻器無需調整或后處理,即可在標準的CMOS工藝上集成完整的LO合成器,并符合現代通信規范。

RF CMOS上變頻器

到目前為止,公開發表的文章中提及的大多是CMOS下變頻混頻器。直到最近,業界才提出了CMOS上變頻器。在傳統的雙極收發器實現中,上變頻和下變頻混頻器通常采用相同的四象限拓撲結構。但上變頻和下變頻器之間也存在一些本質的區別,通過研究這些區別可以優化專用混頻器拓撲結構。

在下變頻器拓撲結構中,兩條輸入信號都是高頻信號,如GSM系統中的900MHz信號。而對于低中頻或零中頻接收器系統,輸出信號則是最大為若干兆赫茲的低頻信號。

上行變頻混頻器的設計則完全不同,高頻本地振蕩器和低頻基帶(BB)輸入信號經過相乘,形成高頻輸出信號。所有這些進一步的信號處理必須在高頻下進行,但當采用當前的深亞微米CMOS工藝時將相當困難,并將消耗很大的功率。此外,所有噪聲信號,如交調分量和LO泄漏信號都必須低于期望信號電平,例如低于-30 dB的信號電平。

很多已公開CMOS的混頻器拓撲結構均基于傳統的具有交叉聯結差動調節級的可變跨導倍頻器。由于傳統的雙極??叉聯結差動調節級又基于雙極性晶體管的線性跨導(translinear)特性構建,因此與之相對應的MOS器件只能在調制器或開關模式下有效地使用。較大的LO信號必須用來獲得門限,這將導致極大的LO饋通(feedthrough)。在CMOS下變頻器中,這已經成為一個難題。例如,對于-30dBm的饋通信號,LO輸出信號的電平為-23dBm,這表明抑制的信號電平僅為-7dB。這將導致直接上變頻拓撲結構出現非常嚴重的問題,而且通過對LO信號進行方波調制,第三階諧波將具有30%的信號功率。噪聲信號將只能通過附加的外部輸出濾波器進行濾波。

上述問題可以通過在CMOS中對偏離線性區域的MOS混合晶體管中的電流進行線性調制加以解決。對于柵極電壓V1+vin1、漏電壓V2+vin2/2以及源電壓V2-vin2/2,通過晶體管的電流可由下式計算:

![]()

當LO信號連接到柵極,基帶信號連接到vin2時,由于等式(3)的第一項,電流將包含LO附近的頻率分量;根據等式3第二項可知,電流還包含基帶信號分量。根據上面的原理,可以得到采用標準CMOS技術的 1GHz上變頻器。

所有不期望的測量信號均低于-30dBc。如果采用500Ω的片上負載,那么對于0dBm的LO信號就可實現-10dB轉換增益。然而,傳統的RF構件內聯采用了50Ω的特性阻抗,這意味著CMOS發送器功能需要額外的功率預放大器,以得到外部高效率功率放大器組件的輸入阻抗。對于現有的亞微米技術而言,預放大器構件仍是一個嚴重問題。用以實現900MHz完全集成收發器的典型雙極性技術具有20GHz的截止頻率。由于目前在高頻應用中采用的亞微米技術具有較低的gm/I比率,因此CMOS預放大器的功耗將比雙極性技術高至少20倍。然而,得益于CMOS技術的快速下行縮放,現有的CMOS 構件實現表明,帶有可接受功耗的整體CMOS收發器完全適用于極深亞微米CMOS。

本文結論

幾個深亞微米技術研究組正致力于研究在RF電路實現CMOS技術的可能性。尤其是在新的接收器拓撲結構(如寬帶中頻和低中頻拓撲結構)開發中,該技術與高線性下變頻器相結合,無需添加外部濾波器或其它器件,就能為完全集成的下變頻器開發鋪平道路。

然而,由于現有亞微米技術的適中速度性能,必須設計出低噪聲低功耗的電路。只要短信道效應不限制線性度和互調性能,深亞微米技術的發展將有助于實現這些目標。

性能低相位噪聲、低功耗、完全集成的VCO電路已出現在CMOS中。雖然開始時遇到一些困難,但后處理技術通過將電感用作接合線,推動了標準CMOS技術的應用。現在,甚至已經出現了帶有優化的集成螺旋電感的低相位噪聲性能標準CMOS技術,而且無需任何后處理或對外部器件進行調整。這推動了完全集成的收發器電路的發展。

然而,由于通信系統通常是雙向系統,因而也需要發送器電路。直到最近,具有適中輸出功率的CMOS上行轉換器才出現在公開發表的文章中。同樣得益于深亞微米技術的發展,今后將有望實現具有可接受功耗的完全集成CMOS發送器電路。這推動了采用標準CMOS技術的完全集成收發器電路的發展。

電子發燒友App

電子發燒友App

評論