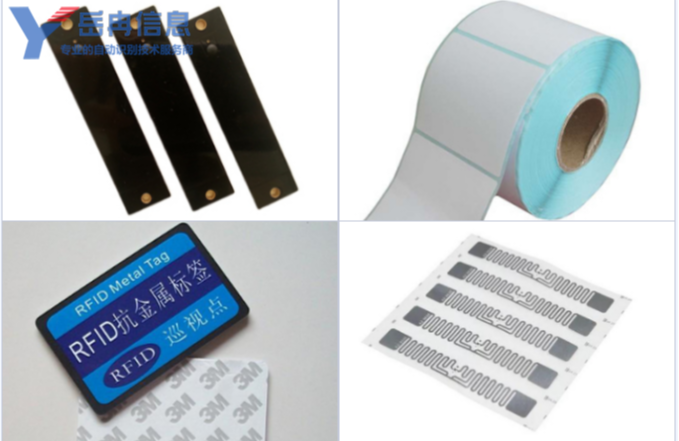

無線射頻識別(RFID)是一種利用射頻信號自動識別目標對象并獲取相關信息的技術。基本的RFID系統由電子標簽、閱讀器及應用支撐軟件等幾部分組成。

電子標簽內存有一定格式的電子數據,常以此作為待識別物品的標識性信息。應用中將電子標簽附著在待識別物品上,作為待識別物品的電子標記。閱讀器與電子標簽可按約定的通信協議互傳信息,通常的情況是由閱讀器向電子標簽發送命令,電子標簽根據收到的閱讀器的命令,將內存的標識性數據回傳給閱讀器。這種通信是在無接觸方式下,利用交變磁場或電磁場的空間耦合及射頻信號調制與解調技術實現的。

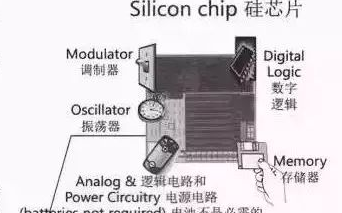

電子標簽通常由標簽天線(或線圈)和標簽芯片組成。電子標簽芯片即相當于一個具有無線收發功能再加存貯功能的單片系統(SoC)。從純技術的角度來說,射頻識別技術的核心在電子標簽,閱讀器是根據電子標簽的設計而設計的。

電子標簽依據發送射頻信號的方式不同,分為主動式和被動式兩種。主動式標簽主動向閱讀器發送射頻信號,通常由內置電池供電,又稱為有源電子標簽;被動式標簽不帶電池,又稱為無源電子標簽,其發射電波及內部處理器運行所需能量均來自閱讀器產生的電磁波。無源電子標簽在接收到閱讀器發出的電磁波信號后,將部分電磁能量轉化為供自己工作的能量。

一般來說,有源電子標簽具有更遠的通信距離,但其價格相對較高,主要應用于貴重物品遠距離檢測等應用領域。無源電子標簽具有價格低的優勢,盡管其工作距離和存儲容量受到能量的限制,但有巨大的市場潛力,是目前業界研發的熱點。

無源電子標簽芯片主要包括3個部分:模擬電路、數字控制和電可擦除可編程只讀存儲器(E2PROM)模塊。其中,模擬電路模塊又包括電源產生電路、調制解調電路等。

1 超高頻無源電子標簽芯片模擬電路的設計要求

超高頻(UHF)無源電子標簽芯片是基于ISO/IEC 18000-6C標準而設計的[1],ISO/IEC 18000-6C標準是繼ISO/IEC 18000-6A、ISO/IEC 18000-6B標準之后的新標準,它對前兩種標準的協議特點進行了一系列有效的修正與擴充。其中物理層數據編碼、調制方式、防碰撞算法等一些關鍵技術有了改進,使得ISO/IEC18000-6C的性能比ISO/IEC 18000-6A、ISO/IEC 18000-6B有了很大的提高。

在標簽設計時,標簽芯片的模擬電路部分必須要與標準中規定的空中接口參數相一致,其主要參數規格如表1所示。

表1中的參數主要是按照ISO/IEC 18000-6C標準選擇,其中標簽射頻輸入功率的計算過程如下。

由電磁場理論可知標簽天線處的電磁場能量密度:S =P /Ae =P /[λ2/(4π)]=4πP /λ2=1/2·E 2/η,其中S是標簽天線處的電磁場能量密度,P是標簽天線接收到的能量,Ae是標簽天線的等效接收面積,λ是閱讀器發射電磁波的波長,E是標簽天線處的電場強度,η是空氣的波阻抗。

進而推導出標簽天線處的電場強度為:![]()

當采用半波對稱陣子當作標簽天線時,每個陣子長度為λ/4,所以標簽天線上的感應電壓為:U =E·d =,其中d為單個陣子的長度。

由電荷泵電路可知,電荷泵輸入端的電壓必須大于等于0.8 V時才能開啟整個電荷泵電路進行充電。因此U≥0.8 V,也即:≥0.8,把空氣的波阻抗η=120·π帶入可求得P≥1.1 mW。也即射頻輸入功率至少為1.1 mW才能使標簽正常工作。

2 模擬電路設計

無源電子標簽芯片的模擬電路部分主要分為調制電路、解調電路和電源產生電路3個部分,除此之外還有上電復位電路等,如圖1所示。

調制電路對基帶數據進行射頻調制,設計中主要采用逆向散射調制,即用數據比特流調制標簽天線的輸入阻抗來改變反射回閱讀器信號的幅度,從而實現類似于幅度調制(AM)的逆向散射調制。解調電路完成對閱讀器發射來的命令信息進行解調,電源產生電路必須能夠為芯片中的電路提供穩定充足的電能,在設計中采用電荷泵作為電源產生電路。此電路相對較為復雜,是整個芯片模擬電路部分最為關鍵的部分。

2.1 調制電路

標簽芯片是基于ISO/IEC 18000-6C標準設計的,因而標簽芯片中的調制電路采用逆向散射調制來實現FM0/Miller+ASK調制,也就是用數據比特流調制標簽天線的輸入阻抗來改變反射回閱讀器信號的幅度,從而實現類似于AM調制的逆向散射調制,如圖2所示。

此標簽芯片逆向散射調制電路采用消除了襯底調制效應的互補金屬氧化物半導體(CMOS)開關電路來實現,用數字電路送過來的數據比特來控制CMOS開關的開與關,也即改變單溝道CMOS開關的輸入阻抗,由于CMOS開關是并聯在天線兩端的,因而就改變了天線的輸入阻抗,實現了逆向散射調制的功能。

2.2 解調電路

芯片的解調電路如圖3所示,從天線接收過來的信號先經過頻帶選擇濾波器濾波,然后用包絡檢波電路檢波,再用施密特觸發器對波形進行整形,最后使用1.28 MHz的本地時鐘對整形后的數據進行采樣并計數每個數據比特對應的1.28 MHz脈沖的個數。

(1) 帶通濾波器

為了減少電容和電感數量,節省芯片面積,采用2級反轉Chebyshev濾波器,仿真結果表明其中心頻率為905 MHz,帶寬是220 MHz,相對帶寬是24%,滿足了設計要求。

(2) 包絡檢波器

包絡檢波器由二極管和并聯的RC電路組成,只有時間常數RC大于等于載波周期的100倍時,包絡檢波器的輸出信號才能夠正確地跟隨輸入端調制信號的包絡變化[2]。鑒于芯片采用CMOS工藝,我們使用金屬氧化物半導體(MOS)管實現包絡檢波器中的二極管、電容和電阻。

在ADS中仿真設計的包絡檢波器,結果表明:當輸入的ASK調制信號的載波頻率在860~960 MHz間變化,基帶信號周期在6.25~25 ?滋s間變化時,檢波器均能較好的解調出包絡。但檢波后得到的信號波形不是理想的矩形脈沖,出現了較大的變形,因此為了保證后續電路的正常工作,必須對變形的波形進行整形處理。

(3) 施密特觸發器的設計

由上面的分析可知,包絡檢波后的信號出現變形,可能會導致后續的解碼電路產生錯誤,因此需要對出現變形的信號進行整形處理。我們采用施密特觸發器來消除脈沖變形。

(4) 本地時鐘電路的設計

由于閱讀器到標簽的數據速率在26.7~128 kb/s之間變化,標簽到閱讀器的數據速率在40~640 kb/s之間變化,因此為了正確地調制和解調數據,必須有多種速率的時鐘。經過計算得知:芯片中只要有一個1.28 MHz的時鐘,經過一系列的分頻就可以得到所需的全部時鐘。由于時鐘速率很低(1.28 MHz),使用常用的LC振蕩器實現時鐘電路,將要用到非常大的電感和電容,而在面積很小的芯片中實現大數值的電感和電容是不現實的,因而不能采用LC振蕩器。

本次設計中我們采用環形振蕩器來產生本地時鐘[3-4]。此環形振蕩器由奇數個CMOS反相器閉環連接構成,這樣的環形振蕩器具有集成度高和消耗能量少的優點。此外為了增加每級反相器的延遲時間,除最后一級反相器外的反相器輸出端和地之間都接有電容。改變反相器的級數、電容數值以及MOS管的尺寸可以調整振蕩器的振蕩頻率到所需的數值[5]。我們設計中采用5級反相器構成環形振蕩器,為了提高集成度,我們使用漏極和源極連接到地的N溝道金屬氧化物半導體(NMOS)管當作電容,調整MOS管的長度和寬度,最后在ADS中仿真時鐘電路得到的仿真結果表明可以作為芯片中所需的1.28 MHz的時鐘源。

2.3 電源產生電路

電源產生電路結構框圖如圖4所示。天線接收到的射頻信號經過射頻-直流(RF-DC)轉換電路轉化為不低于VL的直流電壓,然后經電壓限幅器限幅后得到穩定的直流電壓VL(2.8 V)供給除E2PROM外的電路工作;VL和本地時鐘信號經過直流-直流(DC- DC)轉換電路和電壓限幅器轉化為直流電壓VH(12 V)供E2PROM使用。

(1) RF-DC轉換電路

RF-DC轉換電路基于電荷泵電路設計,其原理如圖5所示,芯片設計時用柵源短接的增強型NMOS管代替圖5中的二極管。設RF-DC轉換電路所需二極管的最小個數為n1,則所需電容個數也為n1,由于每級電荷泵由2個電容和2個二極管構成,n1必須為偶數。

(2) DC-DC轉換電路

DC-DC轉換電路也是采用電荷泵原理來設計。由于電子標簽解調電路已有本地時鐘電路(通常采用CMOS環形振蕩器產生幅度為VL /2的時鐘信號),因此用時鐘信號代替射頻信號對電荷泵充電,并從RF-DC轉換電路已產生的直流電壓VL開始充電可以顯著減少DC-DC轉換電路的電路級數。設此電路所需二極管最小個數為n2,則此電路所需二極管最小個數n2為[6]:

![]()

其中表示偶數上取整,即先執行上取整,如果上取整后不是偶數則數值加1。

(3) 電壓限幅器

標簽工作時,由于標簽和閱讀器距離的變化以及傳播環境的不同,標簽天線接收到的射頻信號的幅度變化可以高達10倍以上,使電源產生電路輸出的直流電壓產生很大的波動。因此必須對RF-DC、DC-DC轉換電路的輸出電壓進行限幅。我們采用穩壓二極管限幅原理對RF-DC、DC-DC轉換電路的輸出電壓進行上限幅,即把多個飽和MOS管串聯起來充當二極管限幅器。調整MOS管的寬長比以及摻雜濃度來調整限幅值為所需數值。

3 結束語

本文基于ISO/IEC 18000-6C標準,給出了UHF無源電子標簽芯片模擬電路的設計,設計結果表明電路具有很高的整流效率,滿足了設計要求。下一步的研究將進行標簽芯片的版圖設計和流片,用實際測試結果來進一步驗證設計的有效性。

電子發燒友App

電子發燒友App

評論