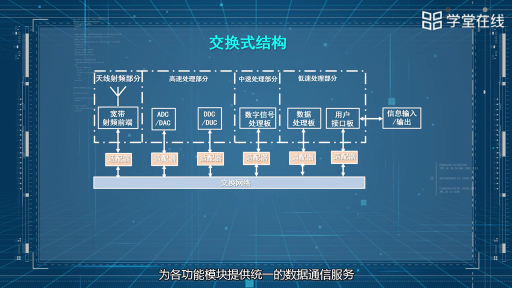

鑒于SDR的接收器僅僅由一個低噪聲放大器 (LNA) 和一個濾波器和ADC組成,隨著半導體行業在RF采樣模數轉換器 (ADC) 領域的進步,那些預見到真正軟件定義無線電 (SDR) 的系統工程師們借此得以實現了之前的設想。例如:在RF波段范圍處于700MHz到3.8GHz之間的蜂窩通信基礎設施中,這一愿望就將很快成為現實。這是因為隨著越來越多功能越來越強大的設備的涌現,能夠滿足用戶對更小外形尺寸、更低系統功耗和更高密度的要求,從而讓系統設計師的構想成為可能。

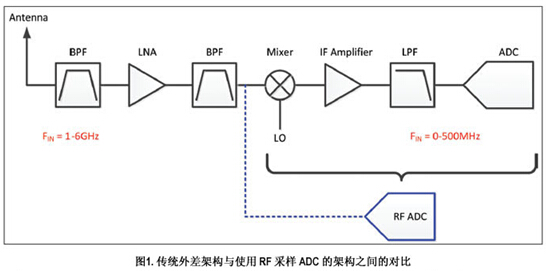

目前的高性能接收器主要使用一種外差架構,在這種架構中,輸入信號的RF范圍在700MHz到數兆赫茲之間,隨后下行轉換為DC-500MHz之間的低中頻 (IF)。例如在某些諸如軍用雷達的應用中,當從10GHz(X波段)或者25至40GHz(Ka波段)范圍內高很多的初級RF波段進行下行轉換時,次級IF就在1至3GHz范圍(S波段,L波段)。

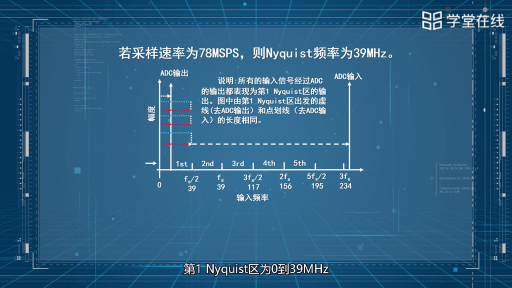

RF采樣ADC直接采集RF輸入,并因此取代了圖1中所示的整個下行轉換級。由于不使用RF本地振蕩器 (LO)、混音器和額外的增益與濾波級,從而節省了印刷電路板 (PCB) 面積,并可以實現更加緊湊的系統設計。ADC的兆赫茲采樣時鐘,在輸入處于第二那奎斯特區間內或者更高區間內時,將已采樣RF能量下行轉換為較低的數字中間頻率,從而成為高效LO。與外差架構中的混音器LO相類似,ADC時鐘需要極佳的相位噪聲來防止來自較大信號的能量混合進入小信號所處的同一頻率,因為這樣會降低接收器的靈敏度。

傳統RF采樣ADC需要極寬的數字接口來輸出數據。由于低壓差分信令 (LVDS) 通常情況下的速度最高只有大約1Gbps,所以一個12位,4Gsps ADC將會需要大約49個差分對(其中的48個用于數據,剩余的一個用于時鐘)。這就要求足夠大的封裝尺寸,和在PCB上較大的走線面積。而例如ADC12J4000使用了一款10Gbps JESD204b接口,只用8個差分對即可傳送同樣的數據量—將所需的差分對數量減少了83%(圖2)。對于窄帶應用來說,片上數字抽取濾波器 (DDC) 可實現片上芯片濾波,以進一步減少數據流量和所需的信道數量。例如,一個帶寬為100MHz的信號,只使用一條5Gbps的單信道即可以250Msps的速度進行傳輸(具有IQ輸出的抽取因子32)。

RF采樣ADC的信噪比 (SNR) 遠遠低于IF采樣ADC,然而動態范圍并沒有變差。其原因是它們用過采樣來彌補了其中的差距,并且通過將每赫茲水平的SNR標準化實現了差不多的SNR。

例如,信噪比為70dB SNR的14位,250Msps ADC的噪聲頻譜密度 (NSD) 為-151dBFS/Hz,而信噪比為55dB SNR的12位,4Gsps ADC的NSD為-148dBFS/Hz。它們之間的差異只有3dB。

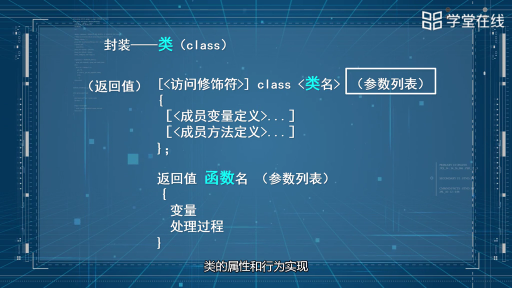

RF采樣ADC的優勢

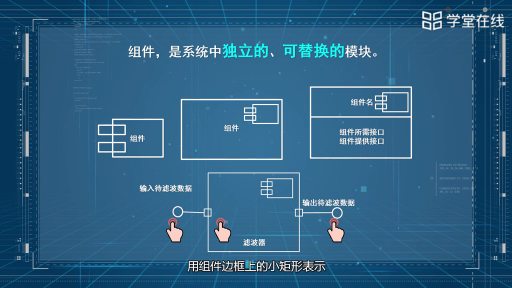

RF采樣ADC有兩個明顯優勢,一是將大量信號帶寬數字化,二是直接在RF上捕捉信號,從而簡化了信號鏈。

但它還有一個鮮少被提及的優勢,即在所需信號波段遠遠小于采樣率時,它能夠使用快速采樣率進行頻率規劃。選擇一個至少比信號帶寬快5至10倍的采樣率可以使系統設計人員能夠規劃那些無法濾除的帶內干擾源的負面影響,因此可實現更好的動態范圍。

與外差接收器正好相類似的是,ADC的無雜散動態范圍 (SFDR) 性能限制了對低輸入信號的檢測功能(圖3)。所需帶寬內的干擾源(或者是通信基礎設施中的攔截器)是無法濾除的。這就要求信號鏈降低增益來避免ADC飽和。信號鏈中減少的增益會削弱把小信號(例如,“有用信號B”)提升到ADC噪底以上的能力,因而不能進行適當的檢測。帶內干擾源的諧波雜散還會落在有用信號的頂部,從而限制了接收器的靈敏度。這是軍用雷達(用來偵測小型物體),軟件定義無線電和蜂窩基站中的一個關鍵要素。

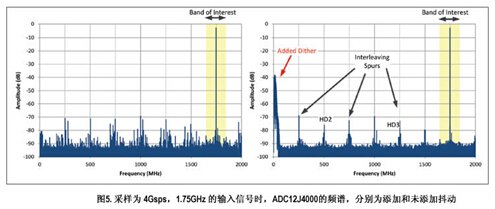

在過采樣配置中使用RF采樣ADC(諸如ADC12J4000)可以避免干擾源的限制諧波對小幅有用信號的阻斷。例如,200MHz的所需帶寬可在中央頻率為1.75GHz的RF上,以4Gsps的采樣率進行采樣。前四個通常是高速ADC中最差的諧波(HD2,HD3,HD4和HD5),以及其他來自帶內干擾源的交叉雜散就全都落在了波段之外(圖4)。

ADC采樣率的加快也放寬了對為驅動放大器所需的對抗混疊濾波器的要求。200MHz波段可以用500Msps ADC進行采樣,但是將會需要非常精確的濾波器,這是因為下一個圖像只隔了50MHz(假定波段在那奎斯特區域的中心)。相反地,采樣率為4Gsps,以1.75GHz為中心的同一波段,就只需要和針對最近距離大約為300MHz的圖像(混疊 = 2.15-2.35GHz,交叉圖像 = 1150-1350MHz)同樣的波段外濾波器衰減技術規格,對濾波器的要求就放寬了許多。

在成功使用頻率規劃后,SFDR性能只受到較高階諧波(不是HD2-5中的任何一個)的限制。可以通過采用小信號抖動來進一步改進這些較高階雜散。兆采樣RF ADC的高采樣率提供很多“未占用”頻譜,可將波段受限抖動放置在其中,而又不會影響到任何有用信號(圖5)。

抖動是軟件定義無線電中的常用技術,并且可將雜散底噪改進5至10dB。

總結

目前諸如ADC12J4000的RF采樣ADC可以大大提高超寬波段接收器的使用和性能。其高輸入帶寬在RF上直接實現了信號的數字化,與此同時,快速采樣率又降低了濾波器要求,并實現了帶內干擾器諧波周圍的頻率規劃。通過添加片上數字濾波器來大大降低數字接口數據流量,從而使ADC12J4000成為小型、低功耗、下一代數字無線電的完美選擇 。

電子發燒友App

電子發燒友App

評論