引言

隨著當今電子、計算機技術的飛速發展,射頻技術作為一種無線網絡通訊手段,已經在越來越多的場合上使用,并且表現出其獨特的優越性。它取代了傳統中錯綜復雜的電纜,使家庭或辦公場所的移動電話、便攜式電腦、打印機、復印機、鍵盤及其他設備實現了互聯互通,將人們從無數的連接電纜中解放出來,自由方便地構成自己的個人網絡。作為取代數據電纜的短距離無線通信技術,它將家庭或辦公室中的各種數據和語音設備聯成一個微微網,還可以進一步實現互聯,形成一個分布式網絡,從而在這些聯接設備之間實現快捷而方便的通信聯系,因此它在無線網絡系統中的發展潛力巨大。

?

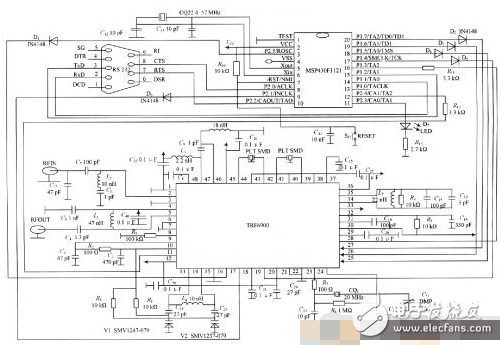

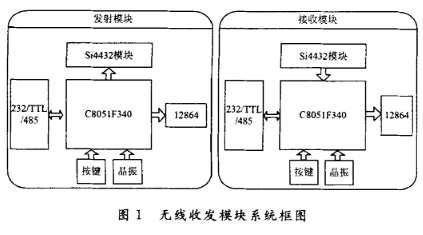

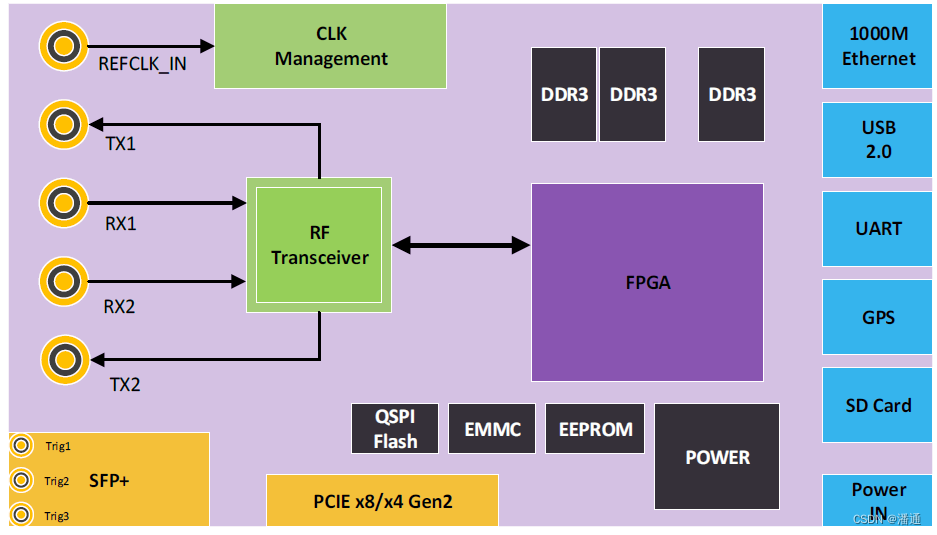

1 系統硬件組成與工作原理

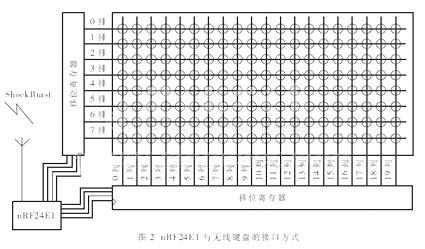

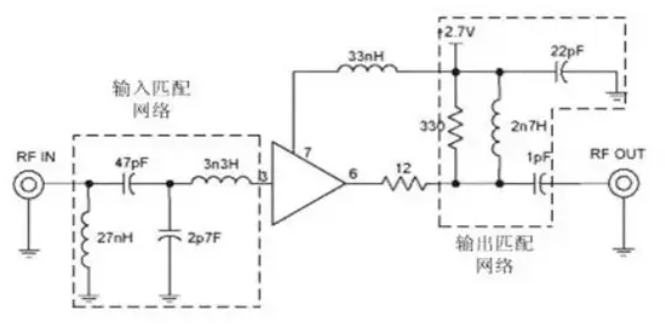

射頻與數字基帶部分電路通過合適的方式連接起來就構成了所設計的無線射頻收發應用系統的硬件電路,總體電路如圖l所示。其中,帶有箭頭的表示接外加的電壓,以保證電路正常工作,其工作電壓為3 V。

1.1 系統主電路結構與原理

射頻部分電路主要是用TRF6900收發芯片和一些外圍元件設計成的射頻收發器。TRF6900是TexasInstruments公司推出的單片射頻收發器芯片,其內部集成了完整的發射電路和接收電路。它的工作頻率范圍為850~950 MHz,供電電壓范圍為2.2~3.6 V,射頻輸出功率高達+5 dBm,而待機模式時的電流消耗僅在O.5~5μA之間。TRF6900采用高吞吐率16 bRISC結構,其最快速率可達8 MIPS。另外,這種收發器還具有FM/FSK調制模式,并采用三線制串行接口,因而能很方便地與微控制器相連接,可用于ISM頻段內數據的雙向無線傳輸,能夠容易地對它的收發進行控制,因而基于它的應用也越來越普遍。

1.1.1 接收原理

從天線接收到的信號由LNA IN引入TRF6900,首先經過低噪音放大器。低噪音放大器提供13 dB的增益,它有正常和低增益兩種模式,當TRF6900接收的信號較強時,應該選擇低增益模式,這樣可以最大程度地減少信號的非線性失真。放大后的信號被送入混頻器,混頻器將信號變頻到中頻,再通過第一和第二級中頻放大。第一級中頻放大可獲得7 dB的增益,用以補償濾波器帶來的損耗;第二級中頻放大包括多個放大器,總共可獲得80 dB的增益。經過兩級放大后的信號,如果采用的是FM/FSK調制方式,就送入FM/FSK解調器,解調出的數據信號從DATA OUT引出。如果是頻移鍵控(ASK)或開關鍵控(OOK),則送入接收信號強度指示器(RSSI)解調,解調后的基帶數據從RSSI OUT輸出。

1.1.2 發射工作原理

數字基帶信號從TX DATA引入TRF6900片內,經過直接數字頻率合成器(DDS)調制到中頻,再通過鎖相環(PLL)倍頻到射頻,最后通過功率放大器放大信號后,由PA OUT導出射頻信號,再通過天線發射出去。

1.1.3 串行控制接口工作原理

串行控制接口包括CLOCK,DATA,STOBE三部分,控制著TRF6900內部所有的寄存器,包括DDS參數設定寄存器和其他的控制寄存器。在CLOCK的每一個上升沿,DATA管腳的邏輯值送入24 b的移位寄存器,當STOBE電平被抬高時,設定的參數被送入選定的鎖存器。TRF6900有四個可編程的24 b控制字(A,B,C,D)。控制字A和B分別控制DDS模式0和模式1狀態下輸出信號頻率。控制字C負責鎖相環和DDS模式O的設定。控制字D負責調制和DDS模式1的設定。

1.2數字基帶部分

數字基帶部分基于微型控制器MSP430F1121。通過它將外部的模擬信號轉換為適合TRF6900的數字信號,再配合軟件設計可以很方便地進行智能化轉換。數字基帶部分的硬件電路由RS 232和MSP430F1121組成,如圖1所示。

MSP430F112l微型控制器是一款超低功耗、高性能的16位精簡指令集MCU,主要由以下部分組成:基礎時鐘模塊,包括1個數控振蕩器(DCO)和1個晶體振蕩器;看門狗定時器Watchdog Timer,可用作通用定時器;帶有3個捕捉/比較寄存器的16位定時器Timer_A;2個具有中斷功能的8位并行端口:P1與P2;模擬比較器Comparator A。

?

2 系統參數計算

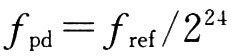

2.1 鑒相器的參考頻率

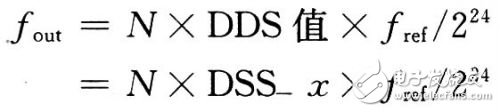

鑒相器是PPL構成鎖相環中的單元模塊之一,其輸入的參考頻率是由DDS的輸出信號決定的。基于DSS技術的頻率合成器能很好地滿足各項指標性能,同時也使設計變得簡單。鑒相器輸出頻率的分辨率為:

式中:fpd是鑒相器的最小輸入頻率,也是DDS時鐘頻率fref的2°,即最低有效位的權值。TRF6900 DDS累加器有24位,fpd乘以預標值N(可選擇256或者512),由它可得出最小頻率的步進值為:

累加器的輸入是24位的用戶串行數據(控制字),時鐘基準信號作為累加器的工作時鐘信號,兩者決定頻率的分辨率;輸出是一串抽樣斜坡數字脈沖,空號頻率等于時鐘頻率。經過D/A轉換后得到模擬域的正弦信號fo_DSS,它代表基準相位,即作為鑒相器的基準輸入信號。DDS的最終性能主要取決于D/A轉換過程中的量化誤差以及濾波特性。

?

2.2 晶振時鐘電路及頻率

2.2.1 時鐘電路的設計及參數計算

晶振采用并聯諧振的工作方式,如圖1中23~24腳外圍電路所示。電路總的相移為360°,其中反向器提供180°的相移,R7和C22提供90°的滯后相位,晶振和電容C1也帶來90°的相位滯后。并聯工作的晶振是作為電感用的。晶振接入電容補償相移以滿足振蕩條件。

偏振電阻R1用于設置反相器的偏置點,典型值是Vcc引腳值的二分之一。R1過小,將降低環路增益,破壞網絡反饋條件,典型值是1~5 MΩ。可以觀察23引腳的輸出頻率隨電壓的變化情況。如果晶振有過驅動,則增大電壓后,輸出頻率會下降,此時應該微調電阻R2(調高)。注意,R2應該足夠小,以確保振蕩器在小于最小工作電壓的情況下能夠起振。C1和晶振的旁路電容Co及反相器的輸入電容共同構成了晶振的輸入電容。要提供穩定度,晶振的輸入電容典型值可選擇20~30 pF。

2.2.2 頻率的選擇

根據抽樣定理可知,時鐘頻率fref(fref/2即為Na-quist頻率)對量化噪聲功率、冗余信號電平以及輸出頻譜中由于不滿足抽樣定理而帶來的干擾信號、時鐘頻率和鑒相器的參考基準頻率fo_DSS(即由DSS得到的信號頻率fref/fo_DSS)的比率越大,頻率合成器的輸出信號頻譜所受到的干擾就越少。時鐘頻率的具體計算方法如下:

假設要使基于DDS的PLL構成的頻率合成器的輸出頻率為906.24 MHz(與DSS得到的輸出信號頻率fo_DSS即鑒相器的參考基準頻率要區別開來),經過256或者512分頻(可選),假設為256,那么DDS的輸出信號頻率fo_DSS就應等于906.24/256=3.54 MHz,可得到PLL的輸出頻率的計算公式:

式中:預標值N可選擇256或者512,DDS_x為控制字A或B的值。

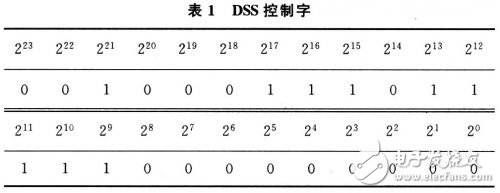

DSS頻率值可通過串行口控制字編程設置,其最低有效位是2°,最高有效位是223。兩個最高位(23,22位)用戶不可訪問,系統內部自動置為0,21-0位,并由用戶編程設置。其中,A字對應DDS-O即模式0的頻率;B字對應DDS-1即模式1的頻率;C字控制PLL、數據限制器和模式1寄存器的設置;D字控制調制方式(如頻偏大小)和模式O寄存器的設置。

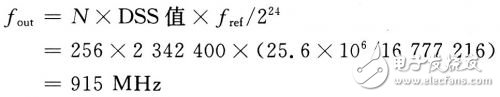

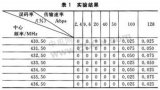

2.3 載波頻率計算

由時鐘頻率經過基于DDS的頻率合成器可得到VCO輸出的載波頻率。對于典型的25.6 MHz時鐘頻率,由表1可得當DDS控制字為001,000,111,0000,000,000時,可計算出的VCO輸出頻率即載波頻率為915 MHz。

由表1可知:

?

?

?

最后的VCO輸出頻率為:

?

2.4 DSS控制字的計算

TRF6900的FSK調制是由專門的FSK頻偏寄存器來完成。A,B控制字用來設置接收機和發射機的頻率及信道。在應用系統的使用中,A,B控制字用來設置FSK頻偏。用于FSK方式時DDS控制字的計算方法如下:

假設載波頻率為915.O MHz,頻偏為20 kHz,即A字對應的VCO輸出頻率fout1=915.00 MHz;B字對應的VCO輸出頻率fout2=915.02 MHz;時鐘頻率fclock=fref=25.6 MHz;分頻比N=256。下面計算A,B控制字:

A字對應于DDS_O值:

所得的二進制的DDS_O將裝入A控制字中。

B字對應于DDS_1值:

所得的二進制的DDS_1將裝入B控制字中。

2.5 本地振蕩器

TRF6900的本地振蕩器(LO)是鎖相環PLL形式,由基于片上DDS的頻率合成器、低通濾波器(LPF)和壓控振蕩器(VCO)構成。

2.5.1 VCO的電路設計

壓控振蕩器是輸出信號頻率隨輸入控制電壓變化的振蕩器。為了減小相位噪聲,VCO電路通常由分立元件構成。

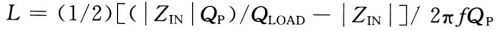

LC諧振槽路的諧振頻率:

諧振頻率時的電感值:

式中:|ZIN|為TRF6900內部振蕩器的輸入阻抗;QLOAD為諧振回路的品質因數;QP為電感的品質因數;f為諧振頻率。

2.5.2 VCO的靈敏度

變容二極管的電容大小與調諧電壓成正比,VCO的靈敏度:

2.5.3 參數計算

設計的無線收發電路工作在868~928 MHz ISM頻段。假設TRF6900的VCO輸出頻率為880~950 MHz,調諧電壓為0.3~2 V。TRF6900振蕩器的輸入阻抗|ZIN|即引腳13和14間的電阻大小約為1 400 Ω;諧振回路的品質因數必須大于等于10;在915 MHz時,電感的品質因數大約等于80。由公式可得:L≤10.65 nH,取L=10 nH標準值。

從方程中可知:

為了擴大變容二極管的調諧范圍,根據以上的計算,C2可以取2.2pF,C1可取3.3pF。

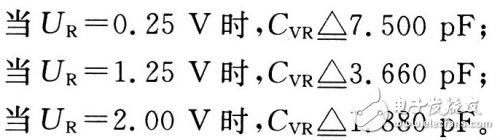

設計時采用Alpha Industries的SMV1247系列變容二極管,其參數如下:

要注意的是因為PCB的分布電容不可預測,隨工作頻率變化而變化,所以在PCB調試時要進行必要的修正,這里采用經驗值。

現在對上述元件參數進行驗證:

對于0.25 V時的ftune,依據公式有CTOTAL=3.346 pF;

對于2.00 V時的ftune,有CT0TAL=2.799 pF。

由上述方程式可知,槽路的諧振頻率:MHz,,2 MHz。顯然,能滿足880~940 MHz頻率調諧范圍。對于滿足880~940 MHz的頻率調諧范圍的元件參數,取L=10 nH,C1=3.3 pF,C2=2.2 pF,變容二極管為SMVl247-079。最后可得出VCO的靈敏度MHz/V。

2.5.4 環路濾波器的設計

(1)計算公式

環路濾波器是一個典型的二階低通濾波器,用于頻率合成器中電荷泵電流模式。二階元件的計算公式:

?

式中:KPD為鑒相器增益(單位:A/rad),KPD=ICP/2π;KVCO為VCO增益(單位:rad/V);N為分頻比;ζ為阻尼比,有效范圍是0<ζ<1,典型值為O.707;ωN為自然諧振頻率(單位:rad/sec),ωN=(2×BN)/[(ζ+1)/2]2。

(2)設計注意事項

VCO有加速和正常兩種工作模式,鎖存時間都要小于250μs。正常模式用于精確控制并保持VCO工作所需頻率;加速模式利用APLL鎖相環加速因子來提供快速粗調,它可以使用TRF6900軟件根據需要進行調整。DSS的諧振通常在環路帶寬內,不能用環路濾波器抑制,但降低環路濾波的帶寬可以減小DSS諧波產生的可能性。正確選擇時鐘基準頻率能較好地抑制DSS諧波。

?

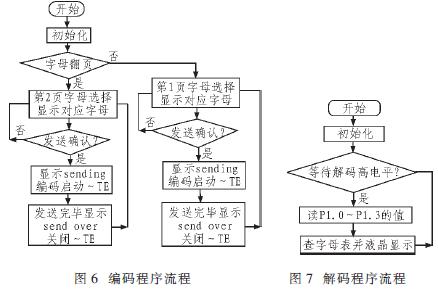

3 系統軟件設計

軟件部分主要由主程序和各個子程序組成。主流程圖包括兩部分:一是設備初始化;二是循環部分(loop main)設置相關的循環程序。初始化部分主要是設置端口、模式和時鐘系統;循環部分(loop main)提供RS 232和射頻(RF)通信,包括校驗總和的初始化。篇幅所限這里不做介紹。

?

4 結語

本設計根據TRF6900收發芯片的特點和微型控制器MSP430F112的優點設計的無線數據收發系統,經過多次實驗證明,其發射端能正確地將數據傳送出去;同時,經TRF6900發射后,接收端也能正確接收并顯示數據。系統完成了比較完善的硬件設計以及抗干擾措施,今后將繼續開發系統軟件,這樣就可以保證系統工作的安全性和可靠性,并具有通用性,便于投入實際應用,具有廣泛的市場應用價值。?

電子發燒友App

電子發燒友App

評論