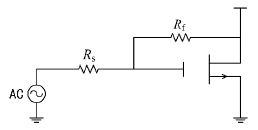

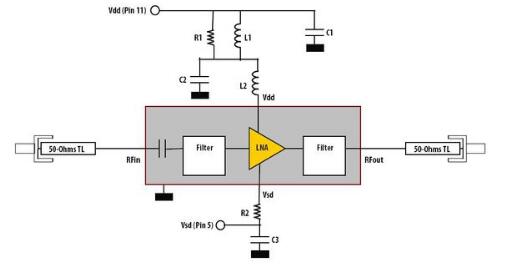

低噪聲放大器是無線接收系統中第一個模塊,影響著整個系統的噪聲性能和靈敏度等參數。隨著超寬帶技術的發展,寬帶低噪聲放大器設計已成為當前設計的一個熱點。根據目前國內外發表的相關文獻,當前寬帶低噪聲放大器的結構大致有帶通濾波網絡匹配和電阻負反饋2 種結構。

2018-09-05 08:11:00 4577

4577

低噪聲放大器設計資料

2022-11-22 09:16:52 712

712 低噪聲放大器低噪聲放大器(LNA)被用來將天線收到的微弱的無線蜂窩信號,放大到混頻器所需要的幅度。如果低噪聲放大器損壞,通常會造成手機接收信號差的故障。低噪聲放大器通常又稱為前置射頻放大器,前置

2021-07-27 07:57:52

更少,放大器是當今RF/IF信號鏈中功能最多樣的構建模塊之一;想請教一下大牛 ;低噪聲放大器和中頻放大器有什么樣的特性?

2021-04-07 06:52:54

低噪聲放大器除了用于接收機的信號放大以外,在測試和測量中也經常用到。以下列舉了一些低噪聲放大器在射頻測試和測量中的典型應用。一、用于電磁環境測量電磁環境測量是保證各類無線電業務正常開展的必要環節

2017-11-08 10:10:46

低噪聲放大器除了用于接收機的信號放大以外,在測試和測量中也經常用到。以下列舉了一些低噪聲放大器在射頻測試和測量中的典型應用。一、用于電磁環境測量電磁環境測量是保證各類無線電業務正常開展的必要環節

2018-01-23 09:52:05

低噪聲放大器在無線數據接收中有哪些應用?

2019-08-23 07:08:00

低噪聲放大器設計 線性仿真

2019-03-15 17:23:22

低噪聲放大器(LNA)是怎樣提出來的?低噪聲放大器(LNA)有哪些優勢?低噪聲放大器(LNA)主要應用在哪些領域?

2021-04-23 06:46:07

`低噪聲放大器,噪聲系數很低的放大器。一般用作各類無線電接收機的高頻或中頻低噪聲前置放大器,以及高靈敏度電子探測設備的放大電路。在放大微弱信號的場合,放大器自身的噪聲對信號的干擾可能很嚴重,因此希望

2017-09-11 15:43:24

ADS設計低噪聲放大器的詳細步驟

2012-08-20 07:56:37

(頻分多址)和TDMA(時分多址)相比,具有系統容量大而且配置靈活、頻譜利用率高、軟切換、保密性能好的優點。基于這些優點CDMA技術得到了廣泛的應用。 CDMA低噪聲放大器作為CDMA接收機的第一

2019-06-19 07:03:12

(頻分多址)和TDMA(時分多址)相比,具有系統容量大而且配置靈活、頻譜利用率高、軟切換、保密性能好的優點。基于這些優點CDMA技術得到了廣泛的應用。CDMA低噪聲放大器作為CDMA接收機的第一

2019-07-09 08:14:06

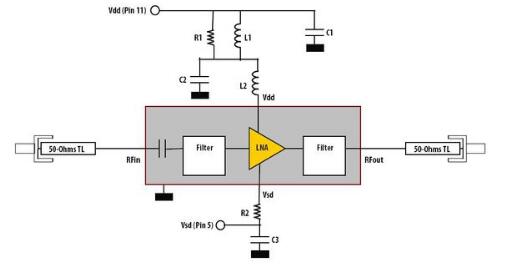

CMD132是Custom?MMIC的X波段寬帶低噪聲放大器,該放大器適用于C波段和X波段的微波無線放大器應用,MMIC提供設計和測試服務,其中產品RF毫米波電路可用于衛星通信,雷達系統,蜂窩

2019-07-17 10:13:32

如何優化LNA的指標?MAX2640低噪聲放大器用于ISDB-T設計,有什么優勢?

2021-04-20 07:13:51

` 本帖最后由 330538935 于 2018-6-13 17:56 編輯

QPB9331低噪聲放大器產品介紹QPB9331報價QPB9331代理QPB9331咨詢熱線QPB9331現貨

2018-06-13 17:37:43

RFFM4527低噪聲放大器產品介紹RFFM4527報價RFFM4527代理RFFM4527咨詢熱線RFFM4527現貨,王先生深圳市首質誠科技有限公司RFFM4527是一個低噪聲放大器(LNA

2018-06-14 14:55:20

`SPF5043Z 低噪聲放大器產品介紹SPF5043Z報價SPF5043Z代理SPF5043Z咨詢熱線SPF5043Z現貨,王先生深圳市首質誠科技有限公司SPF5043Z一種高性能GaAs

2018-06-22 10:28:00

目前,有關低噪聲放大器的討論常常關注于RF/無線應用,但實際應用中,噪聲對于低頻模擬產品(如數據轉換器緩沖、應變儀信號放大和麥克風前置放大器)也有很大影響,是一項重要的考慮因素。為了選擇一款合適

2018-12-19 13:56:15

為什么低噪聲放大器的第一級要盡可能的放大?

2023-11-21 08:01:12

1、低噪聲放大器在通訊系統中的作用隨著通訊工業的飛速發展,人們對各種無線通訊工具的要求也越來越高,功率輻射小、作用距離遠、覆蓋范圍大已成為各運營商乃至無線通訊設備制造商的普遍追求,這就對系統的接收

2019-06-20 06:15:56

【作者】:宮波;李淑華;【來源】:《電子設計工程》2010年02期【摘要】:介紹接收機前端的低噪聲放大器(LNA)對于整個通信設備的接收機系統靈敏度的影響,利用ADS軟件對接收機低噪聲放大器進行改進

2010-04-24 09:02:08

低噪聲放大器是通信、雷達、電子對抗及遙控遙測系統中的必不可少的重要部件,它位于射頻接收系統的前端,主要功能是對天線接收到的微弱射頻信號進行線性放大,同時抑制各種噪聲干擾,提高系統的靈敏度。特別是隨著

2019-08-01 06:31:15

低噪聲放大器性能指標及設計步驟根據噪聲最小設計輸入匹配電路如何利用ADS仿真器設計低噪聲放大器?

2021-04-22 07:24:57

請問如何利用ATF-54143設計一款低噪聲放大器?

2021-04-21 06:56:50

為什么要設計低噪聲放大器?請問如何利用ATF54143設計低噪聲放大器?

2021-04-13 06:26:22

如何采用CHRT的0.35μm RFCMOS工藝,在EDA軟件IC 5.1設計環境中設計了一個2.4 GHz的低噪聲放大器?

2021-04-12 06:41:55

如何設計一種集成度高、匹配方便的寬帶低噪聲放大器?

2021-04-02 07:06:59

放大器設計對噪聲性能的影響是什么常見放大器設計的典型噪聲參數如何正確選擇低噪聲放大器?

2021-04-14 06:17:09

射頻前端低噪聲放大器(LNA)電路是無線電設備前端電路設計中的重要內容。由于實際的無線電傳播環境通常較為惡劣,因此,其射頻前端電路中必須考慮采用LNA。LNA作為射頻模塊中的關鍵電路,其噪聲大小

2019-08-01 06:34:15

如何進行寬頻帶低噪聲放大器的設計?選擇平衡式電路結構來進行寬頻帶低噪聲放大器的設計有什么優勢?

2021-04-06 07:18:10

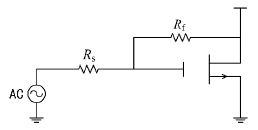

近年來在射頻通訊接收機中,低噪聲放大器的噪聲,增益和線性度直接影響著整個射頻前端的性能,因此它成為整個射頻前端設計的關鍵所在。其中,寬帶低噪聲放大器成為近年來的國內外的研究熱點。寬帶低噪聲放大器主要

2010-05-13 09:06:35

TOP1 射頻低噪聲放大器電路 射頻LNA設計要求:低噪聲放大器(LNA)作為射頻信號傳輸鏈路的第一級,它的噪聲系數特性決定了整個射頻電路前端的噪聲性能,因此作為高性能射頻接收電路的第一級LNA

2021-07-28 08:51:10

的體積要大過低噪聲放大器(LNA)。功率放大器的工作電流在安培數量級,而LNA只需要毫安級的電流。

2019-06-19 08:25:12

怎么實現WCDMA分布式基站低噪聲放大器電路設計?

2021-06-07 06:22:33

、傳感器網絡將逐漸引領人類步入“網絡即傳感器”的傳感時代。 低噪聲放大器LNA ( low noise amp lifier)是射頻接收前端的主要組成部分。由于位于接收前端的第一級,直接與天線相連

2019-08-22 06:06:08

怎樣設計和仿真低噪聲放大器?有什么流程?低噪聲放大器技術指標與設計原則低噪聲放大器設計步驟

2021-04-07 06:19:47

在雷達或無線電接收器中,敏感型低噪聲放大器 (LNA) 在承受較大的輸入信號時必定會發生損壞。那么,有什么解決方案?

2019-08-02 06:26:46

0 引言在雷達射頻接收系統中,對系統性能指標的要求越來越高,其中低噪聲放大器是影響著整個接收系統的噪聲指標的重要因素。與普通的放大器相比,低噪聲放大器作用比較突出,一方面可以減少系統的雜波干擾,提高

2019-07-09 06:08:25

基于HP41511的微波低噪聲放大器的設計

2021-04-06 09:12:27

如何去設計一種2.4 G的低噪聲放大器?對2.4 G的低噪聲放大器怎樣進行仿真?

2021-04-21 06:17:57

高線性低噪聲放大器的工作原理是什么?高線性低噪聲放大器該如何去設計?怎樣對高線性低噪聲放大器進行電磁仿真?

2021-04-22 06:34:26

為什么低噪聲放大器的第一級要盡可能的放大?

2018-08-24 07:15:03

怎么設計一種2.5GHz WiMAX低噪聲放大器?

2021-04-20 06:27:09

怎樣去設計一種低噪聲放大器?如何對低噪聲放大器進行仿真?

2021-05-26 06:04:52

怎樣去設計全集成的低噪聲放大器?怎樣對全集成的低噪聲放大器進行模擬仿真?

2021-04-21 06:18:40

怎樣可以提高低噪聲放大器的測量精度?低噪聲放大器的特點和應用有哪些?如何精準的測量低噪聲放大器的各種指標參數?網絡分析儀系統是如何構成的?低噪聲放大器傳統的測試方法中存在哪些問題?

2021-04-14 06:59:08

一種多模低噪聲放大器電路:

一種多模低噪聲放大器電路,其適合多個射頻接收標準,是一種共源共柵結構的窄帶放大器,其特征在于,包括:輸入匹配

2007-07-16 23:37:54 23

23 Ka波段低噪聲放大器的研鑭:本文介紹了~種毫米波低噪聲放大器的設計技術,應用CAD技術設計了波導到微帶的過渡,結合其它電路設計和組裝工藝,研制出了工作帶寬為3GHz的Ka波

2009-11-01 14:56:59 16

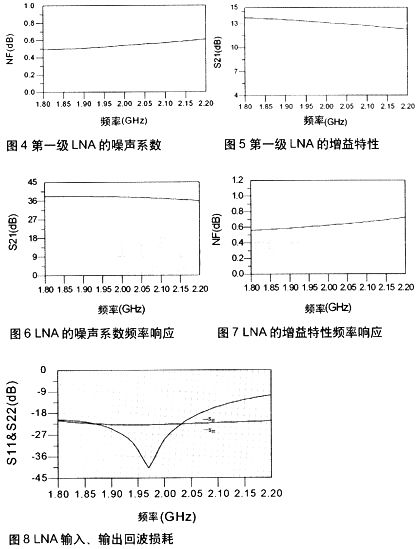

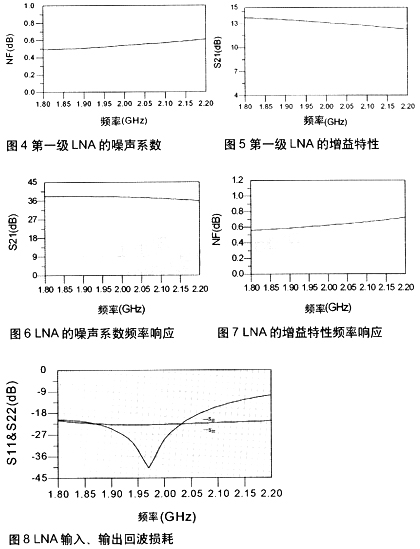

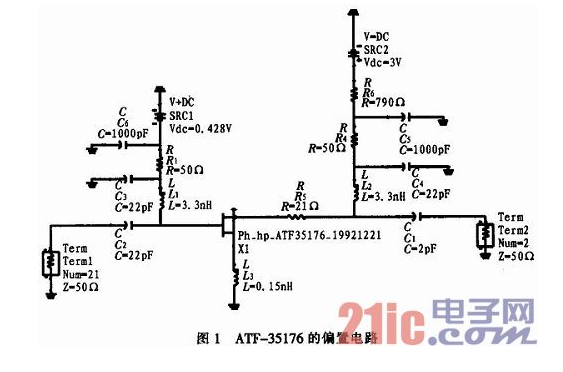

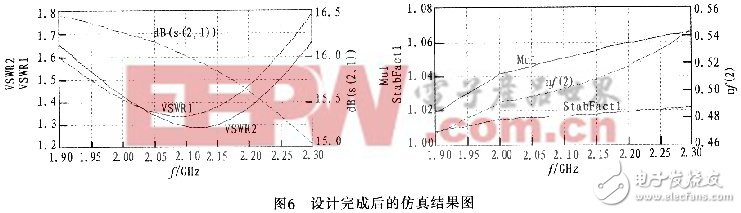

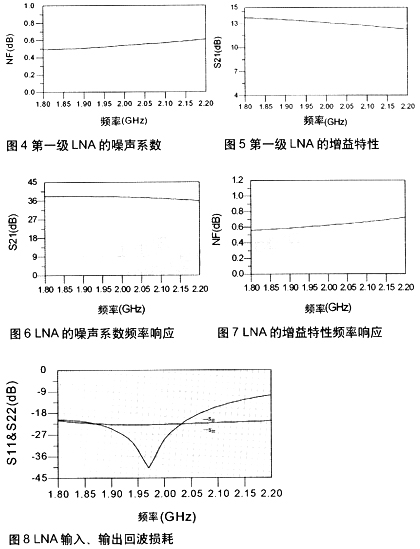

16 射頻低噪聲放大器的ADS設計:本文首先簡要介紹了低噪聲放大器設計的理論基礎,并以2.1-2.4Ghz 低噪聲放大器為例,詳細闡述了如何利用Agilent 公司的ADS 軟件進行分析和優化設計該

2009-11-01 15:07:13 71

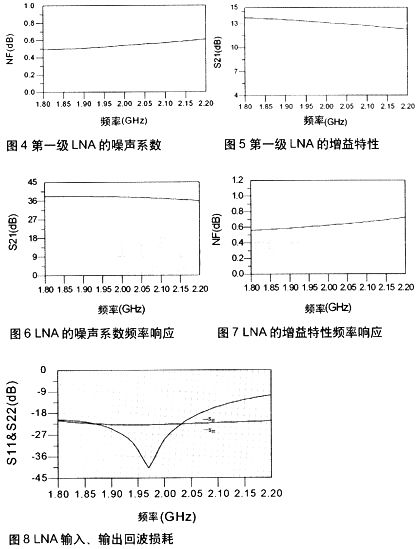

71 S波段低噪聲放大器的分析與設計:介紹了S 波段低噪聲放大器(LNA ) 的設計原理和流程。對影響電路穩定性和噪聲性能的、易被忽視的因素進行了詳細分析。文中重點分析實際電路可能

2009-11-01 15:16:46 20

20 低噪聲放大器設計指南:低噪聲放大器在通訊系統中的作用隨著通訊工業的飛速發展,人們對各種無線通訊工具的要求也越來越高,功率輻射小、作用距離遠、覆蓋范圍大已成為各

2009-11-13 23:04:53 535

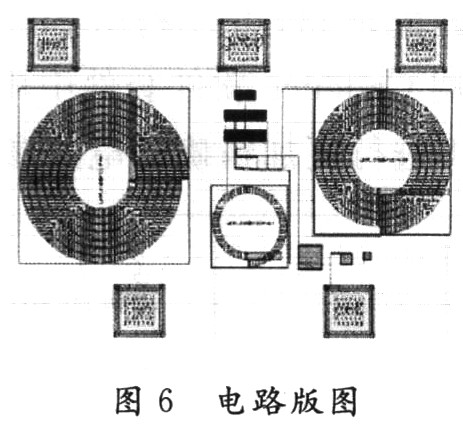

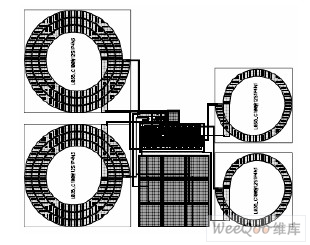

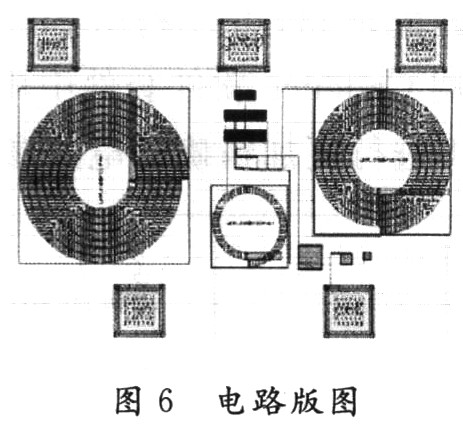

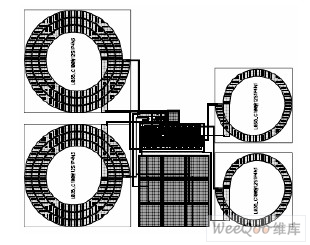

535 論述了在射頻電路仿真軟件ADS中實現低噪聲放大器的整個設計過程,包括低噪聲放大器的晶體管的選取、輸入輸出匹配網絡設計以及實現形式等。結合版圖與系統結構框圖,論述該

2010-07-21 15:18:00 43

43 ?? 摘要:介紹一種用于航天GPS接收機的無源微天線的低噪聲放大器設計。內容涉及選擇低噪聲放大器的輸入匹配網絡及優化匹配參數;并通過實際測試驗證了它在天

2006-03-11 13:32:04 763

763

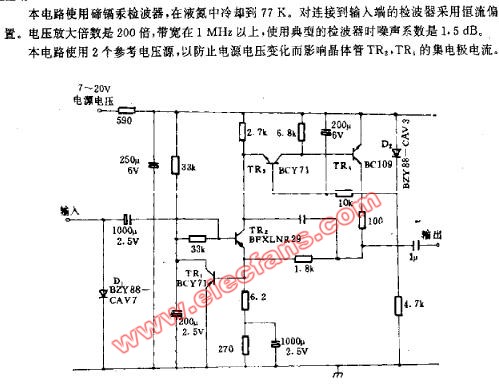

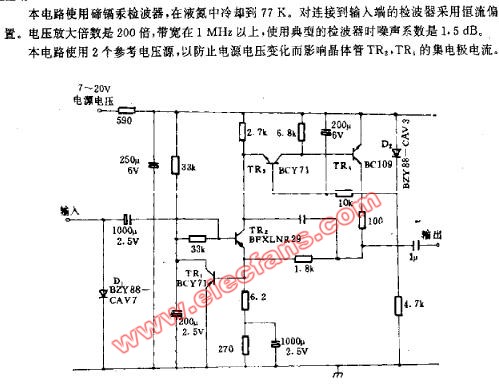

用低噪聲放大器的紅外檢波電路圖

2008-12-24 21:56:58 2561

2561

L波段低噪聲放大器的設計

低噪聲放大器(LNA)是雷達、通信、電子對抗、遙測遙控等電子系統中關鍵的微波部件,有廣泛的應用價值。由于微波系統的噪聲系數基本

2009-04-22 15:51:47 1102

1102

利用Cadence設計COMS低噪聲放大器

結合一個2.4 GHz CMOS低噪聲放大器(LNA)電路,介紹如何利用Cadence軟件系列中的IC 5.1.41完成CMOS低噪聲放大

2009-07-06 18:23:09 2737

2737

射頻低噪聲放大器的ADS設計

本文首先簡要介紹了低噪聲放大器設計的理論基礎,并以2.1-2.4Ghz 低噪聲放大器為例,詳細闡述了如何

2009-10-20 20:45:05 5814

5814

L波段低噪聲放大器的設計

引言

低噪聲放大器(LNA)是雷達、通信、電子對抗、遙測遙控等電子系統中關鍵的微波部件,有廣泛的應用價值。由于微波系統的噪

2010-02-04 10:43:15 1138

1138

低噪聲放大器,低噪聲放大器是什么意思

噪聲系數很低的放大器。

2010-03-05 10:10:44 3468

3468 3GHz CMOS低噪聲放大器優化設計

摘 要: 基于0.18 μm CMOS工藝,采用共源共柵源極負反饋結構,設計了一種3 GHz低噪聲放大器電路。從阻抗匹配及噪聲優化的角度分析了

2010-04-13 12:57:29 1485

1485

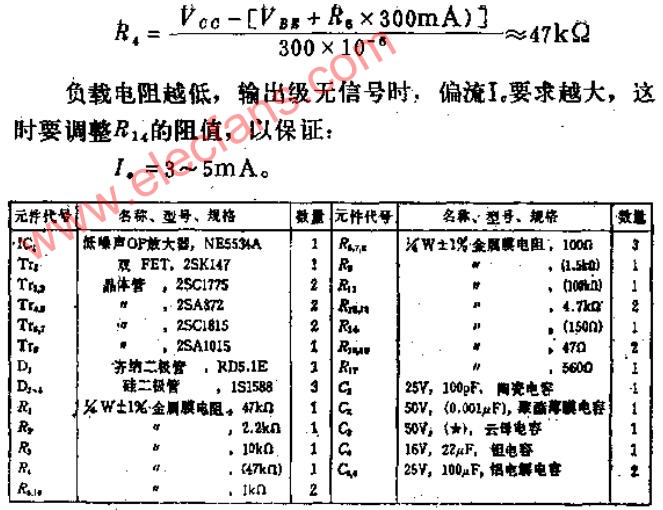

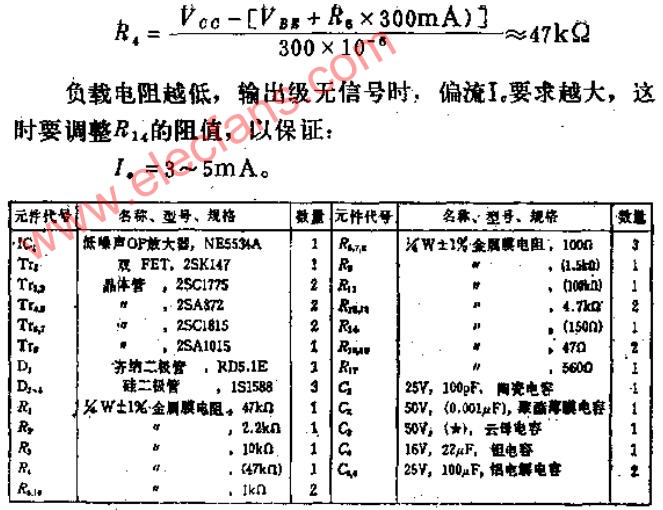

用于高阻抗電路的低失真、低噪聲放大器

電路的功能

近年來,噪聲及失真特性得到改進的低噪聲放大器品種繁多,已無須用分立元件制作了。此外,

2010-04-26 18:27:48 1827

1827

共基差分低噪聲放大器

2011-01-10 11:15:41 88

88 本文簡要的介紹了低噪聲放大器的原理,并用Agilent 公司的ADS 軟件設計、仿真了一個Ku 波段的低噪聲放大器。

2011-10-13 17:39:31 67

67 低噪聲放大器(LNA)是無線系統前端中重要器件,其性能決定了整個接收機的信噪比及整機性能。本文在介紹了低噪聲放大器的工作原理之基礎上,綜述了CMOs基毫米波低噪聲放大器的最新

2011-12-16 14:29:17 27

27 寬帶低噪聲放大器系統的研究與探測,及噪聲的提取

2015-12-10 15:24:18 1

1 低噪聲放大器(續)池保勇_清華大學微電子學研究所設計室

2016-06-27 16:22:31 0

0 低噪聲放大器_池保勇_清華大學微電子學研究所設計室

2016-06-27 16:22:31 0

0 UHF_SHF單片低噪聲放大器的設計_唐健

2017-01-07 19:00:39 2

2 一種L頻段高線性度低噪聲放大器的設計_崔偉

2017-01-07 21:45:57 0

0 用于相控陣雷達的高線性度低噪聲放大器_張小波

2017-01-08 10:18:57 1

1 本文對S波段寬帶低噪聲放大器進行了設計與實現。文中首先闡述低噪聲放大器

的相關理論,對二端口網絡的表述、傳輸線、匹配網絡等微波電路設計的一些基本理

論進行了介紹。然后給出寬帶放大器的主要技術指標

2022-07-08 16:42:53 20

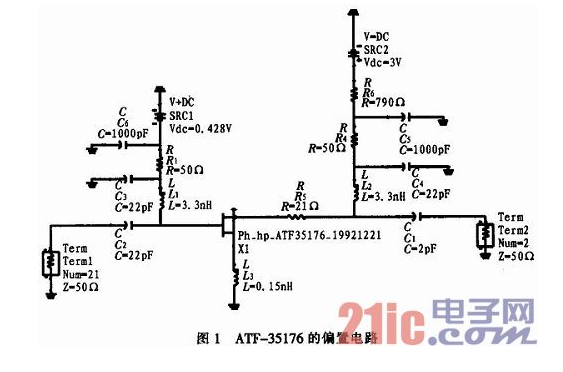

20 工程師們一般都把RF低噪聲放大器設計視為畏途。要在穩定高增益情況下獲得低噪聲系數可能極具挑戰性,甚至使人畏懼。不過,采用最新的GaAs(砷化鎵)異質結FET,可以設計出有高穩定增益和低于1dB噪聲系數的放大器。本設計就講述了一個有0.77dB噪聲系數的低噪聲放大器。

2017-11-23 17:17:34 2958

2958

在無線通信終端中,低噪聲放大器是射頻接收系統中的第一級有源電路,主要功能是放大天線從空中接收到的微弱信號,降低噪聲干擾,以供系統解調出所需的信息 數據,低噪聲放大器的設計對整個接收機來說是至關重要的。低噪聲放大器在提供增益的同時,應盡可能地減少噪聲,以及完成接收大信號不失真和好的線性度。

2017-12-10 15:19:01 1533

1533

低噪聲放大器,噪聲系數很低的放大器。一般用作各類無線電接收機的高頻或中頻前置放大器,以及高靈敏度電子探測設備的放大電路。在放大微弱信號的場合,放大器自身的噪聲對信號的干擾可能很嚴重,因此希望減小這種噪聲,以提高輸出的信噪比。

2018-02-12 09:44:01 11819

11819

低噪聲放大器(LNA)是射頻收發機的一個重要組成部分,它能有效提高接收機的接收靈敏度,進而提高收發機的傳輸距離。因此低噪聲放大器的設計是否良好,關系到整個通信系統的通信質量。

2018-02-12 10:42:50 24169

24169

在整個接收系統中,低噪聲放大器總是處于前端的位置。整個接收系統的噪聲取決于低噪聲放大器的噪聲。與普通放大器相比,低噪聲放大器一方面可以減小系統的雜波干擾,提高系統的靈敏度;另一方面放大系統的信號

2018-12-28 15:55:14 18075

18075

低噪聲放大器, 噪聲系數很低的放大器。一般用作各類無線電接收機的高頻或中頻前置放大器,以及高靈敏度電子探測設備的放大電路。在放大微弱信號的場合,放大器自身的噪聲對信號的干擾可能很嚴重,因此希望減小這種噪聲,以提高輸出的信噪比。

2019-12-20 09:10:26 21420

21420 Qorvo提供了各種具有低噪聲性能的工業領先晶體管和放大器。Qorvo低噪聲放大器提供各種產品解決方案,包括分立晶體管、集成內部匹配和片內線性化的封裝mMIC解決方案,以及用作推挽或平衡放大器配置

2020-11-03 15:34:36 658

658 低噪聲放大器簡介

2023-01-07 09:28:37 1574

1574 低噪聲放大器的設計原理是通過最小化噪聲源的貢獻,從而實現盡可能低的噪聲水平。在放大器的設計中,噪聲通常來自于電阻、晶體管和其他元件的熱噪聲以及輸入和輸出端口的噪聲耦合。為了降低噪聲水平,設計低噪聲放大器需要采取以下原則:

2023-07-25 09:44:25 968

968 低噪聲放大器工作原理詳解 低噪聲放大器是一種特定類型的放大器,其用途非常廣泛。低噪聲放大器在射頻和微波領域中非常受歡迎,因為它可以有效降低信號的噪聲,同時將信號放大到所需的水平。 本文將詳細介紹

2023-09-05 17:37:06 2508

2508 低噪聲放大器放在哪里?低噪聲放大器的作用是什么? 低噪聲放大器(low-noise amplifier,LNA)是一種電子產品,通常用于放大弱信號,使其更適合接下來的處理。它通常被用于通信系統、雷達

2023-09-05 17:49:37 958

958

![]()

![]()

電子發燒友App

電子發燒友App

評論