從工業過程控制和測量到高速通信和成像,高效的信號采集是各類應用的基礎,如此寬廣范圍的應用類別,要匹配適當的應用組件,創建一個信號鏈是至關重要的,以便以盡可能低的成本滿足性能要求,但隨著嵌入式傳感器系統(給物聯網提供采集信號)有望大發展,平衡成本與性能也就變得更加重要了。物聯網設備數量預計達上百億,每級信號鏈上節省的資源匯總起來就可以節省驚人的資源。

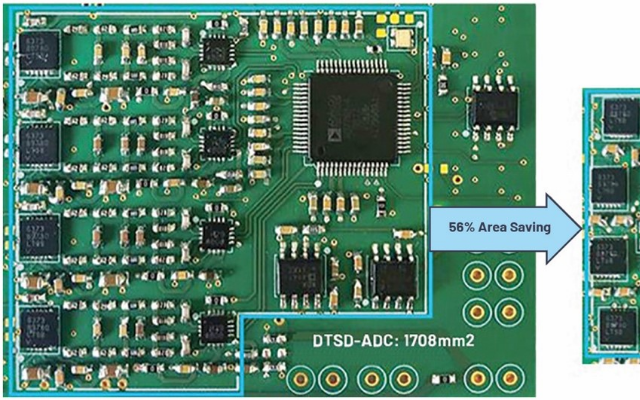

對設計者來說,要從總體出發,建立一個高效的信號鏈意味著要平衡每個獨立組件規格,在信號鏈的每個階段都要達到目標性能水平。然而有些應用要求設備盡可能高的規格(如圖1),但是設計者可能經常使用更具成本效益的組件,不過是要在達到性能和功能要求水平后創建完整的信號鏈。

圖1 :高性能模擬組件,包括模數轉換器和多路復用器,能夠使CERN(歐洲核子研究組織)的LHC(大型量子對撞機)以最可能高的性能來測量磁場區域

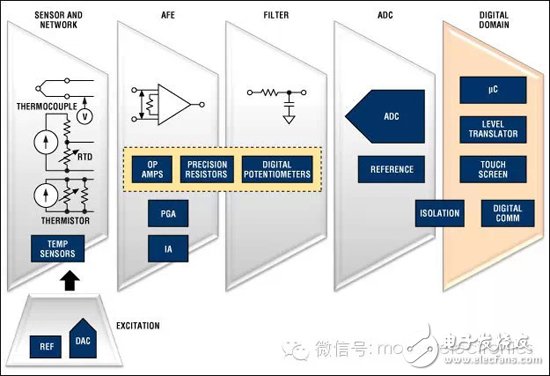

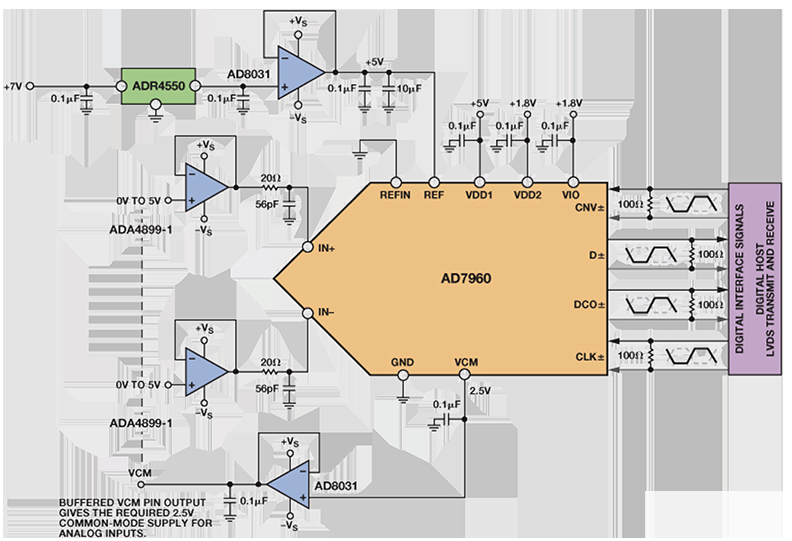

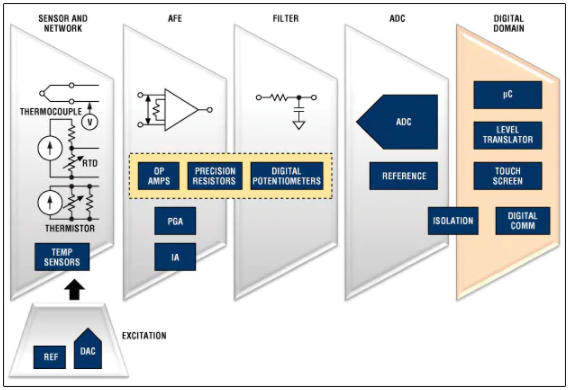

在理想情況下,信號采集電路的大多數基本形式是只包含一個組件:模數轉換器(ADC),它將傳感器或其他輸入源輸入的模擬信號轉換為數字信號。然而,對于任何實際應用,現實世界的信號不可能這么簡單,有進一步信號調節的需要,包括信號放大和濾波(如圖2)。對于使用有源傳感器和額外組件(例如數模轉換器(DAC))的應用,需要在系統前端設置精確的參考電壓和放大器,以便為傳感器提供所要求大小的勵磁電流或者電壓。

圖2:數據轉換之前,典型的模擬信號鏈需要調節來彌補小信號輸入、信號補償和其他的每個應用特有信號特征

信號調節

通常情況下,傳感器和換能器產生小振幅信號。如果沒有經過放大,這些信號只能滿足ADC全部動態范圍中一部分使用要求,由于ADC有限的分辨率和轉換器量化誤差影響,最有可能導致細節丟失。

因此,設計師通常需要一個模擬前端(AFE)放大器來增加輸入信號的幅度,以符合ADC全部動態范圍需求。同樣重要的是,輸入放大器可以確保傳感器和換能器保持正確加載,同時也可以緩沖負載瞬間變化對前端的影響,當信號采樣時,這種負載瞬變現象會出現在某些類型ADCs的輸入端。

工程師可以找到跨越較寬功能和性能范圍的放大器。盡管通常都是盡可能去找到一種可能具備最高性能的放大器,但是工程師可以通過嚴格的將放大器的規格與輸入信號的特征和要求的輸出分辨率進行比較,然后可以大大降低設計成本。例如,當信號慢速率變化并且在噪聲上保持很好時,采用帶有最快轉換速率和最低噪聲的儀表放大器(IA)則可能白白增加了成本,同樣的,具有最好線性規格的放大器可以簡單的超越ADC,提供足夠精確的結果,雖然有量化誤差,但從總體上看卻符合信號鏈的性能要求。

基于信號特征和應用要求,工程師面臨更嚴格的要求,他們可以選擇各種功能齊全的放大器,例如高精確度的IA、低噪聲的放大器(LNA)和可編程增益放大器(PGA)。不過傳統放大器提供的性能特征適合大多數應用。例如,軌到軌輸入輸出(RRIO)低噪聲放大器如亞德諾半導體公司的AD850x、美信公司的MAX963x和德州儀器公司的OPA320系列在信號采集廣泛的應用中,能夠將動態范圍擴到最大,將噪聲降到最小,是降低成本的選擇。

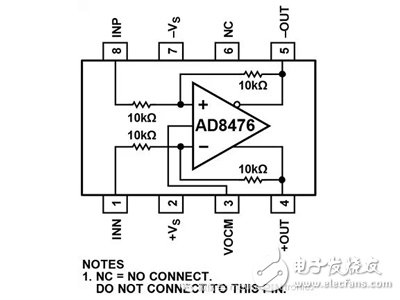

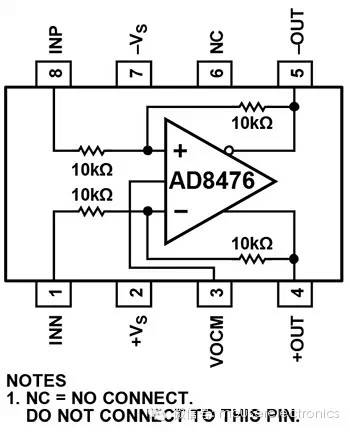

盡管傳統的單端輸入放大器對很多的應用已經足夠了,但是很多信號采集應用要求差分輸入,并且良好的共模抑制是其關鍵。例如,使用電橋傳感器的應用或者在非常嘈雜環境下工作的設計,要求對放大器的差分輸入具有更高的共模抑制特性。實際上,一些差分放大器例如ADI公司的AD8476和德州儀器公司的THS4531就是為解決差分信號調節要求而專門設計的,包括為簡化ADCs接口而設計的功能。談到ADC接口,亞德諾半導體公司的AD8476內部發現的集成激光微調電阻可以幫助在信號鏈設計中減少組件數量和成本(如圖3)。

圖3:差分放大器例如ADI的AD8476帶有集成激光微調電阻,具有按ADC接口要求調整輸出能力,幫助簡化差分輸入要求的信號鏈設計

放大器雖然擴展了輸入信號幅度,但同時也加劇了信號噪聲,限制了動態范圍。因此信號鏈通常要在信號轉換之前設置濾波級,以此來限制有用信號頻率以外的噪聲影響。

對于要求最大靈活性的應用,工程師可以使用數字電位器例如美信的MAX540x和德州儀器的TPL0102系列搭建濾波電路,使用簡單的控制邏輯或者通過上位機微控制器來驅動它們。然而對于信號特征相對穩定的應用,簡單的無源組件就能夠滿足設計濾波的要求。除了噪聲帶寬限制問題,通常信號鏈要求使用抗鋸齒濾波器,以減少采樣誤差,不過過采樣轉換方法可以降低這級電路的需求。

信號轉換

信號調節電路包括放大器和濾波器,設計的目的只有一個,就是給ADC輸入提供“干凈”的信號。因此,這些前端組件的復雜性和性能規范很大程度上取決于ADC器件的特征和要求。如果在信號鏈中只要求為變換緩慢的信號提供相對低分辨率的轉換,那么昂貴的高精度的放大器就可以省下了。

在實際情況中,最適合ADC器件的選擇——以及所需的信號調節組件選擇——反過來取決于對輸入信號特征的仔細分析和應用的整體功能要求。一個應用信號鏈的精度(和成本)需要在環境溫度下定期測量漸進的變化,這與一個“任務-關鍵過程-控制”的應用中,只打算提供及時反饋的機制是由很大不同的。事實上,ADC的選擇通常取決于信號轉換吞吐量和延遲時間的要求(延遲時間即信號采集開始到ADC輸出端有正確的響應信號)。

工程師可以從提供不同性能水準的ADC器件的結構中推斷出一些結論,對于實現高吞吐量和低延時,每種結構都提供了內在功能和限制。例如,閃爍型ADC結構通常具有最高的吞吐量和最低的延遲,但是一般只在較低分辨率情況下使用才具有成本效益。Flash ADC器件,例如亞德諾半導體公司的AD782x和德州儀器公司的TLC0820,使用并行轉換配置原理實現高速配置。它們具有的高吞吐量和最小延遲特性,這使它們成為聲音編碼應用方面的理想選擇,因為在這些應用方面顯著的延遲是不允許的。

相比之下,逐次逼近式(SAR)和(ΣΔ)型ADC能夠為較寬范圍的要求和應用提供良好的成本效益。SAR ADC已經成為大多數中等到高級分辨率應用的主要選擇。這些器件在單個周期內完成轉換,是數據采集應用方面合適的選擇,例如控制環路、電源監控和信號分析等都要求最小的延遲時間。

對于高分辨率轉換ΣΔ ADC器件一般是最低成本的選擇,因為其固有的過采樣結構。另一方面傳統的ΣΔ ADC器件因其相對緩慢的建立時間和內部數字濾波器的尖銳截止而造成了應用受限,因此,即使在一些ΣΔ ADC的性能就能勝任的情況下,設計師有時也會選擇采用SAR ADC。例如,傳統情況下在控制環路和多路復用應用方面,SAR ADCs已經成為第一選擇,因為不僅要考慮到傳統ΣΔ轉換器的性能。

在工業過程、家居應用或者汽車應用方面,反饋延時會造成控制回路的不穩定性,因此設計師有時候會選擇SAR ADC,而不是冒險使用較長延遲的ΣΔ ADC。然而,實際上在信號相對緩慢的控制應用方面,ΣΔ ADC可預見性延遲可能對控制回路的影響是微不足道的。

在多通道應用方面,設計師往往復用單個ADC器件的多個輸入通道,這樣可以節省成本、封裝和整體組件的數量。對于這些設計,基于傳統上的考慮,在下一個信號通道復用到ADC的輸入通道之前,ΣΔ ADC可能不能足夠快的完成前一次的轉換,因此工程師已經轉向采用SAR ADC。然而,在很多傳感應用方面,監測的物理現象的變化速率遠低于ΣΔ ADC的建立時間,因此很多復用通道可以選擇使用ΣΔ ADC,完全可以勝任。

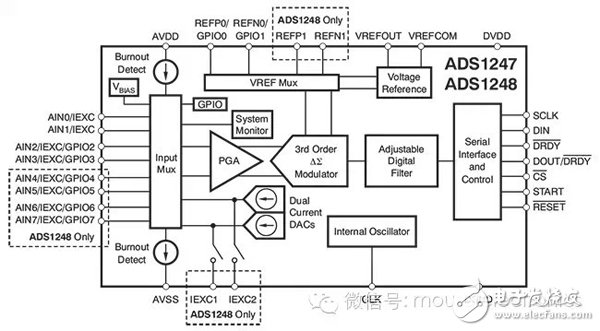

盡管傳統的ΣΔ ADC很適合那些信號變化緩慢的應用,但是先進的ΣΔ ADC,例如德州儀器公司的ADS124x,具備更加復雜的功能,很大程度上消弭了傳統上的問題(如圖4)。例如,更加復雜濾波技術會在下一代器件中使用,允許輸出零延遲。因此,24位的ΣΔ ADC,例如TIADS124x能夠提供差分復用輸入,且輸出速率可達到2ksps。

圖4:先進技術的24位ΣΔ ADCs,例如TIADS124x,已經消除了很多傳統顧慮,如在低延遲設計和復用差分輸入設計中使用ΣΔ ADC

除了要使ADC的規格符合應用要求外,設計師要考慮參考電壓的作用,進一步優化模擬信號鏈。在信號轉換過程中,除了提供穩定的參考電壓外,參考電壓的精度對于確保轉換的絕對精確是至關重要的。在一些應用中,例如電池供電設計或者能量采集設計,這些器件是尤其重要的,在這些設計中,隨著電池達到放電周期的結束或者采集能量源周期性的變弱,源電壓可能會出現波動。

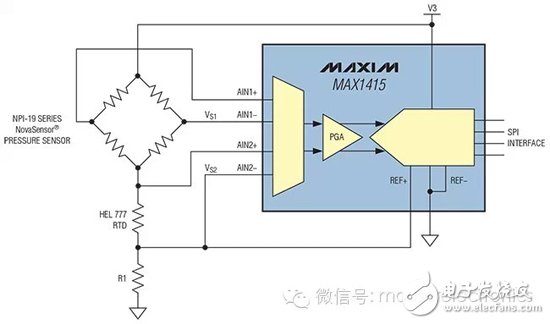

對于那些不要求如此絕對精度水平的應用,設計師可以通過使用比例轉換方法(如圖5)消除對參考電壓精度的需求。比例轉換提供的結果是與參考電壓(通常是源電壓或者勵磁電壓)的一個比值。使用這種方法,即使當源電壓波動時,ADC的輸出仍保持比例格式輸出。

圖5:ADC器件例如美信的MAX1415可以運行在比率計模式,消除了信號轉換對精確參考電壓的需要。

數字域

通常ADC提供標準的I2C或者SPI兼容串行接口,用于將模擬信號鏈的輸出與MCU(微控制單元)連接。隨著數據傳入MCU,對于更高性能要求的應用,設計者可以在軟件部分或者數字信號處理硬件部分實現傳統的濾波算法,提高信噪比。

利用靈敏的截止和陷波濾波器可以減少模擬器件的使用,例如,設計師可以選擇將復雜的濾波轉移到數字區域,而不是使用更多復雜模擬濾波組件來增加設計面積,盡管在某些特別應用里要求這么做。當然,從內存要求和MCU的性能來看,增加軟件的復雜度也加重了其自身的負擔。

結論

設計師可以發現滿足性能規范的模擬信號調節和轉換組件以應對大多數數據采集的苛刻要求。不過,對于很多的應用,信號鏈不需要采用最好的性能規格組件就能夠有效滿足應用設計要求。通過匹配ADC與轉換要求以及信號調節組件與ADC規格,工程師也可以輕松設計出滿足性能和成本要求的信號鏈。

電子發燒友App

電子發燒友App

評論