摘要:本文描述了395MHz-455MHz Doherty放大器的一種緊湊型設計方法。在本文中,90度混合電橋被用作Doherty合成器,用來替代傳統的四分之一波長線來實現Doherty合成器,隨著應用頻率的降低四分之一波長線將占用更大的布板面積,甚至有的時候無法實現。在本文中,我們設計實現了一種非常緊湊型的Doherty放大器,并將和基于相同輸入輸出匹配電路實現的平衡式AB類放大器做性能對比,最終我們設計實現了在輸出功率43dBm時,漏極效率43%,未校正鄰道泄漏比-33dBc,輸出信號的峰均比7.5dB。

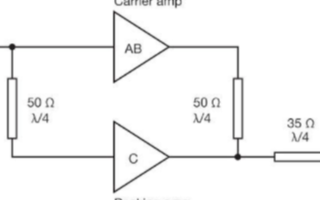

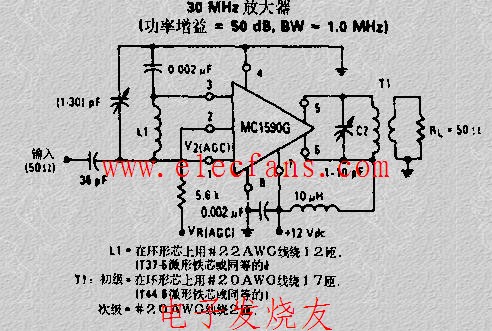

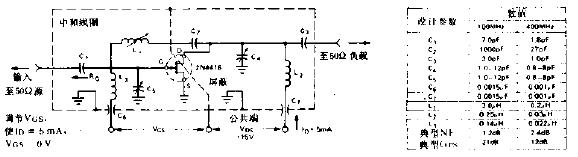

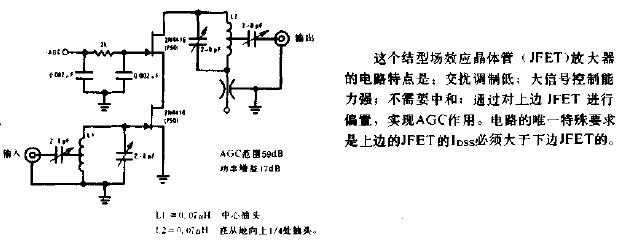

早在1936年,W.H. Doherty首次提出了一種高效節能的放大器結構[1]。由于效率高,結構簡單并且不需要復雜的外圍電路,Doherty放大器獲得了非常廣泛的應用。典型的Doherty放大器結構框圖如圖1所示,由載波放大器,峰值放大器以及Doherty合成器組成。傳統的Doherty合成器會隨著頻率的降低占用更大的PCB板面積,甚至有的時候體積龐大到無法實現布板。如果采用傳統設計方法,在RO4350B 20mil基材上設計實現395MHz-455MHz的Doherty合成器,合成器中的每條四分之一波長線長度將超過100mm,這就意味著需要更大的PCB板面積,從而增加了產品的成本。

圖1、Doherty放大器的結構框圖

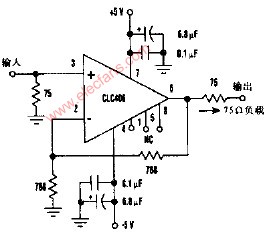

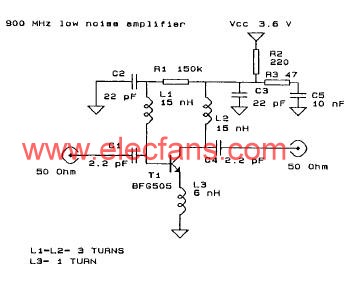

在本文中,基于90度混合電橋,我們設計并實現了一種非常緊湊型的Doherty高效放大器,其中載波放大器和峰值放大器采用飛思卡爾的功率放大器MRFE6S9045N。為了更好的理解本設計,我們將分析傳統Doherty放大器的工作原理,并將與本設計的工作原理作對比。

1、設計方法

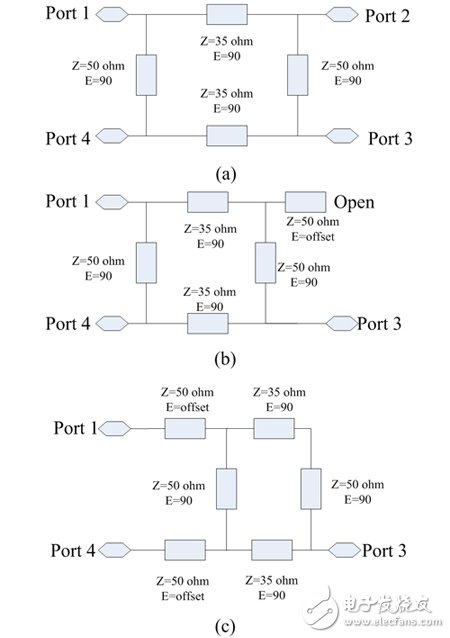

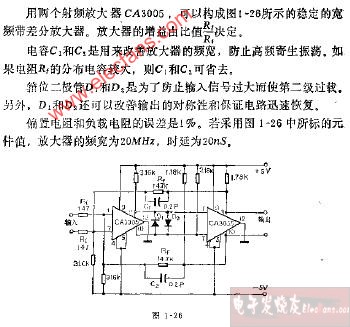

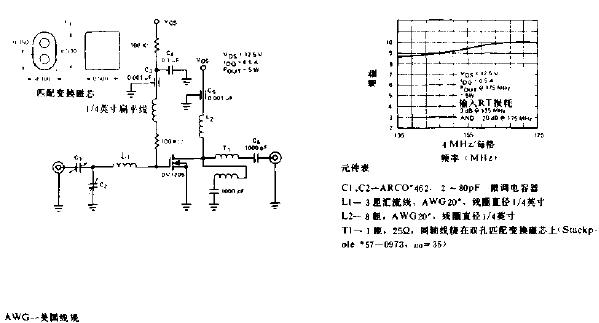

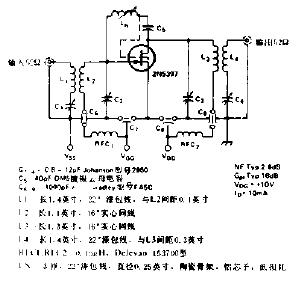

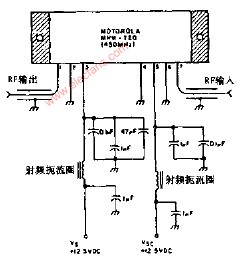

本文中的90度混合電橋采用ANAREN公司的11303-3。90度混合電橋其等效的分支線耦合器的電路圖如圖2所示。盡管90度混合電橋和分支線耦合器具有相同的功能,但是就395MHz-455MHz頻率而言,實現體積相差甚遠,11303-3器件的封裝面積為16mm*12mm,如果在RO4350B 20mil厚基材上設計395MHz-455MHz分支線耦合器,其占用的布板面積約為100mm*100mm。運用奇偶模分析方法分析分支線耦合器[2],我們可以得到圖2中(b) (c) (d)電路在電氣功能上是完全等效的,圖2中電路(e)和電路(f)在電氣功能上是完全等效的。當然,我們也可以借助安捷倫仿真軟件Advanced Design System (ADS) 進行S參數仿真,以驗證上述結論。

圖2、90度混合電橋的微帶等效電路

通過上述分析,我們可以看出90度混合電橋和傳統的Doherty合成器具有完全相同的電氣性能,對于低頻應用而言,90度混合電橋實現面積更小。

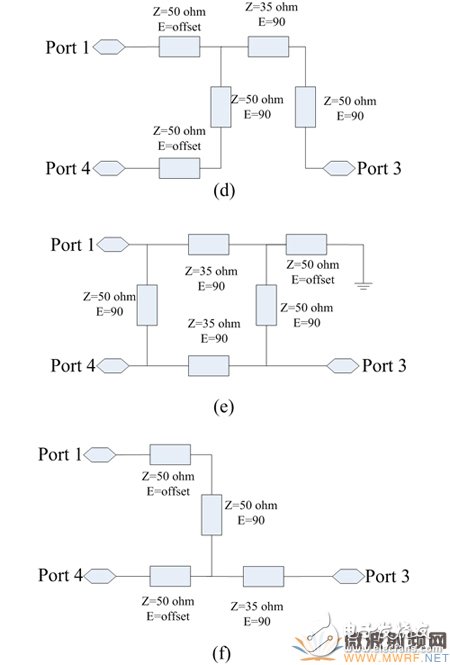

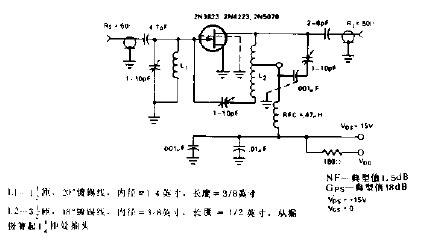

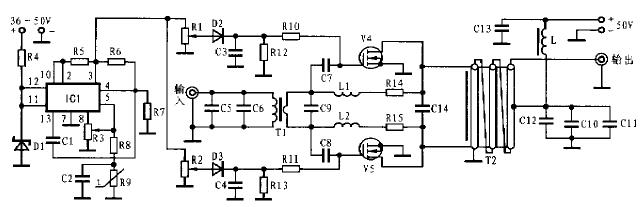

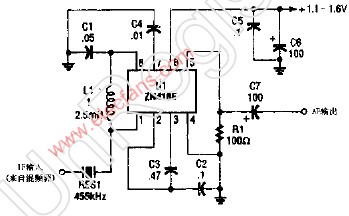

Doherty放大器的基本工作原理是有源負載牽引[3]。正如圖1所示,Doherty放大器由載波放大器和峰值放大器組成,Doherty合成器將在載波放大器和峰值放大器連接在一起。為了能夠更好的理解Doherty放大器的工作原理,本文用安捷倫的Agilent’s Advanced Design System (ADS)軟件搭建了仿真工程如圖3所示。在仿真工程中,我們將把功率放大管抽象成理想的壓控電流源,在歸一化輸入電壓前提下,通過圖3中的VAR expression控件設置 載波放大器和峰值放大器電流,載波放大器和峰值放大器電流和輸入電壓的關系曲線如圖4左上子圖所示。

圖3、Doherty 放大器工作原理仿真工程

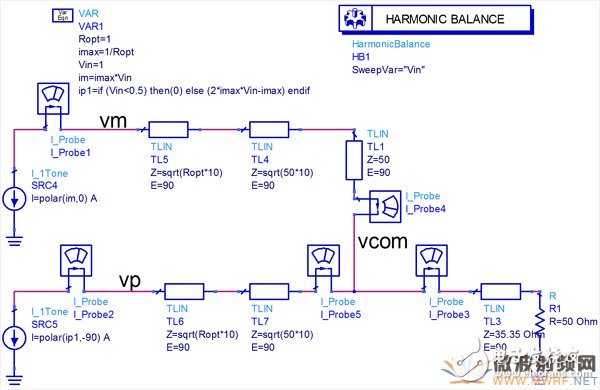

當歸一化輸入電壓為(0~0.5)時,輸出匹配電路呈獻給載波放大器的阻抗是所對應的傳統AB類放大器阻抗的兩倍,如圖4左下子圖所示。由于輸出匹配電路阻抗提高到傳統AB類放大器的兩倍,所以當歸一化輸入電壓達到0.5時,載波放大器將達到傳統放大器臨界飽和點,因此效率也將達到臨界飽和點的效率,比如B類放大器的臨界飽和效率為Pi/4。在這個輸入電壓范圍內載波放大器和基于同樣器件設計的傳統AB類放大器相比,因為載波放大器輸出匹配電路所呈現的阻抗是傳統AB類放大器的兩倍,所以理論上載波放大器的增益將要高出AB類放大器3dB,輸出1dB壓縮點降低3dB。

當歸一化輸入電壓為(0.5~1)時,峰值放大器開始工作導通,峰值放大器輸出的電流在Doherty有源負載牽引技術中扮演重要作用。如圖4右上子圖所示,在歸一化輸入電壓為(0.5~1)范圍內載波放大器始終保持在臨界飽和狀態,所以載波放大器的效率始終保持在臨界飽和效率,載波放大器輸出匹配電路所呈現的阻抗也將由2Zopt調制到Zopt,相對應的峰值放大器輸出匹配電路所呈現的阻抗將有無窮大調制到Zopt,如圖4左下子圖所示。此時歸一化的峰值放大器的漏極電壓也將由0.5調制到1,因此峰值放大器也將由臨界飽和效率的50%,逐步提高到臨界飽和效率,最終Doherty放大器的合成效率如圖4右下子圖所示。同樣我們也可以通過ADS仿真驗證,理想Doherty放大器的輸入輸出功率是完全線性的[4][5]。

圖4、Doherty放大器ADS仿真結果

2、設計實現

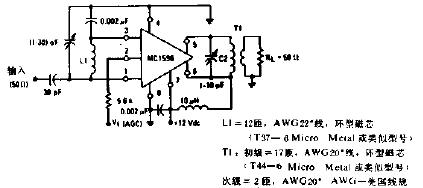

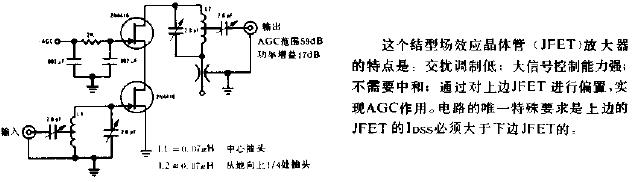

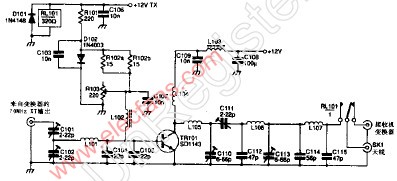

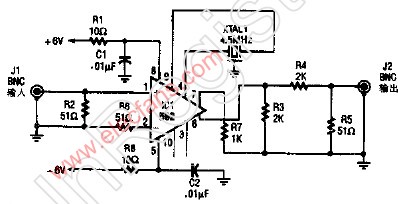

本文采用MRFE6S9045N設計實現了緊湊型395MHz-455MHz Doherty放大器,為了對比Doherty放大器的性能,本文也同樣制作調試了基于同樣器件同樣匹配電路的AB類,平衡式放大器,設計實現的Doherty放大器如圖5所示。在輸入端口,我們采用90度混合電橋將功放輸入信號一分為二,分別送給載波放大器和峰值放大器,載波放大器偏置在AB類,靜態偏執電流為350mA。峰值放大器偏置在C類,柵極偏置電壓為1.5V,載波放大器和峰值放大器放大后的信號將通過另一個90度混合電橋合成后輸出。如圖5所示,輸出90度混合電橋的隔離端口的一段50歐姆的開口線,其作用是作為載波放大器和峰值放大器共同的相位補償線。

圖5、緊湊型Doherty放大器實物圖

3、測試結果

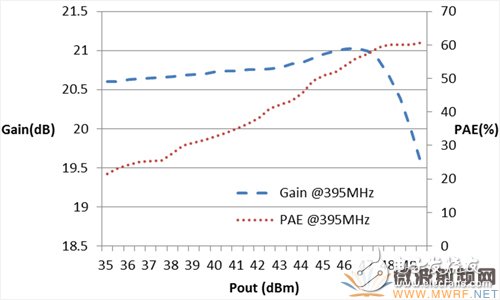

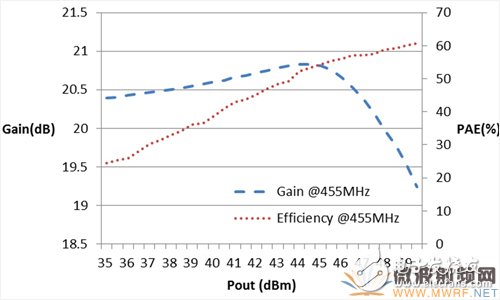

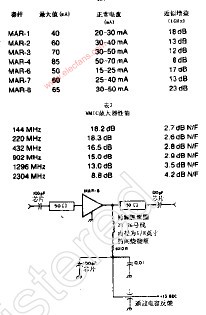

在本文中,將用連續波單音信號測試所設計的功率放大器性能。選取395MHz和455MHz測試結果羅列如下。

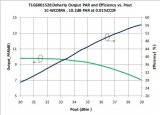

在395MHz處,測試所得的增益和效率對輸出功率的曲線如圖6所示,測試數據顯示在輸出功率為43dBm時,功放漏極效率為43%, 飽和輸出功率高于49dBm。

圖6、395MHz 增益和效率測試數據

在455MHz處,測試所得的增益和效率對輸出功率的曲線如圖7所示,測試數據顯示在輸出功率為43dBm時,功放漏極效率為45%, 飽和輸出功率高于49dBm。

圖7、455MHz 增益和效率測試數據

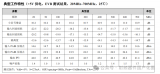

典型的單載波W-CDMA信號測試性能如表1所示,測試所用輸入信號的峰均比為9.9dB(在互補累計分布函數概率為0.01%條件下測得)功放輸出平均功率為43dBm。

表1、Doherty 放大器單載波W-CDMA信號測試性能

FrequencyGain(dB)PAE (%)ACLR(dBc)PAR(dB)

395 MHz20.59743.30%-33.6dBc7.5

425MHz22.943.80%-34.4dBc7.62

455MHz20.41545.20%-33.5dBc7.58

為了對比所設計的Doherty放大器和傳統AB類放大器性能,本文設計調試了一個基于同樣器件和同樣匹配電路的平衡式AB類放大器,典型的單載波W-CDMA信號測試性能如表2所示,測試所用輸入信號的峰均比為9.9dB(在互補累計分布函數概率為0.01%條件下測得),功放輸出平均功率為43dBm,從表2中我們可以看出,對于同樣的43dBm的輸出功率,Doherty放大器呈現了更高的效率,平衡式放大器呈現了更好的線性。

表2、AB類的平衡式放大器W-CDMA信號測試性能

FrequencyGain(dB)PAE (%)ACLR(dBc)PAR(dB)

395 MHz21.218.60%-43.5dBc8.52

425MHz23.521%-40.3dBc8.31

455MHz24.41520.80%-41.8dBc8.41

4、結論

本文提出了一種395MHz到455MHz緊湊型Doherty放大器的設計方法, 采用了飛思卡爾公司的LDMOS器件MRFE6S9045N。設計實現了在單載波W-CDMA輸出平均功率為43dBm時,漏極效率高于43%,相對于傳統的Doherty放大器設計方法,本文呈現了一種緊湊型Doherty設計方法,節約了PCB板的面積,并且達到了很好的性能。本文也證明了在低頻段設計應用上,90度混合電橋可以用來作為Doherty的合成器。

電子發燒友App

電子發燒友App

評論