LDMOS (Lateral Diffused MetalOxide Semiconductor Transistor,橫向擴散金屬氧化物半導體)以其高功率增益、高效率及低成本等優點,被廣泛應用于移動通信基站、雷達、導航等領域。射頻大功率 LDMOS由于具有P、L波段以上的工作頻率和高的性價比,已成為3G手機基站射頻放大器的首選器件。

隨著IC集成度的提高及器件特征尺寸的減小,柵氧化層厚度越來越薄,其柵的耐壓能力顯著下降,擊穿電壓是射頻LDMOS器件可靠性的一個重要參數,它不僅決定了其輸出功率,還決定了器件的耐壓能力,因此必須要采取措施以提高器件的擊穿電壓。

本文將在基本LDMOS的基礎上,通過器件結構的改進來提高LDMOS的抗擊穿能力。

1、LDMOS耐壓特性

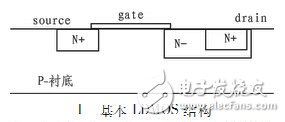

如圖1所示,LDMOS最主要的結構特點是采用雙擴散技術,在同一窗口進行磷擴散,溝道長度由兩種擴散的橫向結深決定。LDMOS中產生的擊穿形式有柵絕緣層擊穿和漏源擊穿。

LDMOS高壓器件是多子導電器件,由于漂移區將漏區與溝道隔離,Vds絕大部分降落在漂移區上,基本上沒有溝道調制,所以當Vds增大時,輸出電阻不下降。并且柵電極和漏區不重迭,從而提高了漏源擊穿電壓。

影響LDMOS耐壓性能的因素很多,本文將從埋層、漂移區摻雜濃度、襯底摻雜濃度3方面進行分析各參數對其耐壓性能的影響。

1.1、影響LDMOS耐壓性能的主要參數

1.1.1、埋層

在 P襯底用離子注入法注入N型埋藏層(NBL),一方面,NBL與P襯底以及N+摻雜區形成寄生三極管,當有電壓加在LDMOS器件的漏極時,可利用寄生三 極管形成電流放電路徑,并且添加的N型埋層可以增加雜質的摻雜濃度,減小其內部電阻,從而更利于釋放電流。另一方面,NBL可以降低溝道附近的等位線曲率 提高擊穿電壓,其電中性作用使漂移區的優化濃度提高,導通電阻降低,改善了漏極擊穿特性。

1.1.2、漂移區摻雜濃度

漂移區 是LDMOS和MOS器件結構的主要差異之一,也正是由于低摻雜漂移區的存在使LDMOS擊穿電壓比傳統MOS高很多。漂移區長度、深度和濃度對擊穿電壓 的影響很大,一般說來,漂移區長度越長,LDMOS擊穿電壓越高,但是當漂移區長度增加到一定值時,其擊穿電壓隨著漂移區長度的變化逐漸變緩。擊穿電壓隨 漂移區濃度的增大先增大后減小。

1.1.3、襯底摻雜濃度

襯底摻雜濃度的大小對擊穿電壓影響較大。由于pn結一邊或者兩邊摻 雜濃度較低時,雪崩擊穿是pn結主要的擊穿機制,LDMOS的一次擊穿是主要集中在漏極處的雪崩擊穿,在一定范嗣內,襯底濃度越小,與漏極形成的反向PN 結的勢壘寬度越寬,碰撞倍增次數越多,雪崩擊穿也就越容易發生,擊穿電壓就越低。

1.2、提高LDMOS擊穿電壓現有的技術

目前,利用器件結構上的改進,進而提高LDMOS擊穿電壓的方法主要有:RESURF技術、漂移區變摻雜、加電阻場極板、內場限環等技術。

RESURF 技術:其基本原理是選擇適當的漂移區摻雜濃度和厚度,控制漂移區表面的二維電場,使擊穿發生在體內從而達到高擊穿電壓的目的。通過降低漂移區摻雜,在溝道 和漂移區結的電場尚未達到臨界電場之前,利用P-襯底和N-漂移區的pn結將漂移區耗盡,增大了耗盡區邊界的曲率半徑,從而提高了擊穿電壓。

漂移區變摻雜:通過表面摻雜濃度的階梯變化,在漂移區中部引入新的電場峰值,提高漂移區中部電場,且較高的摻雜位于表面,降低導通電阻的同時改善表面電場分布。

加電阻場極板:在漂移區上方形成電阻場板,電阻場板產生均勻分布的垂直電場施加于漂移區中,與水平電場交疊,使漂移區電場分布也均勻化,降低了電場強度,從而提高了擊穿電壓。

內場限環技術:在N-漂移區中插入P型區域,在漂移區內形成內場限壞時,內場限壞耗盡區的電場與表面電場方向相反,增大了柵場耗盡區的有效曲率半徑,從而提高了器件耐壓。

總體而言,RESURF技術無需增加額外的工藝,但須對襯底摻雜濃度、N阱摻雜濃度和N阱的厚度以及區域進行控制,精確度要求較高。漂移區變摻雜技術和加電 阻場極板工藝步驟較復雜,不利于電路的集成。內場限環技術需受到漂移區寬度及深度的限制,一般適用于漂移區較深,且濃度較高的LDMOS器件中。

2、LDMOS抗擊穿設計

LDMOS器件的擊穿電壓主要集中在漏極處,此處的電場較集中,電場越集中,器件越容易擊穿,因此,為了提高器件的擊穿電壓,可減弱其電場強度。

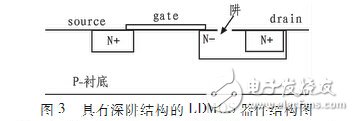

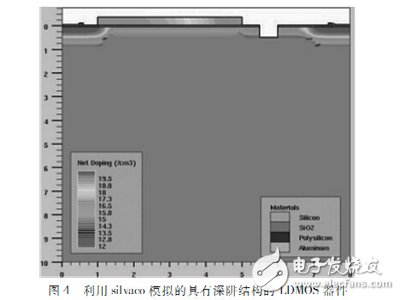

LDMOS器件工作時,柵極的末端存在一個峰值電場,為了減小其表面電場強度,可在漂移區引入阱結構。圖3為具有阱結構的LDMOS結構圖,圖4為其相應的silvaco模擬仿真圖。

阱結構可以是一個無任何介質的深槽,深槽的作用主要是從物理結構上改變器件的電場強度分布,減弱柵極末端的電場集中。為了進一步改善器件的電場分布,可在阱 結構中填充低介電常數的絕緣介質。阱中低介電常數的介質一方面截斷器件的曲面結,消除電場集中:另一方面抑制了平面工藝的橫向擴散,可承受更高的峰值電場。

Si、SiC、SiO2、GaAs的相對介電常數分別為11.6、10.0、3.9、13.1。相對而言,SiO2具有低的介電常數,適合填充在LDMOS的深阱結構中。

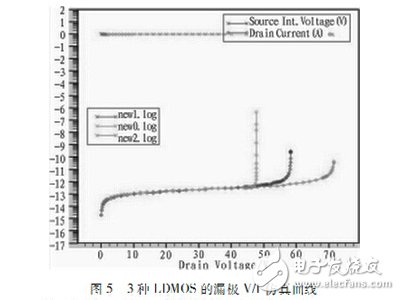

保持LDMOS器件摻雜濃度、柵長、阱寬等參數不變,如圖5所示。new0.Log、new1.Log、new2.Log分別代表基本LDMOS、有深槽的 LDMOS以及完全填入SiO2的深阱的LDMOS漏極V/I仿真曲線。本文采用的深阱結構其阱寬和阱深都為0.5μm,從圖5中可以看出,由于深槽的作 用,LDMOS擊穿電壓提高了10 V,當進一步在深槽中填入SiO2時,其擊穿電壓可再次提高12 V。通過對比分析可以說明,采用阱結構技術可以明顯提高器件的抗擊穿能力。

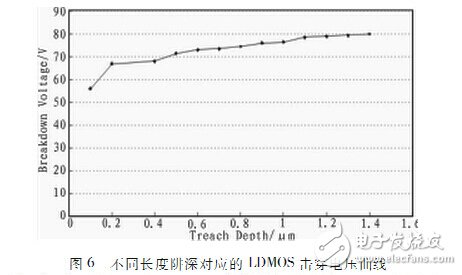

通 過進一步仿真實驗發現,器件耐壓性能與阱寬及阱深的尺寸有關。保持漂移區長度不變,阱寬為固定值0.5μm,圖6為不同長度阱深對應的器件擊穿電壓曲線。 從圖6中可以看出,隨著阱深的加大,器件的抗擊穿能力加強,這是由于阱深越大,耗盡區俞難越過阱區,且體硅中承受的最大電場的范圍越大,LDMOS的耐壓 就越高。

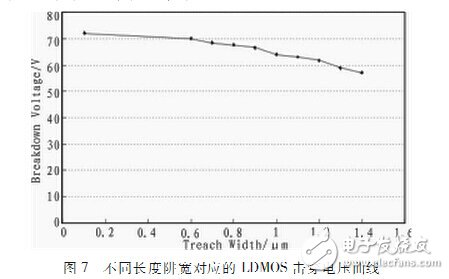

同樣,保持漂移區長度不變,阱深為固定值0.5μm,圖7為不同長度阱寬對應的器件擊穿電壓曲線。擊穿電壓隨著阱寬的增加反而減小,這是因為阱寬的增加使得漂移區長度減小,總的耐壓也就隨之減小。

選擇適當的阱寬及阱深,在阱中摻雜低介電常數介質,如SiO2,通過優化器件的結構參數可以得到擊穿電壓的最大值。

采用此深阱結構最大的優點是工藝方法簡單有效,并且可利用深阱的寬度和深度以及深阱中填入何種介質或填入介質的多少來控制LDMOS的擊穿電壓,在實際工藝操作過程中可控性強。

3、結論

LDMOS 擊穿電壓易發生在柵極末端,器件襯底上添加埋層可以降低溝道附近的等位線曲率從而提高其擊穿電壓。漂移區將漏區與溝道隔離,抑制了器件的溝道調制,在一定 摻雜范圍內,漂移區濃度越低,擊穿電壓越高。襯底濃度越低,雪崩擊穿越容易發生,擊穿電壓就越低。本文采用的深阱結構主要為了減小柵極末端的電場強度,消 除電場集中,進而提高其抗擊穿能力。

另外,由于柵極界面存在電荷,柵末端的峰值電場隨柵長的增加而增加,為了抑制峰值電場集中導致器件的擊穿,柵長不宜較長。漂移區長度可適當加大,阱深可盡量取較大值,結合器件摻雜濃度,最終可使射頻LDMOS的抗擊穿能力達到最優。

文 中設計的LDMOS器件主要是在耐壓特性上做了改進,相對于RESURF技術、漂移區變摻雜、加電阻場極板、內場限環等技術而言,具有工藝簡單,可控性強 的優點。其較高的抗擊穿能力可適用于射頻集成電路,如移動通信基站。當然,若將此器件應用于基站,還需要考慮射頻LDMOS的其它電學特性,使器件的各個 參數達到作為基站功率放大器的要求。

電子發燒友App

電子發燒友App

評論