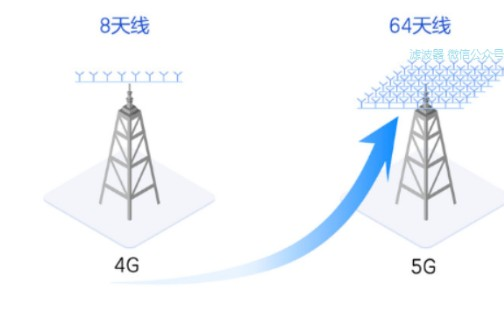

第五代(5G)無線存取網(wǎng)絡是為了滿足對容量不斷成長的需求,以及2020年之后新的使用情境與應用。5G新無線電技術(NR)針對每位用戶高達10Gbps的最高數(shù)據(jù)傳輸率,提供增強型行動寬帶(eMBB)服務,與第四代無線網(wǎng)絡相比,約提升100倍。大規(guī)模MIMO,或稱大規(guī)模數(shù)組天線(Massive MIMO)是達成效能提升的關鍵技術,尤其適合于6GHz以下不常使用的時分雙工(TDD)頻段,如Band 40(2.3GHz)、Band 41(2.5GHz)、Band 42(3.5GHz)、Band 43(3.7GHz),以及尚未授權的新興頻段。

大規(guī)模MIMO系統(tǒng)能支持動態(tài)數(shù)字波束成形(Dynamic Digital Beamforming)來執(zhí)行每位用戶的波束成形,理論上能提供每位用戶完整的基地臺容量;在其它情況下,上述容量則依據(jù)時間與頻率由用戶共享。客戶端無須改變現(xiàn)有設備,即可受惠于具備大規(guī)模MIMO功能的行動通訊基地臺。大規(guī)模MIMO的前景相當誘人,讓許多業(yè)者等不及5G NR標準完成,就已考慮部署在4G設備上,不過,這些好處也帶來一系列的挑戰(zhàn)。由于落實大規(guī)模MIMO無線技術系統(tǒng)會使復雜性提升數(shù)倍,隨之而來的較大系統(tǒng)體積、更高的功耗與成本需求便成為一大障礙。若想克服這些挑戰(zhàn),必須將無線技術中的模擬訊號鏈與數(shù)字前端(DFE)裝置進行整合,并大幅提升訊號處理運算能力。

大規(guī)模MIMO與波束成形

? ? ? ?波束成形并非全新概念,在行動通訊市場中,它已被用為主動式天線系統(tǒng)(AAS),其在無線電中運用靜態(tài)波束成形,來達到系統(tǒng)成本與復雜性的平衡。主動式天線系統(tǒng)適用于訊號涵蓋范圍有限的網(wǎng)絡,但今日壅塞的網(wǎng)絡需要動態(tài)數(shù)字波束成形,以獲得頻譜效率提升所帶來的所有益處。具備完整數(shù)字波束成形的大規(guī)模MIMO,除了頻率與時間之外還增加了空間維度,可以大幅提升頻譜效率。數(shù)組增益與多波束正交性產(chǎn)生的訊噪比(SNR)改善,意謂著同樣的時間與頻率分配,可由多名用戶重復使用(圖1)。

圖1 主動式天線系統(tǒng)與大規(guī)模MIMO

基地臺分解與功能性分割

? ? ? ?由于大規(guī)模MIMO架構相關的復雜性,基地臺必須分解以支持新的功能性分割,來管理系統(tǒng)內的連接帶寬。例如,在100MHz 64T64R天線數(shù)組系統(tǒng)中,假定基頻與無線電功能各利用一個組件來運行,此時基頻與無線電功能間的帶寬則為230Gbps。事實上,系統(tǒng)往往使用多個組件來運行8T8R或16T16R數(shù)組DFE無線電功能模塊,因此使得系統(tǒng)內連接帶寬的需求多出一倍以上。圖2說明大規(guī)模MIMO無線電系統(tǒng)的概念圖。

圖2 大規(guī)模MIMO的概念架構

數(shù)字無線電處理模塊透過整合的模擬數(shù)字轉換器(ADC)與數(shù)字模擬轉換器(DAC),來執(zhí)行8T8R或16T16R的DFE功能。為了降低系統(tǒng)空間體積、功耗與成本,必須去除接合數(shù)字與模擬領域所需的JESD204B連接鏈路。波束成形裝置為無線電技術帶來第一層(Layer 1;L1)基頻功能性,能大幅降低更高層基頻功能的連接帶寬需求,而這些更高層基頻功能,現(xiàn)階段在行動邊緣運算上存在虛擬化的潛在可能。整合、靈活性,與更高的運算能力是三大關鍵需求,以落實大規(guī)模MIMO系統(tǒng)的優(yōu)化,并有助于相關的波束成形與DFE算法的演進,進而不斷改善效能、成本與功耗。

成本/功耗/體積提升 主動訊號鏈商轉挑戰(zhàn)大

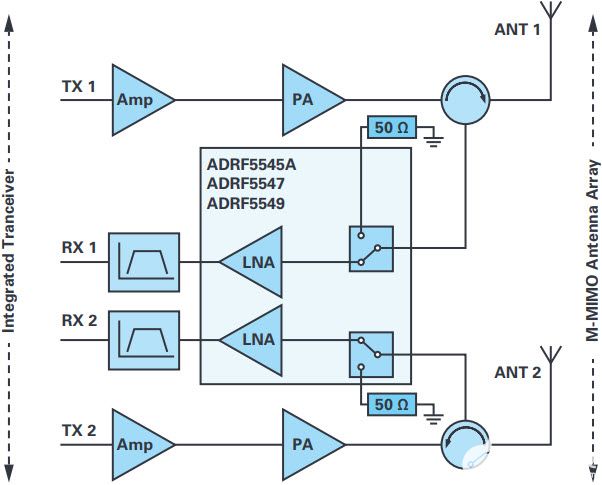

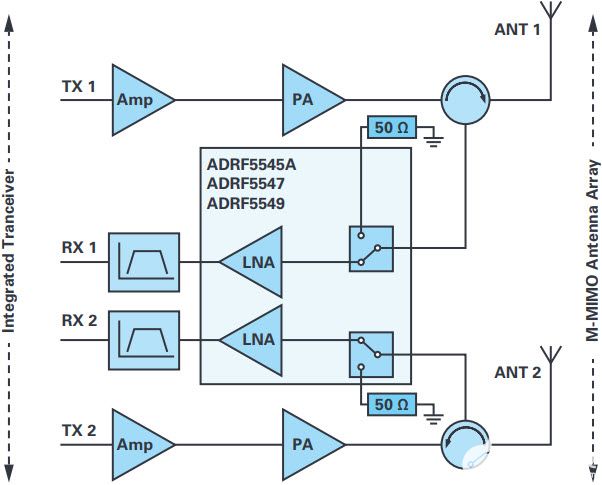

? ? ? ?落實5G NR大規(guī)模MIMO需在無線電裝置中有大量的主動訊號鏈,來連接數(shù)組中的每支天線,或天線數(shù)組子集。傳統(tǒng)上這些主動訊號鏈會包含數(shù)據(jù)轉換器、濾波器、混波器、功率放大器與低噪訊放大器,進而導致系統(tǒng)的耗電、體積與成本顯著增加,因此大規(guī)模MIMO系統(tǒng)中的大量主動訊號鏈會造成系統(tǒng)耗電與空間體積增加,較不易成為可商轉應用的系統(tǒng)。讓資料在射頻前端(RFFE)與DFE間移動的相關成本,不管是對軟件、硬件或系統(tǒng)層級上,都是5G領域必須解決的主要挑戰(zhàn)。

為了解決此一挑戰(zhàn),目前已有相關業(yè)者,如賽靈思(Xilinx)把直接無線射頻取樣數(shù)據(jù)轉換器(Direct RF-sampling Data Converters),整合至專為無線電應用設計與布署的16奈米FinFET多重處理系統(tǒng)芯片(MPSoC)系列產(chǎn)品中,來取代電路板上多種ADC、DAC,以及其它許多RF組件。此新推出的SoC組件系列稱為「可完全編程射頻系統(tǒng)單芯片」(All Programmable RFSoC),其單片整合無線射頻取樣數(shù)據(jù)轉換器技術,為無線電系統(tǒng)提供硬件與軟件皆可完全編程的寬帶寬平臺。此一架構采用Arm處理子系統(tǒng),并結合FPGA可編程邏輯技術,來展現(xiàn)12位4GSPS無線射頻取樣ADC,與14位6.4GSPS直接無線射頻DAC,以及優(yōu)化的數(shù)字訊號降頻與升頻處理的技術。

利用整合無線射頻取樣數(shù)據(jù)轉換器技術,將射頻帶入數(shù)字領域,不但可以克服功耗、空間體積與成本的劣勢,同時也可達成寬帶寬與多頻段系統(tǒng)。現(xiàn)有無線電系統(tǒng)中的模擬射頻,通常在設計上用來產(chǎn)生緩解且離散的數(shù)據(jù)轉換器規(guī)格。此外,離散數(shù)據(jù)轉換器與模擬射頻組件,采用較為舊型的處理節(jié)點,且通常針對窄帶寬進行優(yōu)化。這導致模擬射頻解決方案用在寬帶寬MIMO與大規(guī)模MIMO無線電系統(tǒng)時,無論體積大小、耗電與成本都相當昂貴。因此整合高速數(shù)據(jù)轉換器、6.4GSPS直接無線射頻DAC與4GSPS無線射頻取樣ADC,可以讓數(shù)字射頻更具彈性、耗用更低電量同時帶寬更寬,因此相當適合建構小體積、低耗電與低成本的MIMO與大規(guī)模MIMO系統(tǒng)。

借力16奈米FinFET 數(shù)位射頻運行一路順暢

? ? ? ?高速射頻組件的單片整合,受惠于16奈米FinFET制程的優(yōu)異模擬晶體管特性。晶體管通電時阻力相當?shù)停梢詧?zhí)行具高精度的寬帶寬無線射頻取樣訊號切換。如此一來,就可以整合具成本與功耗效益的高速比較器、放大器、頻率電路與具有優(yōu)異特性的數(shù)字輔助模擬校準邏輯。相較于65奈米(通常用于模擬射頻組件),在16奈米FinFET上進行數(shù)字操作帶來十倍以上的體積縮減,及耗電量也減少四倍。

整合至RFSoC的數(shù)字射頻資源,包含6.4GSPS DAC與4GSPS ADC的多頻道、已整合的低相位噪訊鎖相回路(PLL),以及完整的復頻混波器(Complex Mixer),且每個DAC與ADC各有48位的數(shù)值控制震蕩器(NCO)。射頻數(shù)據(jù)轉換器數(shù)組具有1倍、2倍、4倍與8倍的內插(Interpolation)與取樣降頻濾波器(Decimation Filter),并能運行靈活的FPGA結構接口。此外,直接無線射頻DAC模塊,則運行正交調變修正(QMC)與Sin x/x(Sinc)修正濾波器(圖3)。

圖3 RFSoC數(shù)字射頻資源

在RFSoC上落實大規(guī)模MIMO系統(tǒng)

? ? ? ?圖4顯示運用RFSoC組件運行的典型大規(guī)模MIMO無線電。RFSoC具有100G強固級以太網(wǎng)絡MAC/PCS的33Gbps收發(fā)器,其可依前傳接口特點的不同(25G CPRI或ECPRI協(xié)議),來運用其中的RS-FEC。部份的L1功能,例如逆/正向快速傅立葉變換(iFFT/FFT),以及相關聯(lián)的實體隨機存取頻道處理,則可移至無線電部份,可在無線電與基頻單元之間減少50%的帶寬(及成本與功耗上的節(jié)省)。RFSoC組件能提供豐富的高效能、低功率數(shù)字信號處理器(DSP)資源,以進行包括數(shù)字升頻器(Digital up Conversion)、峰波因子抑制(Crest Factor Reduction, CFR)、數(shù)位預失真(Digital Pre-distortion, DPD)、被動互調(Passive Intermodulation)修正,等化與降頻等DFE技術。通過在傳送路徑使用適當?shù)膬炔鍨V波器,及接收路徑使用適當?shù)娜咏殿l濾波器,可以在高頻率頻率、且不受FPGA結構頻率影響下,運行RF-DAC及RF-ADC,以利更佳的頻率規(guī)劃。在仔細的頻率規(guī)劃下,可利用整合的射頻訊號鏈的寬帶寬,同步支持多個頻段,諸如FDD大規(guī)模MIMO使用的Band 1與Band 3,以及TDD大規(guī)模MIMO使用的Band 38、40、41與Band 42和43等。RFSoC擁有四核ARM Cortex-A53多核心處理器,運作頻率最高可達1.5GHz,另外還有雙核實時Arm Cortex-R5多核心處理器,運作頻率達533MHz。對于運算預失真系數(shù)與進行系統(tǒng)管控、射頻校準與一般運作及維修來說,這是重要的運算資源。可編程邏輯線路加上系統(tǒng)芯片運算,可用來支持開源應用程序編程接口(API),讓無線電系統(tǒng)碰到軟件定義網(wǎng)絡的未來環(huán)境時,也能滿足無線電系統(tǒng)依據(jù)客戶需求進行動態(tài)配置的要求。機器學習算法可在此結構上有效運行,并自動管理數(shù)量愈來愈多的零碎頻譜頻段、頻譜分享及托管虛擬行動網(wǎng)絡電信公司(MVNO)。

圖4 在減少部分L1功能下,于RFSoC上運行大規(guī)模MIMO無線電

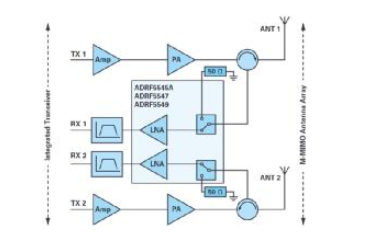

為順利進行整合,F(xiàn)PGA廠商提供針對CFR與DPD的打造的DFE IP,以及針對4G、LTE-Pro與5G應用的DFE子系統(tǒng)參考設計與DFE展示套件。為了呈現(xiàn)RFSoC上的系統(tǒng)效能,可將采用ZU28DR組件的RFSoC特征基板連接至射頻前端卡,采用兩個傳送與兩個多任務接收路徑,來支持功率放大器回饋(如圖5所示)。依此進行基板設定,并將單一功率放大器連接至一對DAC/ADC后,就完成采用FPAG廠商現(xiàn)有16奈米MPSoC組件之DFE參考設計(2.1版本)的快速端口,并運用RFSoC與16奈米SoC在結構上的共通性,讓更復雜設計時還能重復使用。在此設計中,CFR IP運作的取樣頻率達245.76MSps(針對TM3.1a訊號在7.5分貝峰值對平均功率比(PRPR)的情況下,達成3%的誤差向量幅度(EVM)),而DPD IP的運作取樣頻率則達到491.52MSps(DAC/ADC在第二奈奎斯特區(qū),利用3.93216 GSps頻率與8倍內插/整數(shù)倍降低取樣率(Decimation)運作),而2c LTE20+1c LTE20合成訊號則處于160MHz的瞬時帶寬內。放大器輸出為45dBm或32瓦。在運行DPD后,達到的加速運算平臺(ACP,如圖5右側顯示)為54.91dBc,而Upper ACP則為-55.14dBc,容限充足且符合LTE頻譜輻射模板(SEM)所需。

圖5 針對2c LTE20+1c LTE設置的RFSoC,瞬間帶寬達160MHz

落實5G NR、LTE-Advanced Pro MIMO及大規(guī)模MIMO無線電系統(tǒng)設計,須要面對多元、多頻段需求,同時還須減少系統(tǒng)體積、功耗與成本問題。而解決這些挑戰(zhàn)的方式有許多種,而其中已有看到業(yè)界采用單芯片整合「高速、寬帶寬無線射頻取樣數(shù)據(jù)轉換器」與「結構縝密的數(shù)字內訊號處理及運算資源」,來解決大規(guī)模MIMO的挑戰(zhàn)。

電子發(fā)燒友App

電子發(fā)燒友App

評論